一种用于ESD的新型双雪崩NMOS器件

一种用于esd的新型双雪崩nmos器件

技术领域

1.本发明属于电子科学与技术领域,涉及集成电路高压输出引脚的静电释放(electro static discharge,esd)防护与抗误触发技术,具体涉及一种用于esd的新型双雪崩nmos器件。

背景技术:

2.esd在芯片的制造、封装、测试和使用过程中无处不在,积累的静电荷以几安培或几十安培的电流在纳秒到微秒的时间里释放,瞬间功率高达几十或者上百瓦,对电路系统内的芯片的摧毁强度极大。据统计35%以上的芯片失效是由于esd损伤引起的。所以芯片或系统的设计中,静电保护模块的设计直接关系到电路系统的功能稳定性,以及系统可靠性,对电子产品极为重要。

3.高压集成电路的高压输出引脚同样需要通过严格的esd测试,为了防止误触发,一般方法是对引脚进行无回扫保护。然而无回扫保护的一个缺点是功耗过大,esd器件的保护能力不够,因此若需要其拥有合格的esd保护能力必须增大面积。为了既能防止误触发,又能提高esd器件的保护能力,亟需一种新的esd器件。

技术实现要素:

4.有鉴于此,本发明的目的在于提供一种用于esd的新型双雪崩nmos器件,通过具有高维持电压vh和高的维持电流的i-v特性,回避了高压输出电流的负载线,通过增加维持电流ih的方法避免闩锁。该器件在esd泄放时无需维持高vh值,从而降低功耗,增加esd能力。

5.为达到上述目的,本发明提供如下技术方案:

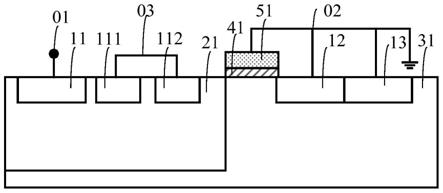

6.一种用于esd的新型双雪崩nmos器件,包括:漏极nsd注入11、源极nsd注入12、bulk电位psd注入13、nw漂移区21、pbody区31、栅氧化层41、多晶硅栅极51、阳极金属线01、阴极金属线02、第一浮空nsd区111、第二浮空nsd区112和短路金属线03;

7.其位置关系为:漏极nsd注入11位于nw漂移区21内部表面;pbody区31位于nw漂移区21右侧并与其相切;源极nsd注入12与bulk电位psd注入13左右相邻,且均位于pbody区31的内部表面;栅氧化层41位于pbody区31的沟道位置上方,即位于源极nsd注入12和nw漂移区21中间区域的表面上方;多晶硅栅极51位于栅氧化层41上方;阳极金属线01连接漏极nsd注入11;阴极金属线02分别连接多晶硅栅极51、源极nsd注入12和bulk电位psd注入13并接地;所述第一浮空nsd区111与第二浮空nsd区112位于漏极nsd注入11右侧同时也在nw漂移区21内部表面;所述短路金属线03将第一浮空nsd区111和第二浮空nsd区112短接。

8.工作原理:当高压esd脉冲出现在漏极上端时,会引起nmos体内的npn结构导通。npn导通后,由于电阻分布的原因,大部分电子流会从第二浮空nsd区112流出,通过短路金属线03再流入第一浮空nsd区111,然后流出漏极。此时由于高电子密度,第二浮空nsd区112右侧将会形成雪崩电场,形成第一次回扫。当电流继续增加到一定值后,体内npn开启,此时由于体内npn具有更低的导通电阻,表面npn路径被旁路,第二浮空nsd区112右侧的雪崩电

场会因电子密度的降低而消失,而该电场消失的过程就是第二次回扫过程,该状态能够使得nmos形成独特的双回扫特性曲线,该特性十分适用于高压端口的esd防护。

9.可选的,该器件还能将金属线03、第一浮空nsd区111和第二浮空nsd区112在nw漂移区21中重复制作n(n》1)次,形成n组由金属线03、第一浮空nsd区111和第二浮空nsd区112构成的短路结构,其他结构保持不变。

10.本发明的有益效果在于:本发明器件通过利用一个短路浮空nsd结构巧妙地利用了器件的克尔克效应形成了双回扫特性。该特性有利于降低器件esd瞬态功耗,同时很好的避免了高压输出端口的误触发问题,是esd端口防护器件设计的一种可选方案。

11.本发明的其他优点、目标和特征在某种程度上将在随后的说明书中进行阐述,并且在某种程度上,基于对下文的考察研究对本领域技术人员而言将是显而易见的,或者可以从本发明的实践中得到教导。本发明的目标和其他优点可以通过下面的说明书来实现和获得。

附图说明

12.为了使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明作优选的详细描述,其中:

13.图1为实施例一的新型双雪崩nmos器件结构示意图;

14.图2为实施例一的新型双雪崩nmos器件第一次回扫状态图;

15.图3为实施例一的新型双雪崩nmos器件第二次回扫状态图;

16.图4为实施例二的新型双雪崩nmos器件结构示意图;

17.附图标记:01-阳极金属线,02-阴极金属线,03-短路金属线,11-漏极nsd注入,12-源极nsd注入,13-bulk电位psd注入,21-nw漂移区,31-pbody区,41-栅氧化层,51-多晶硅栅极,111-第一浮空nsd区,112-第二浮空nsd区。

具体实施方式

18.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需要说明的是,以下实施例中所提供的图示仅以示意方式说明本发明的基本构想,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

19.其中,附图仅用于示例性说明,表示的仅是示意图,而非实物图,不能理解为对本发明的限制;为了更好地说明本发明的实施例,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;对本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的。

20.本发明实施例的附图中相同或相似的标号对应相同或相似的部件;在本发明的描述中,需要理解的是,若有术语“上”、“下”、“左”、“右”、“前”、“后”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此附图中描述

位置关系的用语仅用于示例性说明,不能理解为对本发明的限制,对于本领域的普通技术人员而言,可以根据具体情况理解上述术语的具体含义。

21.实施例一:

22.本实施例提供一种用于esd的新型双雪崩nmos器件,如图1所示,包括:漏极nsd注入11、源极nsd注入12、bulk电位psd注入13、nw漂移区21、pbody区31、栅氧化层41、多晶硅栅极51、阳极金属线01、阴极金属线02、第一浮空nsd区111、第二浮空nsd区112和短路金属线03。

23.其位置关系为:漏极nsd注入11位于n漂移区21内部表面,pbody区31位于nw漂移区21右侧并与其相切,源极nsd注入12,bulk电位psd注入13位于pbody区31的内部表面,栅氧化层41位于pbody区31的沟道位置上方(即源极nsd注入12和nw漂移区21中间区域的表面上方),多晶硅栅极51位于栅氧化层41上方,阳极金属线01连接漏极nsd注入11,阴极金属线02分别连接多晶硅栅极51,源极nsd注入12和bulk电位psd注入13并接地,第一浮空nsd区111与第二浮空nsd区112位于漏极nsd注入11右侧同时也在nw漂移区21内部表面,短路金属线03将第一浮空nsd区111和第二浮空nsd区112短接。

24.其工作原理如图2和图3所示,当远大于vdd的esd电压出现在漏极上后,nw/pbody结会被率先击穿。击穿电流会逐渐开启内部寄生npn三极管(nw/pbosy/nsd结构)。当npn三极管发射极(nmos源极)发射电子后,该电子会被nw漂移区表面的nsd所聚集(由于nsd浓度更高电阻更小),通过图2中的线路到达漏极。电子聚集效应会在nsd与nw漂移区右侧产生一个高雪崩电场e2,同时nmos漏极也会产生传统的高雪崩电场e1。此时该器件处于第一次回扫状态。

25.当电流继续增大,如图3所示,nw漂移区被完全电导调制。此时当nw漂移区电阻急剧减小至小于图2电流路径的电阻后,新的导电路径将会开启,即图3中的路径。该路径会将图2的电子聚集效应消除,从而使器件退出双雪崩状态,回到传统器件的单雪崩状态,如图3所示的e3。因此经过以上过程,该nmos器件实现了目标的低vh和高ih的双回扫特性。

26.实施例二:将实施例一中的金属线03、第一浮空nsd区111和第二浮空nsd区112在nw漂移区21中重复制作n次(n》1),形成n组由金属线03-第一浮空nsd区111-第二浮空nsd区112构成的短路结构,其他结构保持不变,如图4所示。

27.综上,本发明器件通过引入两个相互短接的浮空nsd区域,对器件第一次触发后的电子电流进行主动聚集,其结果是除了在原本的漏极nsd和n漂移区交界处形成雪崩电场外在另一个浮空nsd侧也会形成一个雪崩区域,这样该器件在进行放电时就是一个双雪崩状态,该状态能够使得nmos形成独特的双回扫特性曲线,该特性十分适用于高压端口的esd防护。

28.最后说明的是,以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本技术方案的宗旨和范围,其均应涵盖在本发明的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1