忆阻器及其制备方法、应用与流程

1.本发明涉及微电子的技术领域,尤其是涉及一种忆阻器及其制备方法、应用。

背景技术:

2.近年来,阻变随机存储器(rram)是新兴存储器技术中最有希望的候选者之一,它具有阻变响应速度快、每单位能量消耗扩展性高、耐久性以及稳定性高的优点,引起了硅微电子学行业的广泛关注;此外,“金属/固体电解质/金属”这种简单的双端子结构也被用于3d可堆叠的高密度数据存储架构中。以上的诸多特点使得rram在众多领域中表现出潜在的应用价值,例如内存中的计算、数据存储以及内存逻辑单元。

3.目前,tio

x

、wo

x

、nio、cuo、ta2o5以及zro等的金属氧化物材料已经作为固体电解质而被广泛应用于阻变存储器的研究之中。对于这些器件,阻变(rs)依赖于氧化还原过程和离子迁移过程在固体电解质内引起电子限域导电丝或功能界面的横向均匀性,但是仍然存在着许多有待于解决的问题,例如高温过程、高功耗、可靠性问题以及稳定性问题。因此,为使rram在高级电子系统中得以出色的应用,仍然需要进一步优化材料和器件的结构。

4.二氧化硅(sio2)主要作为栅介质材料和线路工艺后端(beol)的钝化层,在rram中的应用也有所研究。sio2材料具有高的晶片级均匀性,而且与传统cmos技术的3d结构也表现出较佳的一致性。氧空位的移动或电流-电压(i-v)特性的缺陷会引起强烈的滞后现象;而基于金属氧化物的rram会存在可靠性的相关问题,主要在于耐久性和稳定性。人们已经探索了各种策略来提高器件的阻变性能。此外,随着时间的推移,二氧化硅会在环境湿度的影响下表现出退化现象,而会损害基于二氧化硅的rram器件的开关行为。

5.目前,有许多关于基于sio2的rram器件的阻变机理的解释,而在众多的解释当中,由于具有低工作电压和高开比的缘故,活性金属电极例如铜所形成的高导电细丝(cfs)机制被深入研究。活性电极的活性原子在电场作用下表现出的导电细丝的形成/溶解是丝状rram器件产生阻变行为的关键因素。然而,聚集的金属原子的浓度很大地影响了这种器件的阻变性能,高导电细丝会诱发不同的阻变行为,而这种多变性影响了rram器件的可靠性和均匀性,例如由活性金属原子所形成的低浓度导电细丝可以引起阈值开关行为而非阻变行为。因此,为了获得可靠的阻变行为,必须调整活性金属原子的浓度,使纳米尺度的导电细丝通过电介质层实现可控的生长。

6.由于rram与传统的cmos制造流程相兼容,因此其备受关注。然而为了满足工业标准,这种类型器件的稳定性和可靠性仍是一个巨大的挑战,例如在长期的反复开关操作之后,器件极易发生故障,难以保持高的耐受性、稳定性和均一性。

7.有鉴于此,特提出本发明。

技术实现要素:

8.本发明的目的之一在于提供一种忆阻器,具有优异的耐久性能、出色的开关性能以及较佳的稳定性能。

9.本发明的目的之二在于提供一种忆阻器的制备方法,工艺简单、高效且稳定。

10.本发明的目的之三在于一种忆阻器在数据存储、内存计算以及神经形态技术中的应用。

11.为了实现本发明的上述目的,特采用以下技术方案:

12.第一方面,本发明提供了一种忆阻器,包括依次排列的底电极、电介质层、阻变层以及顶电极;

13.所述电介质层为非晶二氧化硅;

14.所述阻变层为铜掺杂钛酸锶。

15.进一步的,所述底电极包括si。

16.进一步的,所述底电极的厚度为100nm。

17.进一步的,所述电介质层的厚度为70nm。

18.进一步的,所述阻变层的厚度为70nm。

19.进一步的,所述顶电极为导电金属、导电金属合金或导电金属化合物;

20.进一步优选的,所述导电金属包括铜。

21.进一步的,所述顶电极的厚度为50nm。

22.第二方面,本发明提供了一种忆阻器的制备方法,包括以下步骤:

23.在底电极上依次沉积生长电介质层、阻变层以及顶电极,得到所述忆阻器;

24.所述电介质层为非晶二氧化硅;

25.所述阻变层为铜掺杂钛酸锶。

26.进一步的,所述制备方法包括以下步骤:

27.在底电极上,利用射频磁控溅射首先沉积非晶二氧化硅,再采用共溅射技术在非晶二氧化硅上沉积铜掺杂钛酸锶,之后利用直流溅射在铜掺杂钛酸锶上沉积顶电极,得到所述忆阻器。

28.第三方面,本发明提供了一种忆阻器在数据存储、内存计算以及神经形态技术中的应用。

29.与现有技术相比,本发明至少具有如下有益效果:

30.本发明提供的忆阻器,包括依次排列的底电极、电介质层、阻变层以及顶电极;其中的电介质层为非晶二氧化硅(sio2),阻变层为铜掺杂钛酸锶(csto)。本发明以非晶二氧化硅(sio2)作为电介质层,该电介质层与硅衬底非常相符,而且具有高温稳定性;本发明在顶电极与二氧化硅薄膜(sio2)之间引入铜掺杂钛酸锶(csto),能够确保铜原子浓度从而实现导电细丝的生成,通过调整csto层中的铜原子数量去优化二氧化硅层中铜导电细丝的形成/断裂,进而实现阻变行为的产生;同时,与直接在二氧化硅薄膜上沉积铜电极相比,本发明csto/sio2结构的忆阻器能够展现出更为可靠的性能;此外,铜掺杂钛酸锶层可与二氧化硅层形成牢固的多层结构,从而保护二氧化硅层不受周围空气的影响,使得忆阻器能够稳定可靠地工作20天左右而没有任何退化。综上所述,本发明csto/sio2结构的忆阻器不仅可以提升sio2的可靠性,提高耐久性和增强开关性能,还能够有效地调节sio2层中的铜原子含量。另外,本发明的忆阻器能够展现出数字类型的阻变行为和模型类型的阻变行为,展现出兴奋性突触后电流(epsc)、双脉冲易化(ppf)、短期记忆(stm)到长期记忆(ltm)的转变,以及易化/抑制等突触特性。

31.本发明提供的忆阻器的制备方法,工艺简单、高效且稳定。

32.本发明提供的忆阻器在数据存储、内存计算以及神经形态技术中的应用,具有很大的应用潜力。

附图说明

33.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

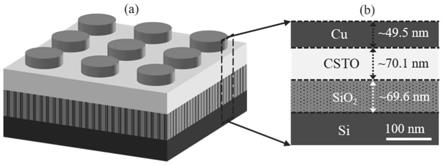

34.图1为本发明试验例1提供的忆阻器(cu/csto/sio2/si)的结构示意图;

35.图2为本发明试验例2提供的忆阻器(cu/csto/sio2/si)的电流-电压特性图;

36.图3为本发明试验例3提供的忆阻器(cu/csto/sio2/si)的稳定性表征图;

37.图4为本发明试验例4提供的忆阻器(cu/csto/sio2/si)的开关特性图。

具体实施方式

38.下面将结合实施例对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

39.根据本发明的第一个方面,提供了一种忆阻器,包括依次排列的底电极、电介质层、阻变层以及顶电极;

40.其中,电介质层为非晶二氧化硅;阻变层为铜掺杂钛酸锶。

41.本发明的忆阻器,以非晶二氧化硅(sio2)作为电介质层,与硅衬底非常相符,而且具有高温稳定性;本发明在非晶二氧化硅层上堆积铜掺杂钛酸锶层(csto),能够实现导电细丝的可控生长,具体的,在顶电极与电介质层二氧化硅薄膜之间引入铜掺杂钛酸锶以确保铜原子浓度,从而实现导电细丝的生成,通过调整csto层中的铜原子数量去优化二氧化硅层中铜导电细丝的形成/断裂,进而实现阻变行为的产生;与直接在二氧化硅薄膜上沉积铜电极相比,本发明csto/sio2结构的忆阻器能够展现出更为可靠的性能;此外,铜掺杂钛酸锶层可与二氧化硅层形成牢固的多层结构,从而保护二氧化硅层不受周围空气的影响,使得忆阻器能够稳定可靠地工作20天而没有任何退化。

42.同时,本发明的忆阻器能够展现出数字类型的阻变行为和模型类型的阻变行为,展现出兴奋性突触后电流(epsc)、双脉冲易化(ppf)、短期记忆(stm)到长期记忆(ltm)的转变,以及易化/抑制等突触特性。

43.综上所述,本发明csto/sio2双层膜结构的忆阻器具有优异的耐久性和开关性能,可以在背景环境中稳定工作;同时,本发明的忆阻器具有数字和模拟两种类型的阻变形式;本发明的忆阻器能够实现基本的突触功能,包括增强/抑制。

44.在本发明中,忆阻器的底电极包括但不限于si,底电极的厚度为100nm;忆阻器的电介质层的厚度为70nm;忆阻器的阻变层的厚度为70nm;忆阻器的顶电极为导电金属、导电金属合金或导电金属化合物,其中,导电金属包括但不限于铜;忆阻器的顶电极的厚度为

50nm。

45.本发明所限定的底电极种类及其厚度、电介质层的厚度、阻变层的厚度以及顶电极种类及其厚度,能够互相配合,取得协同效果,提高忆阻器器件的耐受性、稳定性以及均一性。

46.根据本发明的第二个方面,提供了一种忆阻器的制备方法,包括以下步骤:

47.在底电极上依次沉积生长电介质层、阻变层以及顶电极,得到忆阻器;

48.其中,电介质层为非晶二氧化硅;阻变层为铜掺杂钛酸锶。

49.在本发明中,首先沉积非晶二氧化硅薄膜,然后利用共溅射方式在非晶二氧化硅膜表面沉积csto薄膜,通过调节sto靶材磁道上cu片去调节csto薄膜中的cu原子含量,csto薄膜中的cu原子是形成导电细丝的关键之处。

50.在一种优选的实施方式中,本发明忆阻器的制备方法包括以下步骤:

51.在底电极上,利用射频磁控溅射首先沉积非晶二氧化硅(电介质层),再采用共溅射技术在非晶二氧化硅上沉积铜掺杂钛酸锶(阻变层),之后利用直流溅射在铜掺杂钛酸锶上沉积顶电极,得到忆阻器。

52.本发明提供的忆阻器的制备方法,工艺简单、高效且稳定。

53.在本发明中,可以使用物理气相沉积方法沉积非晶二氧化硅层,从而实现低温制备纳米级rram器件。

54.一种忆阻器典型的制备方法,包括以下步骤:

55.s1:将商用的si清洗干净并吹干,利用射频磁控溅射在si上沉积厚度为70nm的二氧化硅薄膜;

56.s2:采用共溅射技术将铜片放在钛酸锶靶材上,并在步骤s1沉积的二氧化硅薄膜上镀厚度为70nm的铜掺杂钛酸锶(csto)层;

57.s3:用直流溅射的方法制备厚度为50nm的cu层,利用掩膜辅助沉积,制备直径为100微米的圆形cu电极层;

58.在上述的步骤中,二氧化硅和csto薄膜的溅射功率保持在90w,cu电极的溅射功率为100w;工作气体为氩气,在整个沉积过程中腔内压强始终保持10mtorr。

59.本发明提供的忆阻器的制备方法,工艺简单、高效且稳定,实现在低温下制备纳米级rram器件。

60.根据本发明的第三个方面,提供了一种忆阻器在数据存储、内存计算以及神经形态技术中的应用,具有很大的应用潜力。

61.本发明cu/csto/sio2/si器件所组成的10

×

10阵列,能够模拟简单的学习和遗忘行为,证明了基于本发明csto/sio2的忆阻器在神经形态学中应用的可行性。

62.下面通过实施例对本发明作进一步说明。如无特别说明,实施例中的材料为根据现有方法制备而得,或直接从市场上购得。

63.实施例1

64.一种忆阻器(结构cu/csto/sio2/si),包括依次排列的底电极、电介质层、阻变层以及顶电极;

65.其中,底电极为si,厚度为100nm;电介质层为非晶二氧化硅(sio2),厚度为70nm;阻变层为铜掺杂钛酸锶(csto),厚度为70nm;顶电极为cu层,厚度为50nm。

66.实施例2

67.本实施例为实施例1的忆阻器的制备方法,包括以下步骤:

68.(a)将商用的si依次用丙酮、乙醇以及去离子水超声清洗10分钟左右,除去表面污染物,之后再用压缩氮气吹干,得到清洗干净的si,再利用射频磁控溅射在si上沉积厚度为70nm的二氧化硅薄膜;

69.(b)采用共溅射技术将铜片放在钛酸锶靶材上,并在步骤(a)沉积的二氧化硅薄膜上镀厚度为70nm的铜掺杂钛酸锶(csto)层;

70.(c)用直流溅射的方法制备厚度为50nm的cu层,利用掩膜辅助沉积,再去除掩膜后完成铜电极沉积,得到cu电极层,为直径为100微米的圆形片;

71.在上述步骤(a)、以及(b)中,二氧化硅和铜掺杂钛酸锶(csto)薄膜的溅射功率保持在90w左右,cu电极的溅射功率为100w左右,工作气体为氩气,在整个沉积过程中腔内压强始终保持10mtorr。

72.对比例1

73.本对比例的忆阻器与实施例1忆阻器的不同之处在于,本对比例的忆阻器不包括铜掺杂钛酸锶(csto)层,本对比例的忆阻器结构为cu/sio2/si,si为底电极,sio2为电介质层,cu层为顶电极。

74.本对比例采用与实施例1相同的方式制备了cu/sio2/si结构的器件。

75.试验例1

76.对实施例1得到的cu/csto/sio2/si器件的结构和化学成份进行表征:

77.实施例1的cu/csto/sio2/si器件的结构和化学成份表征的结果见图1,其中(a)为器件的堆垛结构视图,(b)为器件的截面tme图;

78.测试方法:对实施例1的cu/csto/sio2/si器件,运用透射电子显微镜分析各层薄膜的厚度(顶电极铜膜厚50nm,csto层和sio2层的厚度都是70nm),利用聚焦离子束(fei quanta 3d feg dual-beam)的方式展现cu/csto/sio2/si结构的截面图,利用x射线光谱表征了器件各层薄膜的化学成分,见图1中的(a),以及(b)。

79.试验例2

80.对实施例1得到的cu/csto/sio2/si器件进行电学测试(以下的电学特性测试均是在室温下用keithley 2636b电源所连接的探测系统完成的,顶电极cu加正向或者负向偏压,si作为底电极接地)。

81.实施例1得到的cu/csto/sio2/si器件的电流-电压特性测试,结果见图2,其中(a)为cu/csto/sio2/si器件的i-v特性图,(b)为器件在5000次扫描偏压下的耐受性,低阻态和高阻态的阻值均是在0.3v的读取电压下测试的数据,(c)为器件在读取电压为0.5v时的高、低阻态的持续时间,(d)为100个器件测得的高、低阻值的累积概率分布。

82.测试方法:在顶电极te上施加0~5v的扫描电压,限制电流icc=10ma,在初始阶段,器件电压逐渐上升,当电压到达2.8v时,器件的电流达到icc,这意味着器件已经完成高阻态(hrs)向低阻态(lrs)的转变,即“set”过程;

83.偏置电压从5v到0v后,器件仍然处于低阻态,当偏压从0v到-0.4v时,器件会从低阻态转变为高阻态,即“reset”过程;

84.上述结果表示实施例1的cu/csto/sio2/si器件具有双极阻变行为,见图2中的a;

85.为了验证器件在循环测试状态下的耐受性而进行了一系列的循环测试,测试结果显示该器件在5

×

103次循环测试后,仍然保持着稳定的状态,而且其低阻态与高阻态的比率仍然保持在102不变,见图2中的b;使用dc电压扫描模式执行一系列的set和reset过程以测试器件的数据保持能力,在set与reset过程之后,再立即用0.5v的常压测试器件的阻值状态,结果显示该器件可以实现104秒这么久的保持状态且无任何衰退迹象,见图2中的c;同时,随机选择100个器件去测试器件与器件之间的电阻态变化,即lrs和hrs,以证实器件的均匀性;所有器件展现出的高、低阻态值都是在-4.5v

→

0v

→

5v扫描电压下测试得到的;所有经过测试的器件的电阻态都展现出了密集分布的特性,见图2中的d,证明了cu/csto/sio2/si器件具有较佳的均匀性。

86.试验例3

87.实施例1得到的cu/csto/sio2/si器件在常规环境下的稳定性表征,见图3,其中的(a)为背景环境中cu/csto/sio2/si器件的i-v特性,b为cu/csto/sio2/si器件在室温背景环境中的长达20天的稳定性,在这20天内均对器件的高、低阻态值进行测试。

88.化学稳定性是rram器件在实际应用中的一个重要因素,二氧化硅层对水分很敏感,为了阻止外界水分对器件的影响,本发明引入了铜掺杂钛酸锶(csto),既能够控制着器件的阻变行为,也可以作为钝化层去保护二氧化硅层;

89.测试方法:为了验证铜掺杂钛酸锶(csto)层的作用,本试验例在空气中测试了具有csto层和不具有csto层的基于二氧化硅的rram器件的i-v特性,即实施例1的忆阻器和对比例1的忆阻器,实施例1忆阻器的i-v特性和稳定性见图3中的(a)和(b),可以看出,具有csto层的器件(实施例1的忆阻器)的lhs/hrs比值在0.5v的读取电压下的阻变行为可以保持长达20天而无衰变,而没有csto层的器件(对比例1的忆阻器)在十天之后的阻变行为就逐渐发生退化,由此可见,本发明的csto层确实能够提升基于二氧化硅材料的rram器件的稳定性。

90.试验例4

91.脉冲模式下实施例1的器件的开关特性分析:

92.如图4中的c所示,在一系列脉冲作用下cu/csto/sio2/si器件的耐受性测试:设置脉宽为3毫秒,脉冲值为+2.8v的电脉冲去使器件实现set过程;设置脉宽为3毫秒,脉冲值为-2.8v的电脉冲去使器件实现reset过程;在每个脉冲作用3毫秒之后,立马用0.8v的读取电压记录器件相应的阻态值大小。结果显示在100次脉冲刺激模式下,器件展现出稳定的高、低阻态数值,表明器件具有均一的开关行为;

93.在一系列脉冲作用下,设置读取电压为0.8v,cu/csto/sio2/si器件的保持特性测试:使用单个+2.8v脉宽为3毫秒的正电压脉冲和单个-2.8v脉宽为3毫秒的负电压脉冲测试器件的稳定保持能力,在此过程中运用直流0.8v的电压去测试器件在脉冲模式作用之后的set和reset的电阻值,结果表明,器件的电阻的开、关态稳定时间在5

×

103以上,而且没有任何衰退现象,见图4中的d;

94.测试器件在一系列脉冲刺激作用下的典型set和rest响应,在set或者rest脉冲作用之后和前加上0.8v的读取电压去测试器件的阻值状态,通常响应时间被定义为前沿输入电压时间和有效电流响应之间的时间差,在set过程中器件的电流很高,在reset过程中器件的电流很低至于0;

95.图4中的a为在+2.8v脉宽为3毫秒的正电压脉冲作用下cu/csto/sio2/si器件的set响应时间,图4中的b为在-2.8v脉宽为3毫秒的负电压脉冲作用下cu/csto/sio2/si器件的reset响应时间;以上显示了cu/csto/sio2/si器件在+2.8v脉宽为3毫秒电脉冲作用下的set响应时间为620纳秒,在-2.8v脉宽为3毫秒电脉冲作用下的reset响应时间为1420纳秒,reset过程的响应时间比set过程的响应时间长得多,而且强的导电细丝的形成过程需要足够的热反应能来进行复位操作。

96.因此,实施例1的cu/csto/sio2/si器件在直流扫描模式下具有优异的性能,而且在脉冲模式刺激下会表现出快速的开关响应行为。

97.综上所述,本发明采用sio2薄膜作为介质层,其与传统的cmos工艺具有良好的一致性,并且具有高温稳定性;本发明忆阻器的csto层可以将sio2层钝化,进而形成牢固的多层结构以保护sio2层不受周围环境中的空气影响,使得器件可以长时间稳定地工作而不会发生任何退化,具有优异的耐久性和开关性能,可以在背景环境中稳定工作。

98.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1