一种隔离变压器电路的制作方法、隔离驱动电路及芯片与流程

本技术涉及集成电路,更具体地,涉及一种隔离变压器电路的制作方法、隔离驱动电路及芯片。

背景技术:

1、在智能电网、移动通信以及新能源汽车等新兴产业的牵引下,电力电子应用系统要求进一步提高系统的效率、小型化和增加功能,特别要求系统装备在尺寸、质量、功率和效率之间的权衡,比如服务器电源管理、电池充电器和太阳能电场的微逆变器。为了适应一些高压、高温、高效率及高功率密度的应用场合,开发出了高压集成电路(high voltageintegrated circuit,hvic)。

2、hvic是一种把mcu(microcontroller unit,微控制单元)信号转换成驱动igbt(insulated gate bipolar transistor,绝缘栅双极型晶体管)、mosfet(metal-oxide-semiconductor field-effect transistor,金属-氧化物半导体场效应晶体管)信号的集成电路产品。hvic一方面接收mcu的控制信号,驱动后续igbt或mosfet工作,另一方面将系统的故障状态检测信号送回mcu,是智能功率模组(intelligent power module,ipm)内部的关键芯片。

3、但是,目前的ipm内部的hvic采用纵向pn结和hvjt(high voltage junctionterminating,高压半导体器件和高电压结端点)隔离,参见图1a至图1c所示,隔离电压达不到驱动igbt或mosfet的驱动电压。

4、此外,目前hvic采用脉冲变压器实现驱动信号的隔离传输,脉冲变压器通过将pwm(pulse width modulation,脉冲宽度调制)信号完整耦合到次级后直接驱动mosfet,导通时间受到磁芯饱和特性的限制,导致传输延迟较大,传输速度较慢,并且由于mosfet存在较大的寄生电容,得到的驱动信号容易存在波形失真。

技术实现思路

1、本技术实施例所要解决的技术问题是相关技术中隔离驱动能力弱,同时隔离驱动传输延迟较大、传输速度较慢的问题。

2、为了解决上述技术问题,本技术实施例提供隔离变压器电路的制作方法,采用了如下所述的技术方案:

3、采用等离子体增强化学气相沉积法,在所述衬底上沉积二氧化硅介电质,形成第一二氧化硅隔离层;

4、在所述第一二氧化硅隔离层上溅镀金属膜,形成第一金属层,将隔离变压器电路的布线线路集成在所述第一金属层上;

5、采用等离子体增强化学气相沉积法,在所述第一金属层上沉积二氧化硅介电质,形成第二二氧化硅隔离层;

6、在所述第二二氧化硅隔离层上溅镀金属膜,形成第二金属层,在所述第二金属层上离子刻蚀出所述隔离变压器电路的输入线圈或者输出线圈,其中,所述输入线圈或者所述输出线圈的端口通过金属填充的导孔连接所述第一金属层上的布线线路;

7、采用等离子体增强化学气相沉积法,在所述第二金属层上沉积二氧化硅介电质,形成第三二氧化硅隔离层;

8、在所述第三二氧化硅隔离层上溅镀金属膜,形成第三金属层,在所述第三金属层上离子刻蚀出所述隔离变压器电路的输出线圈或者输入线圈,其中,所述输出线圈或者输入线圈的端口为键合区。

9、为了解决上述技术问题,本技术实施例提供一种隔离驱动电路,采用了如下所述的技术方案:

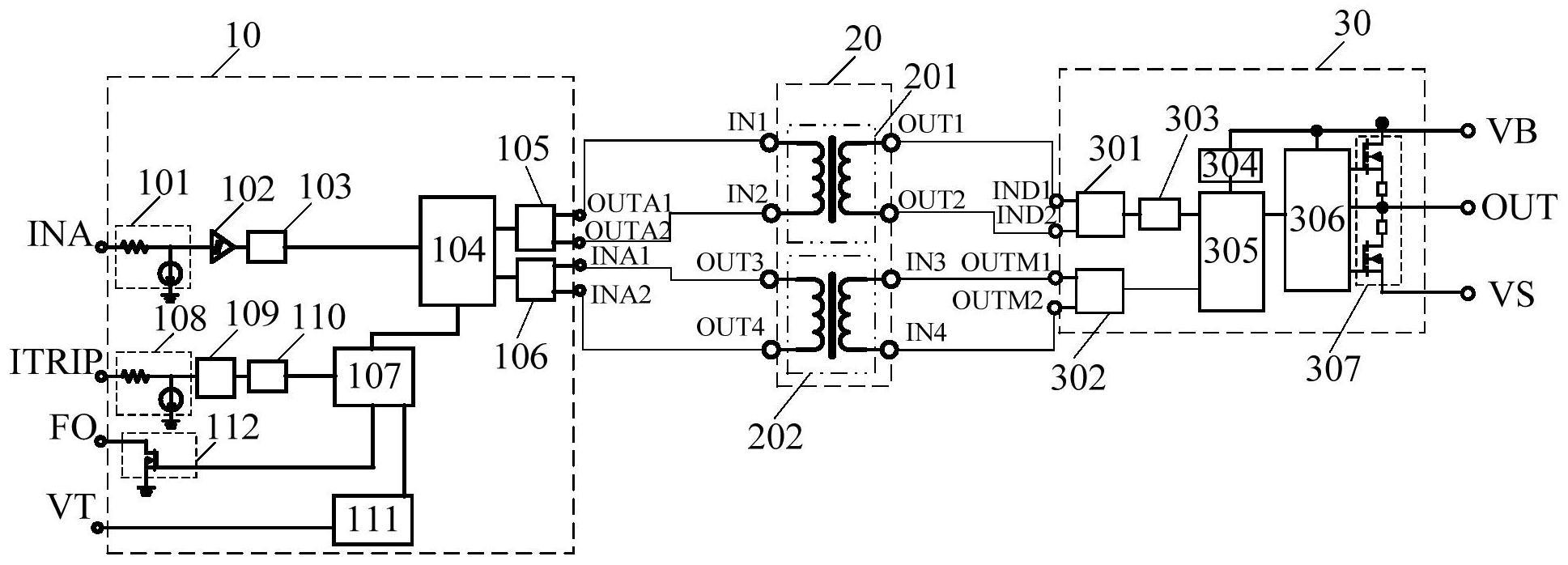

10、输入级电路、输出级电路和利用权利要求1所述的隔离变压器电路的制作方法所获得的隔离变压器电路,所述输入级电路、所述隔离变压器电路和所述输出级电路之间电连接;

11、所述输入级电路用于接收输入信号、故障信号以及所述输出级电路的异常反馈信号,将所述输入信号调制成所述隔离变压器电路的有效输入信号,并将所述有效输入信号通过所述隔离变压器电路传输至所述输出级电路,根据所述故障信号关断所述输入级电路的输出,并将接收到的所述异常反馈信号进行解调;

12、所述隔离变压器电路用于将所述有效输入信号传输至所述输出级电路,以及将所述异常反馈信号传输至所述输入级电路;

13、所述输出级电路用于将接收到的所述有效输入信号解调为方波信号,并把所述异常反馈信号通过所述隔离变压器电路传输至所述输入级电路。

14、进一步的,所述输入级电路包括第一esd保护电路、第一斯密特电路、第一滤波电路、第一逻辑电路、第一调制电路、第一解调电路以及故障反馈电路,其中:

15、所述第一esd保护电路连接至所述第一斯密特电路,用于释放电路中产生的静电电流;

16、所述第一斯密特电路连接至所述第一滤波电路,用于滤除干扰信号;

17、所述第一滤波电路与所述第一逻辑电路连接,用于滤除输入信号中的尖峰电压;

18、所述第一逻辑电路分别与所述第一调制电路、所述第一解调电路以及所述故障反馈电路连接,用于对所述输入信号、异常反馈信号和故障信号进行逻辑处理,并根据所述故障信号和所述异常反馈信号关断所述输入级电路的所有输出;

19、所述第一调制电路连接至所述隔离变压器电路,用于将所述输入信号调制成所述隔离变压器电路的有效输入信号,并将所述有效输入信号传输至所述隔离变压器电路;

20、所述第一解调电路连接至所述隔离变压器电路,用于把所述输出级电路传输的所述异常反馈信号进行解调,并反馈至所述第一逻辑电路;

21、所述故障反馈电路用于将故障信号通过故障输出电路输出,并反馈至所述第一逻辑电路。

22、进一步的,所述输入级电路还包括第二esd保护电路、过流保护电路、第二滤波电路;

23、所述过流保护电路通过所述第二滤波电路与所述故障反馈电路连接,用于检测外部采样电路反馈的电压信号,当所述电压信号大于基准电压时,输出过流保护信号,并将所述过流保护信号传输至所述第二滤波电路;

24、所述第二esd保护电路通过所述过流保护电路连接至所述第二滤波电路,用于释放电路中产生的静电电流;

25、所述第二滤波电路用于滤除所述过流保护信号的干扰信号,并将滤除处理后的所述过流保护信号传输至所述故障反馈电路,其中,所述过流保护信号作为所述故障反馈电路的故障信号。

26、进一步的,所述输出级电路包括第二解调电路、第二调制电路、第三滤波电路、欠压保护电路、第二逻辑电路、驱动和死区电路以及输出驱动电路;

27、所述第二解调电路连接于所述第三滤波电路和所述隔离变压器电路之间,用于将接收到的所述有效输入信号解调为方波信号,并发送至所述第四滤波电路;

28、所述第三滤波电路连接至所述第二逻辑电路,用于滤除所述方波信号的尖峰电压信号;

29、所述欠压保护电路与所述第二逻辑电路连接,用于检测所述输出级电路的供电电压,当所述供电电压低于第二预设阈值时,向所述第二逻辑电路传输欠压信号;

30、所述第二逻辑电路连接至所述驱动和死区电路,用于处理所述方波信号以及所述欠压信号;

31、所述驱动和死区电路连接至所述输出驱动电路,并与供电电压连接,用于将所述第二逻辑电路输出的信号进行放大以驱动所述输出驱动电路,并对所述输出驱动电路产生死区特性;

32、所述第二调制电路连接于所述第二逻辑电路与所述隔离变压器电路之间,用于将所述第二逻辑电路输出的异常反馈信号传输至所述输入级电路。

33、进一步的,所述隔离变压器电路包括第一隔离变压器和第二隔离变压器,所述输入线圈包括第一输入线圈和第二输入线圈,所述输出线圈包括第一输出线圈和第二输出线圈;

34、所述第一隔离变压器包括第一输入线圈和第一输出线圈,所述第一输入线圈与所述输入级电路连接,所述第一输出线圈与所述输出级电路连接,用于将所述有效输入信号依次通过所述第一输入线圈以及所述第一输出线圈传输至所述输出级电路;

35、所述第二隔离变压器包括第二输入线圈和第二输出线圈,所述第二输入线圈与所述输出级电路连接,所述第二输出线圈与所述输入级电路连接,用于将所述异常反馈信号依次通过所述第二输入线圈以及所述第二输出线圈传输至所述输入级电路。

36、进一步的,所述输入级电路还包括死区时间互锁电路、第三esd保护电路、第二斯密特电路、第四滤波电路、第三调制电路以及第三解调电路;

37、所述死区时间互锁电路连接于所述第一滤波电路、第四滤波电路和所述第一逻辑电路之间,用于在至少两路输入信号均为高电平时,输出互锁信号,并将所述互锁信号发送至所述第一逻辑电路;

38、所述第三esd保护电路连接至所述第二斯密特电路,用于释放电路中产生的静电电流;

39、所述第二斯密特电路连接至所述第四滤波电路,用于滤除干扰信号;

40、所述第四滤波电路连接至所述死区时间互锁电路,用于滤除输入信号尖峰电压;

41、所述第一逻辑电路分别与所述第三调制电路以及所述第三解调电路连接,用于根据所述互锁信号关断所述输入信号对应的输出;

42、所述第三调制电路连接至所述隔离变压器电路,用于将所述输入信号调制成所述隔离变压器电路的有效输入信号,并将所述有效输入信号传输至所述隔离变压器电路;

43、所述第三解调电路连接至所述隔离变压器电路,用于把所述输出级电路传输的所述异常反馈信号进行解调,反馈至所述第一逻辑电路。

44、为了解决上述技术问题,本技术实施例还提供一种隔离驱动芯片,采用了如下所述的技术方案:

45、所述隔离驱动电路的输入级电路和所述输出级电路的器件集成于所述衬底上,所述输入级电路和所述输出级电路的布线线路封装于所述第一金属层;

46、所述输入级电路和所述输出级电路通过所述键合区与所述隔离驱动电路的隔离变压器电路连接。

47、进一步的,所述衬底为soi衬底,所述soi衬底的顶层硅用于集成所述输入级电路和所述输出级电路的器件,所述器件之间形成二氧化硅隔离区。

48、进一步的,所述二氧化硅隔离区的雪崩击穿电压大于两倍所述隔离驱动芯片的耐压额定值;所述二氧化硅层的雪崩击穿电压大于两倍所述隔离驱动芯片的耐压额定值。

49、与现有技术相比,本技术实施例主要有以下有益效果:

50、本技术提供的隔离驱动电路的制作方法,通过采用等离子体增强化学气相沉积法,在衬底上沉积二氧化硅介电质,形成第一二氧化硅隔离层;在第一二氧化硅隔离层上溅镀金属膜,形成第一金属层,将隔离变压器电路的布线线路集成在第一金属层上;采用等离子体增强化学气相沉积法,在第一金属层上沉积二氧化硅介电质,形成第二二氧化硅隔离层;在第二二氧化硅隔离层上溅镀金属膜,形成第二金属层,在第二金属层上离子刻蚀出隔离变压器电路的输入线圈或者输出线圈,其中,输入线圈或者输出线圈的端口通过金属填充的导孔连接第一金属层上的布线线路;采用等离子体增强化学气相沉积法,在第二金属层上沉积二氧化硅介电质,形成第三二氧化硅隔离层;在第三二氧化硅隔离层上溅镀金属膜,形成第三金属层,在第三金属层上离子刻蚀出隔离变压器电路的输出线圈或者输入线圈,其中,输出线圈或者输入线圈的端口为键合区;本技术通过将隔离变压器电路的输入线圈和输出线圈分别设置在不同的金属层,可以制得隔离驱动电压较大的隔离变压器电路,提高驱动能力,缩短传输延迟,提高传输速度。

- 还没有人留言评论。精彩留言会获得点赞!