与用于模拟集成电路的可控制薄膜电阻器相关的方法和设备与流程

1.本说明书涉及薄膜电阻器。

背景技术:

2.集成模拟电路(例如,具有低偏移电压和低增益误差、电压参考和电流镜的电流感测放大器)可以包括多个薄膜电阻器作为集成电路元件。在许多情况下,薄膜电阻器是溅射的薄膜电阻器。高性能集成模拟电路可以需要具有或更严格规格的薄膜电阻器(例如,高精度电阻器对电阻器错配(约0.01%错配)、低温度电阻系数(《+/-50ppm/c)、以及低高温操作寿命(htol)可靠性漂移(《0.1%))用于高性能。

技术实现要素:

3.一种集成电路裸片,该集成电路裸片包括设置在第一氧化物层上的硅铬(sicr)薄膜电阻器。该sicr薄膜电阻器包括电阻器主体和电阻器头。第二氧化物层覆盖sicr薄膜电阻器。第二氧化物层具有暴露电阻器头的表面的开口。金属垫设置在第二氧化物层中的开口中并且与由开口暴露的电阻器头的表面接触。层间介电层设置在覆盖sicr薄膜电阻器的第二氧化物层上,并且金属填充的通孔从层间介电层的顶表面延伸穿过层间介电层并且接触设置在第二氧化物层中的开口中的金属垫。

4.一种集成电路裸片包括硅铬(sicr)薄膜电阻器,该sicr薄膜电阻器具有电阻器主体和设置在第一氧化物层上的电阻器头。该sicr薄膜电阻器;保护性介电层覆盖sicr薄膜电阻器。层间介电层设置在覆盖sicr薄膜电阻器的保护性介电层上;并且金属填充的通孔从层间介电层的顶表面延伸穿过层间介电层和保护性介电层,并且接触sicr薄膜电阻器的电阻器头。

5.一种集成电路裸片包括硅铬(sicr)薄膜电阻器,该sicr薄膜电阻器具有电阻器主体和设置在第一氧化物层上的电阻器头。层间介电层设置在覆盖sicr薄膜电阻器的介电层上。金属填充的通孔从层间介电层的顶表面延伸穿过层间介电层并且接触sicr薄膜电阻器的电阻器头。金属填充的通孔终止于设置在裸片中的着陆垫处。

6.一种集成电路裸片包括设置在衬底上的层间介电(ild)层。ild层包括设置在衬底上的第一金属层级(metal level)。金属填充的通孔从ild层的顶表面延伸穿过ild层以接触第一金属层级。硅铬(sicr)薄膜电阻器设置在ild层的顶表面上,其中sicr薄膜电阻器的底表面与从第一金属层级延伸到ild层的顶表面的金属填充的通孔接触。

7.一种方法包括在半导体衬底上形成包括第一金属层级的层间介电(ild)层,在ild层上形成第一氧化物层,以及在第一氧化物层上形成sicr薄膜。该方法还包括在sicr薄膜上形成第二氧化物层,图案化和蚀刻第二氧化物层中的开口以暴露sicr薄膜的部分,在图案化的第二氧化物层上沉积氮化钛(tin)层和氮氧化硅(sion)覆盖层。该方法还包括图案化和蚀刻氮化钛(tin)层和氮氧化硅(sion)覆盖层,以形成通过第二氧化物层中的开口接触sicr薄膜的接触垫,以及图案化和蚀刻第二氧化物层和sicr薄膜以界定sicr电阻器。

8.一个或多个具体实施的细节在附随附图和以下描述中阐明。其他特征将从说明书和附图中以及从权利要求书中显而易见。

附图说明

9.图1a示出了示例sicr薄膜电阻器。

10.图1b示出了三个掩模的示例集合。

11.图2示出了集成电路裸片的后端结构的一部分。

12.图3和图4示出了图2的后端结构的电阻器部分。

13.图5至图9示出了示例后端结构的电阻器部分。

14.图10至图12示出了示例后端结构的一部分。

15.图13示出了用于在后端结构中集成sicr电阻器的示例方法。

16.图14a至图14f示出了在制造的不同阶段处设置在半导体衬底上的后端结构。

具体实施方式

17.薄膜电阻器可以是在半导体衬底上形成的集成电路(ic)中的元件。薄膜电阻器可以例如是溅射的薄膜电阻器。示例溅射的薄膜电阻器可以具有由硅-铬(sicr)化合物或合金制成的非晶体,并且在本文中被称为sicr电阻器。在竖直集成系统(vis)中,sicr电阻器可以在多个金属化中形成在层间介电层中,并且通过设置在半导体器件裸片上的金属化层形成。sicr电阻器可以使用半导体制造工艺形成并集成在ic中,包括例如光刻图案化、材料沉积和材料蚀刻或去除技术。材料蚀刻或去除技术可以包括干式蚀刻、湿蚀刻和化学机械抛光(cmp)技术等。

18.本文的公开内容描述了不同的示例集成电路裸片结构,以及用于集成集成电路裸片结构中的sicr电阻器的不同方法。例如,通过在集成电路裸片结构中集成形成的sicr电阻器的过程期间保持形成的sicr电阻器的组成、非晶性质和表面界面结构,这些方法可以保持(基本上保持)形成的sicr电阻器的特性。在所公开的结构和方法中,通过避免(或尽可能减少)使表面暴露于蚀刻剂(可以用于界定或制造集成电路裸片结构的其它组件)来保护电阻器的表面(例如,顶表面和底表面)免受损坏。

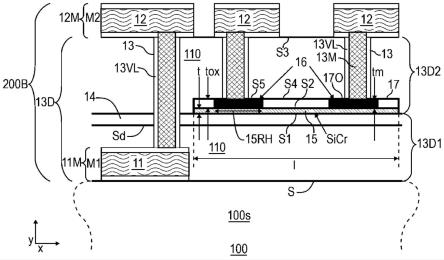

19.图1a示出了示例sicr电阻器15。sicr电阻器15可以由在衬底上溅射的材料的薄膜形成。材料可以包括硅和铬。sicr电阻器15通常可以形成为长度l(例如,在x方向上)、宽度w(在y方向上)和厚度t(在垂直于图1的页面的z方向上)的矩形薄膜条。在示例具体实施中,长度l可以是约1微米至约100微米,宽度w可以是约1微米至约20微米,并且厚度t可以是约50埃至约120埃。sicr电阻器15可以形成为具有非晶硅-铬组合物的薄膜。在一些示例具体实施中,可以通过从单个溅射靶溅射硅、铬和碳或其它元素的混合物以形成非晶硅-铬组合物来形成sicr电阻器15。在一些示例具体实施中,可以通过从单独的溅射靶共同溅射不同元素(例如,硅、铬、碳和或其它元素)以形成非晶硅-铬组合物来形成sicr电阻器15。在一些具体实施中,sicr电阻器15可以例如包含小百分比的碳(例如,按重量计约5%至15%)或其它元素。小百分比的碳可有助于维持sicr电阻器15的非晶性质和特性。

20.sicr电阻器15可以通过在主体部分(例如,电阻器主体15b)的两端上与电阻器部分(例如,电阻器头15rh)进行电接触来用于集成电路,例如,作为双端子电路元件。可以使

用互连导电结构(例如,接触垫、端子电线等)在电阻器主体15b的两端上与电阻器头15rh的部分(例如,接触区域15c)来制造电接触。

21.从溅射的薄膜的sicr电阻器15的制造和半导体集成电路裸片中的sicr电阻器15的集成可以涉及使用一组一个或掩模(光掩模)来光刻图案化并界定电阻器的不同区域。图1b示出了三个掩模(例如,掩膜1、掩膜2和掩码3)的示例集合,它们可以用于光刻图案化并界定集成电路裸片中的电阻器的不同区域。掩模1可以例如用于在从溅射的薄膜制造期间界定sicr电阻器15的形状和尺寸。掩模3可用于界定电阻器头部分(例如,电阻器头15rh),并且掩模2可用于界定电阻器接触部分(例如,接触区域15c),该电阻器接触部分可以用于与集成电路裸片中的sicr电阻器互连。

22.由溅射的薄膜制成的sicr电阻器15(图1a中示出)可以使用不同的集成方法集成在不同的示例集成电路裸片结构中(例如,如图2至图12等中所示)。例如,通过在集成电路裸片结构中集成形成的sicr电阻器的过程期间保持形成的sicr电阻器的组成、非晶性质和表面界面结构,集成方法可以保持(基本上保持)形成的sicr电阻器的特性。在所公开的结构和方法中,通过避免(或尽可能减少)使表面暴露于蚀刻剂(可以用于界定或制造集成电路裸片结构的其它组件)来保护电阻器的表面(例如,顶表面和底表面)免受损坏。

23.图2示出了集成电路裸片100的后端结构200b的一部分的横截面图,包括示例sicr电阻器15。sicr电阻器15可以是溅射的薄膜电阻器。sicr电阻器15可以例如是在垂直于图2的页面的z方向上具有长度l(例如,在x方向上)、厚度t(例如,在y方向上)和宽度(例如,宽度wb、wrh,图3)的大致矩形的薄膜材料条。在示例具体实施中,长度l可以在约1微米至约100微米之间,宽度w可以在约1微米至约20微米之间,并且厚度t可以在约50埃至约120埃之间。在示例具体实施中,可以通过溅射或共溅射硅和铬材料以形成非晶硅-铬组合物来形成sicr电阻器15。在一些具体实施中,sicr电阻器15可以包含小百分比的碳(例如,按重量计介于约5%与15%之间)。

24.如图2所示,后端结构200b可以设置在包括集成电路裸片100的半导体衬底100s的顶表面s上。后端结构200b可以包括金属化层11m和12m,这些金属化层分别对应于例如集成电路裸片100的第一金属层级11和第二金属层级12。金属化层11m和12m可以设置在半导体衬底100s的顶表面s上的层间介电层13d中。层间介电层13d可以包括子层间介电层13d1和13d2,其中子层间介电层13d1设置在半导体衬底100s的顶表面s上,并且子层间介电层13d2设置在子层间介电层13d1的顶表面sd上。包括第二金属层级12的金属化层12m可以设置在子层间介电层13d2的顶表面s3上。

25.介电层(例如,氧化物层14)可以封盖或覆盖子层间介电层13d1。可以在层间介电层13d中的氧化物层14的顶部上形成sicr电阻器15。sicr电阻器15可具有底表面s1(搁置在氧化物层14上)和顶表面s2。另一个介电层(例如,氧化物层17)可以封盖或覆盖sicr电阻器15。氧化物层17可以包括暴露sicr电阻器的顶表面s2的开口17o。金属垫16(例如,钨(w)垫)可以设置在开口17o中的顶表面s2上,用于在sicr电阻器的区域(例如,电阻器头15rh)中与sicr电阻器15电接触(以形成例如电阻器的端子)。金属垫16(例如,钨(w)垫)可以设置为与sicr电阻器15的顶表面s2直接接触,其中存在或不存在金属垫16与形成的sicr电阻器15的硅-铬材料之间的任何中间层(例如,粘合剂或阻挡层,如tin层)。

26.在示例具体实施中,氧化物层17可以在sicr电阻器15的顶表面s2上直接设置并图

案化。可以使用原硅酸四乙酯(teos)沉积工艺(teos沉积)由氧化硅(siox)制成氧化物层17。氧化物层17可以具有顶表面s4和厚度tox。在示例具体实施中,厚度tox可以在1000a到4000a(例如,1000a)的范围内。开口(例如,开口17o)可以通过光刻图案化氧化物层17(使用单个光电掩模,例如,掩模3,图1b))并且湿蚀刻图案化氧化物层17形成在图案化氧化物层17中。湿蚀刻可以例如使用稀释氢氟酸(hf)蚀刻剂。

27.在示例具体实施中,金属垫16(例如,钨(w)垫)可以由溅射金属(例如,w)以填充图案化氧化物层17中的开口(例如,开口17o)、然后是溅射金属的cmp平坦化(例如w-cmp)来形成。

28.金属垫16(例如,钨(w)垫)可以具有顶表面s5和厚度tm。在cmp平坦化之后,金属垫16厚度tm可以与图案化氧化物层17的厚度tox(例如,1000a)大约相同,并且金属垫16的顶表面s5和图案化氧化物层的顶表面s4可以是约共面的。

29.后端结构200b中的不同金属层级(例如,金属层级12和金属层级11以及sicr电阻器15上的金属层级12和金属垫16)可以通过金属填充的通孔13互连。在示例具体实施中,金属填充的通孔13可以是衬有衬里13vl并且填充有金属13m的通孔。在示例具体实施中,衬里13vl可以例如是氮化钛(tin)衬里,并且金属13m可以例如是w。

30.在示例具体实施中,形成金属填充的通孔13以接触在sicr电阻器15上的金属垫16可以涉及从顶表面s3穿过子层间介电层13d2蚀刻通孔到金属垫16的表面s5,在通孔的侧壁衬有衬里13vl,以及用金属13m填充通孔以接触金属垫16。

31.在示例具体实施中,蚀刻通孔可以涉及在衬底100s上具有均匀深度精度的蚀刻,以与可以在衬底100s上形成的多个sicr电阻器15进行均匀接触。

32.图3示出了例如图2的后端结构200b的电阻器部分的平面图。例如,在图2中的子层间介电层13d2的顶表面s3下观察图3中所示的平面图。图4示出了例如图2所示的后端结构200b的电阻器部分的横截面图。

33.如图3所示,sicr电阻器15可以是具有长度l的薄膜条。sicr电阻器15可以包括电阻器主体15b(具有长度lb和宽度wb)和电阻器主体15b的两端处的电阻器头部分15rh(具有长度lrh和宽度wrh)。如图4所示,金属填充的通孔13(如先前参考图2所描述)从顶表面s3延伸穿过子层间介电层13d2到图案化氧化物层17的顶表面s4附近。金属填充的通孔13中的金属13m可以通过sicr电阻器的金属垫16(经由与电阻器头15rh接触)与sicr电阻器建立接触。

34.在示例具体实施中,示例sicr电阻器15可以包括50a至100a厚的非晶sicr溅射薄膜,其中cr的重量%介于40%与60%之间,并且c的重量%介于5%与15%之间。非晶sicr溅射的薄膜可以具有约750欧姆/平方至约1500欧姆/平方的电阻率。电阻器-电阻器错配(集成电路裸片100中的多个电阻器之间)对于5

×

50sq.μm电阻器可以为约0.01%(平均+3-西格玛)(即,10,000欧姆中的1欧姆)。电阻温度系数可以小于约+/-150ppm/c。sicr电阻器15可以具有小于约0.1%的htol可靠性漂移,以及小于约0.1%的可靠性漂移的高温储存寿命(htsl)。

35.在上文参考图2-图4描述的示例后端结构200b中,溅射金属(在金属垫16中)完全填充开口17o的深度,使得金属垫16的顶表面s5与图案化氧化物层17的顶表面s4大致共面(换句话讲,金属垫16和图案化氧化物层17具有大约相同的厚度,tm=tox)。

36.在一些示例具体实施中,具有比图案化氧化物层17的厚度tox更大的氧化物厚度(例如,tox)的氧化物层(例如,氧化物层18,图5)可以设置在sicr电阻器15上以保护表面s2。开口(例如,开口18o),如图3和图4中的开口17o,可以图案化和蚀刻在氧化物层18中以接收溅射金属以在开口中形成金属垫16。开口18o中的金属溅射(用于金属垫16)可以仅部分地填充开口18o的深度,使得开口18o中的金属垫16的厚度tm小于图案化氧化物层18的厚度tox。

37.图5示出了示例后端结构500b的电阻器部分的横截面图,其中沉积在sicr电阻器15上的图案化氧化物层18(例如,覆层沉积的siox氧化物层)的厚度tox大于图2和图4中所示的图案化氧化物层17的厚度tox。在图4所示的示例后端结构500b中,金属垫16部分地填充氧化物层18中的开口18o,使得金属垫16的顶表面s5低于图案化氧化物层18的顶表面s6(换句话讲,金属垫16具有小于图案化氧化物层18的厚度tox的厚度tm)。在示例具体实施中,厚度tox可以是约2500a,并且厚度tm可以在约1000a到1500a的范围内。

38.如先前所讨论的(图1-图3),金属填充的通孔13中的金属13m可通过设置在开口18o中(氧化物层18中)与sicr电阻器的电阻器头15rh接触的金属垫16与sicr电阻器15建立接触。

39.设置在sicr电阻器15的顶表面s2上的氧化物层18的较大厚度(即,tox)(图5)保护sicr电阻器15的顶表面s2比由氧化物层17的较小厚度(即,tox)(图2和图4)提供的保护更多。

40.在一些示例具体实施中,与sicr电阻器15的接触可以使金属13m(例如,金属填充的通孔)与sicr电阻器的sicr材料直接接触,而不使用在金属填充的通孔与sicr电阻器的电阻器头15rh之间的中间金属垫16。

41.作为示例,图6示出了集成电路裸片100的后端结构600b的一部分的横截面图,包括与用于互连的金属通孔直接接触的示例sicr电阻器15。

42.如图6所示,保护层18(例如,氮化硅层或具有蚀刻停止能力的其它层)可以沉积在sicr电阻器15的顶表面s2上。层18可以例如为几百埃(例如,500a)厚。金属填充的通孔13可以从子层间介电层13d2的顶表面s3延伸并且在sicr电阻器15处到达并终止。形成金属填充的通孔13以接触sicr电阻器15可以涉及从顶表面s3穿过子层间介电层13d2到sicr电阻器15的表面s2的通孔的精度深度蚀刻。层18(例如,氮化硅层)相对于通孔蚀刻剂(氧化物蚀刻剂)的蚀刻停止能力可以在层18处停止通孔蚀刻并且辅助深度控制。下游氮化物蚀刻可以用于在通孔填充有金属(例如,金属13m)之前清除氮化硅材料的通孔的内侧。金属填充的通孔13中的金属13m可以直接接触sicr电阻器15(在后端结构200b和500b(图2至图5)的前述示例具体实施中不使用中间金属垫16)。

43.在一些示例具体实施中,可以通过穿过sicr电阻器15的金属填充的通孔(例如,金属填充的通孔33)的侧壁来制造与sicr电阻器15的接触。作为示例,图7示出了集成电路裸片100的后端结构700b的一部分的横截面图,包括通过通孔侧壁与金属直接接触的示例sicr电阻器15。

44.如图7所示,金属填充的通孔33可以从子层间介电层13d2的顶表面s3延伸,穿通sicr电阻器15,并且着陆(即,停止)在金属化层11m中的第一金属层级11上。金属填充的通孔33,如金属填充的通孔13,可以衬有衬里13vl并且填充有金属13m。通孔中的金属13m可以

通过通孔的侧壁部分13s接触sicr电阻器15。

45.在一些示例具体实施中,可以使用延伸穿过子层间介电层13d1或子层间介电层13d2的金属插头(例如,w插头)来制造与sicr电阻器15的接触。作为示例,图8示出了集成电路裸片100的后端结构700b的一部分的横截面图,包括由金属插头接触的示例sicr电阻器15。

46.图8示出了示例后端结构800b的横截面图,其中金属插头(例如,金属填充的通孔22)从顶表面s3延伸穿过子层间介电层13d2接触sicr电阻器15。如图8所示,sicr电阻器15设置在设置于子层间介电层13d1上的氧化物层14上。封盖层(例如,氧化物层17)覆盖sicr电阻器15。氧化物层14和17保护sicr电阻器15的底表面s1和顶表面s2。垫21(例如,tin垫)设置在sicr电阻器15的电阻器头区域15rh中的氧化物层17上。垫21的tin材料还填充氧化物层17中的开口17o,并且在sicr电阻器15的电阻器头区域15rh中接触sicr电阻器15。从顶表面s3延伸穿过子层间介电层13d2的金属填充的通孔22(例如,w插头)在垫21上着陆以接触sicr电阻器15的电阻器头区域15rh。形成金属填充的通孔22可以涉及使用对tin上的氧化物具有正型选择性的氧化物蚀刻剂蚀刻从顶表面s3延伸穿过子层间介电层13d2的通孔。

47.在一些示例具体实施中,可以使用着陆垫(例如,蚀刻停止)停止或终止通孔(例如,在sicr电阻器15处)的蚀刻来实现从顶表面s3延伸穿过子层间介电层13d2以接触sicr电阻器15的通孔的蚀刻的深度控制。

48.作为示例,图9示出了集成电路裸片100的后端结构900b的一部分的横截面图,包括终止于着陆垫处的金属插头或金属填充的通孔接触的示例sicr电阻器15。

49.如图9所示,着陆垫(例如,着陆垫23)在低于顶表面sd的子层间介电层13d1中形成,以与sicr电阻器15的电阻器头15rh区域对准)。着陆垫23可以例如由蚀刻停止材料(例如,w、tin或铜)制成。着陆垫23可以控制形成从顶表面s3延伸穿过子层间介电层13d2的金属填充的通孔22所需的蚀刻深度。从顶表面s3蚀刻穿过子层间介电层13d2的金属插头(例如,金属填充的通孔22)可以穿通sicr电阻器15到达着陆垫上。可以通过金属插头(例如,金属填充的通孔22)的侧壁22s以及沿着着陆垫23的sicr到tin界面建立与sicr电阻器15的电接触。

50.作为另一示例,图10示出了集成电路裸片100的后端结构1000b的一部分的横截面图,包括由终止于着陆垫(例如,着陆垫24)处的金属插头或金属填充的通孔接触的示例sicr电阻器15。

51.如图10所示,着陆垫(例如,着陆垫24)可以形成在子层间介电层13d1的表面sd上。着陆垫24可以具有带竖直侧和顶表面的块形状(例如,矩形或立方体块)。着陆垫24(块)可以具有例如宽度wp和高度hp。着陆垫24可以具有竖直侧sw和顶表面sp(例如,在子层间介电层13d1的表面sd上方的高度hp处)。着陆垫(例如,着陆垫24)可以例如由金属或金属材料(例如,w、tin或铜)制成,并且相对于氧化物或介电蚀刻剂具有蚀刻停止选择性。

52.形成为子层间介电层13d1的表面sd上的溅射薄膜的sicr电阻器15可以符合设置在表面sd上的着陆垫24的形貌。例如,sicr电阻器15可以在着陆垫24的侧面sw和顶表面sp上保形地延伸,使得电阻器15的电阻器(例如,电阻器头15rh)的区域设置在着陆垫24的顶表面sp上。从顶表面s3蚀刻穿过子层间介电层13d2的金属插头(例如,金属填充的通孔22)可以穿通sicr电阻器15的电阻器头15rh到达着陆垫24中。可以通过金属插头(例如,金属填

充的通孔22)的侧壁22s以及沿着着陆垫24的sicr到tin界面建立与电阻器头15rh的电接触。

53.在例如如上参考图9和图10描述的后端结构900b和1000b中使用蚀刻停止(例如,着陆垫23、着陆垫24)可以消除对用于接触sicr电阻器15的金属填充的通孔的蚀刻中的深度精度的需要。

54.在一些示例具体实施中,金属填充的通孔可以将设置在子层间介电层13d1上方的sicr电阻器15连接到子层间介电层13d1中的金属线(例如,第一金属层级11)。

55.作为示例,图11示出了集成电路裸片100的后端结构1100b的一部分的横截面图,包括与金属化层11m中的电阻器和第一金属层级11之间延伸的金属填充的通孔接触的示例sicr电阻器15。

56.在图11所示的示例中,sicr电阻器15被图案化并且形成在子层间介电层13d1的表面sd上。保护性介电层(例如,介电层25)设置在sicr电阻器15的顶表面s2上。介电层25可以例如由氮化硅(sin)制成。金属插头或金属填充的通孔26从第一金属层级11延伸穿过子层间介电层13d1以接触sicr电阻器15的底表面s1。金属填充的通孔26,如金属填充的通孔13,可以填充有金属,包括例如钨或其它导电金属或合金。仅延伸穿过子层间介电层13d1的金属填充的通孔26的长度(或高度)可比例如金属填充的通孔13短,该金属填充的通孔13可以延伸穿过后端结构1100b的金属化方案中的子层间介电层13d1和子层间介电层13d1两者。

57.在sicr电阻器15被图案化并形成在子层间介电层13d1的表面sd上之前,可以在子层间介电层13d1中形成金属填充的通孔26。

58.在一些示例具体实施中,设置在sicr电阻器15上方的金属或金属垫可以用作金属填充的通孔的着陆垫以接触电阻器。

59.作为示例,图12示出了集成电路裸片100的后端结构1200b的一部分的横截面图,包括与在设置在电阻器上方的金属或金属垫中停止的金属填充的通孔接触的sicr电阻器15。

60.在图12所示的示例中,sicr电阻器15形成在子层间介电层13d1的表面sd上的氧化物层14上。保护性介电层(例如,介电层27)设置在sicr电阻器15的顶表面s2上。介电层27可以例如是图案化的teos氧化物层(使用例如电阻器主体掩模)以在电阻器的主体区域(即,电阻器主体15b)上形成保护结构。

61.此外,着陆垫28p设置在电阻器的电阻器头15rh上。着陆垫28可由金属或金属材料(例如,w、tin或铜)制成。可以通过图案化和蚀刻沉积在介电层27和电阻器的电阻器头15rh部分上的金属层来形成着陆垫28。图12还示出了通过金属层蚀刻工艺去除的金属层的部分28e,以及可以通过在金属层蚀刻工艺中过度蚀刻去除的介电层27的部分27e。

62.介电层27保护电阻器的至少主体部分(例如,电阻器主体15b)的表面不经受金属层蚀刻工艺中的蚀刻剂。

63.从顶表面s3蚀刻穿过子层间介电层13d2的金属插头或金属填充通孔13可以着陆(即,停止)在电阻器的电阻器头15rh部分上方的着陆垫28上,以与sicr电阻器15建立电连接。

64.图13示出了用于在设置在半导体衬底(例如,半导体衬底100s)的顶表面s上的后端结构(例如,后端结构1400b,图14f)中集成sicr电阻器(例如,sicr电阻器15)的示例方法

1300。

65.方法1300包括在半导体衬底上形成第一金属层级(例如,金属层级1)(1302);在包括第一金属层级的半导体衬底上形成第一层间介电层(ild)(1304);在第一ild上沉积第一氧化物层(1306);在第一氧化物层上形成sicr薄膜(1308);在sicr薄膜上沉积第二氧化物层(1310)。

66.方法1300还包括图案化和蚀刻第二氧化物层中的开口以暴露sicr薄膜的部分(1312);在图案化的第二氧化物层上沉积氮化钛(tin)层和氮氧化硅(sion)覆盖层(1314);图案化和蚀刻氮化钛(tin)层和氮氧化硅(sion)覆盖层以形成接触垫,该接触垫通过第二氧化物层中的开口接触sicr薄膜(1316);图案化和蚀刻第二氧化物层和sicr薄膜以界定sicr电阻器(1318)。

67.方法1300还包括在接触垫和sicr电阻器的顶部上形成第二ild层(1320);图案化第二ild层和穿过第二ild层蚀刻通孔以着陆在第二氧化物层中的接触垫上(1322);以及用金属或金属合金填充通孔(1324)。

68.图14a-图14f示出了设置在半导体衬底100s上的后端结构1400b在制造的不同阶段或在用于将sicr电阻器集成在后端结构中的方法1300的不同步骤之后的横截面图。

69.图14a示出了在第一阶段(例如,在方法1300、步骤1310之后)的后端结构1400b。如图14a所示,在第一阶段,后端结构1400b包括第一层间介电层(ild)(例如,层13d1),其包围设置在半导体衬底100s上的第一金属层级(例如,金属层级11)。层13d1可以通过在衬底100s上形成的金属线(例如,金属层级11)上沉积氧化物来形成。层13d1可以例如通过teos沉积制成,并且在氧化物cmp平坦化步骤之后可以具有约千埃至几千埃(例如,3000a)范围内的厚度td1。层13d1可以被封盖氧化物层(例如,氧化物层14)覆盖。

70.氧化物层14可以例如通过teos沉积制成,并且可以具有在约几百埃至约几千埃(例如,1000a)范围内的厚度toc。硅铬材料的薄膜(例如,sicr薄膜15tf)沉积在氧化物层14上,例如通过溅射或共同溅射包括硅和铬的材料。进一步地,另一个封盖氧化物层(例如,氧化物层17)设置在sicr薄膜15tf上。氧化物层17(如氧化物层14)可以例如通过teos沉积制成,并且可以具有约一百埃至约几千埃(例如,1000a)范围内的厚度tox。

71.sicr薄膜15tf可具有在约40a到约100a(例如,60-90a)范围内的厚度t。sicr薄膜15tf可以是在稍后阶段在后端结构1400b中形成的sicr电阻器(例如,sicr电阻器15,图14d)的前体材料。可以在溅射沉积sicr薄膜15tf的组分(硅、铬等)之后对其进行退火,以例如活化其电阻性质。sicr薄膜15tf可以例如在约400c到425c的范围内的温度下退火。在示例具体实施中,退火的sicr薄膜15tf可以具有约几百至几千欧姆/平方(例如,1000欧姆/平方)范围的电阻率。

72.图14b示出了在第二阶段(例如,在方法1300、步骤1310之后)的后端结构1400b。如图14b所示,在第二阶段,开口17o形成在氧化物层17中以暴露下面的sicr薄膜15tf的部分。在开口17o中暴露的下面的sicr薄膜15tf的部分稍后可以形成电阻器头部分(例如,sicr电阻器15的电阻器头15rh)。在示例具体实施中,施加到氧化物层17的i-线抗蚀剂涂层可以使用掩模(例如,电阻器头掩膜、掩模3,图1b)进行光刻图案化,以界定对应于sicr电阻器15的电阻器头部分的开口14o。在uv抗蚀剂烘烤之后,可以使用例如对硅-铬具有高选择性的湿蚀刻在氧化物层17中蚀刻开口17o。可以在不损坏sicr薄膜15tf的情况下,在没有灰分或轻

度灰分工艺的情况下剥离抗蚀剂。

73.图14c示出了在第三阶段(例如,在方法1300、步骤1314之后)的后端结构1400b。如图14c所示,在第三阶段,tin层30沉积在开口17o中和氧化物层17之上。tin层30可以具有在约1000a到2000a(例如,1500a)范围内的厚度。进一步地,氮氧化硅蚀刻停止层/抗反射涂层(arc)(例如,sion层31)可以沉积在tin层30上。sion层31可以具有在约200a到800a(例如,300a)范围内的厚度。

74.图14d示出了在第四阶段(例如,在方法1300、步骤1316之后)的后端结构1400b。如图14d所示,在第四阶段,氧化物层17之上的tin层30(和sion层31)的部分使用sicr接触掩模(例如,掩膜2,图1b)图案化并去除(即,蚀刻)以界定接触垫30cp,该接触垫通过氧化物层17中的开口17o接触sicr薄膜15tf。tin层30(和sion层31)的未被移除并且保留形成接触垫30cp的部分由sicr接触掩模(例如,掩膜2,图1b)光刻界定。

75.图14e示出了在第五阶段(例如,在方法1300、步骤1318之后)的后端结构1400b。如图14e所示,在第五阶段,氧化物层17和sicr薄膜15tf的部分(例如,部分17r和15tfr)使用掩模(例如,掩膜1,图1b))图案化,并且被去除(即,蚀刻)以界定设置在氧化物层14上的sicr电阻器15。

76.图14f示出了在第六阶段(例如,在方法1300、步骤1324之后)的后端结构1400b。如图14f所示,在第六阶段,第二层间介电层(ild)(例如,层13d2)设置在第一层间介电层(ild)(即,层13d1)上包围sicr电阻器15和接触垫30cp。层13d2可以例如通过teos沉积形成,并且可以具有在约千埃至约几千埃(例如5500a)范围内的厚度td2。

77.如图14f所示,在第六阶段,金属填充的通孔13从层13d2的顶表面s3延伸,以到达与sicr电阻器15的电阻器头部分(例如,电阻器头15rh)接触的接触垫30cp。其它金属填充的通孔13可以从层13d2的顶表面s3延伸以到达层13d1中的第一金属层级11。

78.在示例具体实施中,最初可以沉积更厚(例如,约8000埃)的teos氧化物层以形成初始层13d2(未示出)。层13d2的顶表面s3可以通过初始层的化学机械抛光(cmp)来制备。cmp可以去除一些沉积的氧化物(例如,3000a的氧化物)并减小层13d2的厚度(例如,到约5500a)。通孔13的形成可以包括顶表面s3的光刻图案化(使用掩模)以界定通孔的位置,并且蚀刻通孔(例如,使用氧化物蚀刻剂)穿过层13d2以到达接触垫30cp(以及在金属层级1上)。接触垫30cp可以充当蚀刻的蚀刻停止。蚀刻的通孔可以衬有tin衬里并且填充有金属或金属合金。在示例具体实施中,通孔13可以填充有溅射的钨(w)。如果在通孔填充过程中任何东西沉积在表面s3上,则可以执行钨cmp步骤以去除过量的w。

79.在制造后端结构1400b使用的蚀刻工艺期间,sicr电阻器15的表面保持由氧化物层17保护,避免暴露于蚀刻剂。

80.在至少一个总体方面,方法可以包括在半导体衬底上形成包括第一金属层级的层间介电(ild)层,和/或在ild层上形成第一氧化物层。该方法可以包括在第一氧化物层上形成sicr薄膜,在sicr薄膜上形成第二氧化物层,和/或图案化和蚀刻第二氧化物层中的开口以暴露sicr薄膜的部分。该方法可以包括在图案化的第二氧化物层上沉积氮化钛(tin)层和氮氧化硅(sion)覆盖层,图案化和蚀刻氮化钛(tin)层和氮氧化硅(sion)覆盖层以形成接触垫,该接触垫通过第二氧化物层中的开口接触sicr薄膜,和/或图案化和蚀刻第二氧化物层和sicr薄膜以界定sicr电阻器。

81.在一些具体实施中,ild层是第一ild层。该方法可以包括在接触垫和sicr电阻器的顶部上形成第二ild层,图案化第二ild层和穿过第二ild层蚀刻通孔以着陆在第二氧化物层中的接触垫上,和/或用金属或金属合金填充通孔。

82.在本文所述的不同集成电路裸片的一些示例具体实施中,sicr薄膜电阻器具有在约40埃至约100埃范围内的厚度,并且在一些示例具体实施中,sicr薄膜电阻器包括非晶硅-铬薄膜,其中cr的重量%介于40%与60%之间,并且c的重量%介于0%与15%之间。

83.在本文所述的不同集成电路裸片的一些示例具体实施中,金属垫的顶表面和第二氧化物层的顶表面约为共面。

84.在本文所述的不同集成电路裸片的一些示例具体实施中,金属填充的通孔包括氮化钛(tin)衬里,并且填充有钨(w)金属。

85.在本文所述的不同集成电路裸片的一些示例具体实施中,保护性介电层是厚度在约200埃至约800埃范围内的氮化硅层。

86.在本文所述的不同集成电路裸片的一些示例具体实施中,保护性介电层是厚度在约200埃至约800埃范围内的氮化硅层。

87.在本文所述的不同集成电路裸片的一些示例具体实施中,包括设置在sicr薄膜电阻器上的顶表面上的氮化硅层。

88.在本文所述的不同集成电路裸片的一些示例具体实施中,着陆垫包括氮化钛(tin)。

89.在本文所述的不同集成电路裸片的一些示例具体实施中,覆盖电阻器主体的氧化物层包含原硅酸四乙酯(teos)氧化物。

90.应当理解,在前述描述中,当元件诸如层、区域、衬底或部件被提及为在另一个元件上,连接到另一个元件,电连接到另一个元件,耦接到另一个元件,或电耦接到另一个元件时,元件可以直接地在另一个元件上,连接到或耦接到另一个元件上,或者可以存在一个或多个中间元件。相反,当元件被提及直接在另一个元件或层上、直接连接到另一个元件或层、或直接耦接到另一个元件或层时,不存在中间元件或层。虽然在整个具体实施方式中可能不会使用术语直接在

…

上、直接连接到

…

、或直接耦接到

…

,但是被示为直接在元件上、直接连接或直接耦接的元件能以此类方式提及。本技术的权利要求书(如果存在的话)可被修订以叙述在说明书中描述或者在附图中示出的示例关系。

91.如在本说明书和权利要求书中所使用的,除非根据上下文明确地指出特定情况,否则单数形式可包括复数形式。除了附图中所示的取向之外,空间相对术语(例如,在

…

上方、在

…

上面、在

…

之上、在

…

下方、在

…

下面、在

…

之下、在

…

之以下等)旨在涵盖装置在使用或操作中的不同取向。在一些具体实施中,在

…

上面和在

…

下面的相对术语可分别包括竖直地在

…

上面和竖直地在

…

下面。在一些具体实施中,术语邻近能包括横向邻近或水平邻近。

92.一些具体实施可使用各种半导体处理和/或封装技术来实现。一些具体实施可使用与半导体衬底相关联的各种类型的半导体处理技术来实现,该半导体衬底包含但不限于,例如硅(si)、砷化镓(gaas)、氮化镓(gan)、碳化硅(sic)等。

93.虽然所描述的具体实施的某些特征已经如本文所述进行了说明,但是本领域技术人员现在将想到许多修改形式、替代形式、变化形式和等同形式。因此,应当理解,所附权利

要求书旨在涵盖落入具体实施的范围内的所有此类修改形式和变化形式。应当理解,这些修改形式和变化形式仅仅以举例而非限制的方式呈现,并且可以进行形式和细节上的各种变化。除了相互排斥的组合以外,本文所述的设备和/或方法的任何部分可以任意组合进行组合。本文所述的具体实施可包括所描述的不同具体实施的功能、部件和/或特征的各种组合和/或子组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1