铁电存储器件及其制造方法

1.本发明涉及存储技术领域,尤其涉及一种铁电存储器件及其制造方法。

背景技术:

2.随着大数据,物联网的需求越来越广泛,传统的存储器已经不能满足高速高集成度的要求,新材料、新器件的新型存储器具有更广阔的发展潜力和研究价值。

3.氧化铪基铁电材料是纳米电子学中的关键材料,材料可以实现自发极化翻转特性,具有稳定的翻转性能和读写性能。例如,锗基铁电晶体管(fe-fet)是存储器中的关键器件,器件可以实现存储器非破坏读取,并且与coms工艺结合,具有功耗低,响应速度快的特点。然而,目前这类铁电存储器件的循环次数普遍只能达到10的5次方,器件的耐久性还有待提升。

技术实现要素:

4.有鉴于此,本技术实施例提供了一种铁电存储器件及其制造方法,能够有效地提升锗基铁电器件的耐久性。

5.第一方面,本技术实施例提供了一种铁电存储器件,包括:

6.锗衬底;

7.铁电层,与所述锗衬底层叠设置;

8.上电极,设置在所述铁电层的远离所述锗衬底的表面;以及

9.氧化锆层,设置在所述锗衬底与所述铁电层之间,所述氧化锆层用于阻断所述锗衬底与所述铁电层的接触。

10.进一步地,所述氧化锆层的厚度为0.5nm~5nm。

11.进一步地,所述氧化锆层为二氧化锆层。

12.第二方面,本技术实施例还提供了一种铁电存储器件,包括:

13.锗衬底;

14.设置在所述锗衬底的源极、漏极以及在所述源极和漏极之间延伸的沟道区;

15.铁电层,设置在所述沟道区上;

16.栅极,设置在所述铁电层上;

17.氧化锆层,设置在所述沟道区与所述铁电层之间,所述氧化锆层用于阻断所述沟道区锗材料与所述铁电层的接触。

18.进一步地,所述氧化锆层的厚度为0.5nm~5nm,所述氧化锆层为二氧化锆层。

19.第三方面,本技术实施例还提供了一种铁电存储器件的制造方法,所述方法包括:

20.提供锗衬底;

21.在所述锗衬底表面形成氧化锆层,用于阻断所述锗衬底与铁电层的接触;

22.在所述氧化锆层表面形成铁电层;

23.在所述铁电层上形成上电极。

24.进一步地,所述在所述锗衬底表面形成氧化锆层,包括:

25.在所述锗衬底表面沉积厚度为0.5nm~5nm的氧化锆层。

26.进一步地,所述氧化锆层的沉积温度在室温至300摄氏度之间。

27.第四方面,本技术实施例还提供了一种铁电存储器件的制造方法,所述方法包括:

28.提供锗衬底;

29.在所述锗衬底上形成源极、漏极以及在所述源极和漏极之间延伸的沟道区;

30.在所述沟道区上依次层叠形成氧化锆层、铁电层以及栅极,其中,所述氧化锆层用于阻断沟道区锗材料与铁电层的接触。

31.进一步地,所述在所述锗衬底上形成源极、漏极以及在所述源极和漏极之间延伸的沟道区,以及在所述沟道区上依次层叠形成氧化锆层、铁电层以及栅极,包括:

32.在所述锗衬底表面依次沉积氧化锆膜层、铁电材料膜层以及栅极材料膜层;

33.利用光刻工艺以及刻蚀工艺对所沉积的膜层进行图案化处理,在所述锗衬底表面预定义的栅极区域形成依次层叠的氧化锆层、铁电层以及栅极;

34.对所述锗衬底表面预定义的源极区域和漏极区域进行离子注入,形成源极、漏极以及在所述源极和漏极之间延伸的沟道区。

35.本技术实施例中提供的一个或多个技术方案,至少具有如下技术效果或优点:

36.本技术实施例提供的铁电存储器件及其制造方法,通过在锗衬底与铁电层之间增设一层氧化锆层,阻断锗衬底与铁电层的接触,即隔离锗与铁电材料,以达到降低锗与铁电材料界面处陷阱,减小漏电的效果,使器件具备良好的抗疲劳能力,有效地提升了锗基铁电器件的耐久性,从而有利于保证器件在循环过程中,具有良好的读写能力和较低的误码率。

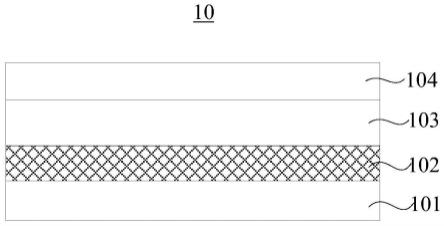

附图说明

37.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

38.图1示出了现有器件的耐久性试验结果图;

39.图2示出了本说明书实施例中一种铁电存储器件的结构示意图;

40.图3示出了本说明书实施例中另一种铁电存储器件的结构示意图;

41.图4示出了本说明书实施例中一种铁电存储器件的制造方法流程图;

42.图5示出了图4对应的制造流程中沉积氧化锆层后的结构示意图;

43.图6示出了图4对应的制造流程中沉积铁电层后的结构示意图;

44.图7示出了本说明书实施例中另一种铁电存储器件的制造方法流程图;

45.图8示出了锗衬底的结构示意图;

46.图9示出了沉积氧化锆膜层后的结构示意图;

47.图10示出了沉积铁电材料膜层后的结构示意图;

48.图11示出了沉积栅极材料膜层后的结构示意图;

49.图12示出了图案化处理后的结构示意图;

50.图13示出了对比试验的耐久性试验结果图。

具体实施方式

51.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

52.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

53.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。本文中,室温是指25摄氏度。

54.发明人对锗基铁电存储器件的耐久性进行了长期研究,发现其耐久性较差的可能性为:随着读写次数的增加,锗与铁电材料界面处陷阱增多,漏电增加,铁电性能退化严重,无法正常读取“0”和“1”。此外,不稳定的界面层geo

x

也是导致耐久性差的原因之一。

55.图1示出了对现有电容型锗基铁电存储器件进行测试得到的耐久性试验数据,其中,横坐标为器件的循环次数(cycles),纵坐标为器件铁电层的极化值(pr,单位为μc/cm2)。拟合曲线a(包括a1和a2)为电场强度e

max

=2.3mv/cm情况下的器件铁电层极化值与循环次数的对应关系曲线。其中,拟合曲线a1表示加正压情况下,器件铁电层极化值(p

r+

)与循环次数的对应关系曲线,拟合曲线a2表示加负压情况下,器件铁电层极化值(p

r-)与循环次数的对应关系曲线。拟合曲线b(包括b1和b2)为电场强度e

max

=3.1mv/cm情况下的器件铁电层极化值与循环次数的对应关系曲线,其中,拟合曲线b1表示加正压情况下,器件铁电层极化值(p

r+

)与循环次数的对应关系曲线,拟合曲线b2表示加负压情况下,器件铁电层极化值(p

r-)与循环次数的对应关系曲线。

56.由图1可知,现有电容型锗基铁电存储器件的耐久性在小电压(如e

max

=2.3mv/cm)下可达到10的5次方,在大电压(如e

max

=3.1mv/cm)下仅可达到10的3次方。这远远无法达到存储器正常使用的年限。发明人考虑过采用在界面处形成稳定的二氧化锗(geo2)的方案,然而geo2高温易分解,因此对整体的工艺温度要求十分严格,且geo2不参与铁电材料翻转过程中。另外,发明人也考虑过其他氧化物如三氧化二铝(al2o3),然而al2o3等效氧化层厚度过大,分压严重,作为插层影响铁电极化翻转,因此不利于选择其为提高耐久性的方法。在此基础上,发明人研究发现,氧化锆作为一种反铁电材料,可以在后续高温退火过程中,结晶扩散参与铁电翻转过程,又能阻隔ge与铁电材料的接触,降低漏电,因此是改进锗基铁电器件耐久性的有效方法。

57.基于此,本说明书实施例提供了一种铁电存储器件及其制造方法,通过在锗衬底与铁电层之间增设一层氧化锆层,阻断锗衬底与铁电层的接触,即隔离锗与铁电材料,以达到降低锗与铁电材料界面处陷阱,减小漏电的效果,使器件具备良好的抗疲劳能力,有效地提升了锗基铁电器件的耐久性。

58.下面就对本说明书提供的具体实施例进行详细说明。

59.第一方面,本说明书一实施例提供了一种铁电存储器件,如图2所示,该铁电存储器件10为电容型铁电器件,包括:依次层叠设置的锗衬底101、氧化锆层102(如图2中的棱形格填充区域)、铁电层103以及上电极104。

60.例如,锗衬底101可以是经过预处理的高掺p型锗衬底101。例如,预处理过程可以包括:将hf酸1:50漂洗30秒以上,5分钟以下,随后用去离子水处理衬底,去除残留的氢氟酸,接着,用气枪把水渍去掉。这样可以达到去除衬底表面残留氧化物以及有机物的效果,有利于保证器件性能。

61.氧化锆层102设置在锗衬底101与铁电层103之间,用于阻断锗衬底101与铁电层103的接触,即隔离锗与铁电材料,以达到降低锗与铁电材料界面处陷阱,减小漏电的效果。氧化锆层102中氧元素比例不同将导致后续铁电性能不同,只要可以阻断锗与铁电层103接触即可。在一种可选的实施方式中,氧化锆层102为二氧化锆(zro2)层。二氧化锆可参与铁电极化翻转,保证不会损失过多的极化值,能够在达到较好的阻断效果同时保证后续铁电性能。例如,可以通过在原子层沉积或溅射等膜层制备工艺沉积氧化锆层102的过程中,控制通氧量,以形成稳定的二氧化锆层,具体工艺参数可以预先根据多次试验确定。

62.在一种可选的实施方式中,氧化锆层102的厚度为0.5nm~5nm,在该厚度范围内能够在保证铁电层103性能的同时,达到较好的阻断效果。需要说明的是,氧化锆层102的过厚造成的分压会影响铁电层103性能,过薄无法达到较好的阻断效果。

63.铁电层103沉积在氧化锆层102上。例如,铁电层103厚度可以为5~30nm。铁电层103材料可以是hfzro或hfalo等铪基铁电材料,其中元素掺杂比例不同会导致铁电性能不同,且不同掺杂元素的厚度不同也会导致铁电性能不同。当然,铁电层103材料可以包括但不限于以上材料,同时具备铪基铁电性能的材料均可适用。

64.上电极104设置在铁电层103的远离锗衬底101的表面。例如,上电极104的厚度可以为10nm~100nm。其中电极材料可以是tin,pd,pt,w,cu,ag或者au等导电材料。

65.第二方面,本说明书一实施例提供了一种铁电存储器件,如图3所示,该铁电存储器件20为晶体管型铁电器件,包括:锗衬底201、源极202、漏极203、在源极202与漏极203之间延伸的沟道区204、氧化锆层205(如图3中的棱形格填充区域)、铁电层206以及栅极207。

66.例如,锗衬底201可以是锗晶圆片,或者,也可以是生在其他材料如硅基底上的锗材料层。具体实施时,为了去除衬底表面残留的氧化物和有机物,可以预先对锗衬底201进行预处理,例如,预处理过程可以参照第一方面实施例中的相应描述,此处不再赘述。

67.源极202和漏极203对应设置在锗衬底201上预定义的源极区域和漏极区域,源极202和漏极203之间延伸的区域即为沟道区204。例如,可以在栅极207定义之后,利用自对准离子注入,将离子注入预定义的源区和漏区,以形成源极202和漏极203。需要说明的是,此处离子注入只要使锗形成pn结即可,不局限于离子种类或功率等具体参数,若沟道区204的锗材料为p型,则注入离子为n型,反之,若沟道区204的锗材料为n型,则注入离子为p型。

68.氧化锆层205设置在沟道区204与铁电层206之间,用于阻断沟道区204锗材料与铁电层206的接触,即隔离锗与铁电材料,以达到降低锗与铁电材料界面处陷阱,减小漏电的效果。以p型锗衬底201为例,可以在p-ge上通过ald(atomic layer deposition,原子层沉积)或其他可沉积氧化锆的方法形成0.5nm~5nm的氧化锆层205。

69.需要说明的是,氧化锆层205中氧元素比例不同将导致后续铁电性能不同,只要可

以阻断锗与铁电层206接触即可。在一种可选的实施方式中,氧化锆层205为二氧化锆层,具体效果与实施过程可以参照第一方面实施例中的相应描述,此处不再赘述。

70.铁电层206位于在沟道区204上形成的氧化锆层205上方。例如,铁电层206的厚度范围以及具体材料可以参照上述第一方面实施例中的相关描述,此处不再赘述。

71.栅极207设置在所述铁电层206上。例如,栅极207可以是厚度为10nm~100nm的金属材料层。例如,金属材料可以是tin,pd,pt,w,cu,ag或者au等导电材料。

72.第三方面,本说明书一实施例提供了一种铁电存储器件的制造方法,应用于制造电容型铁电存储器件。如图4所示,该方法至少可以包括以下步骤s401至步骤s404。

73.步骤s401,提供锗衬底。

74.例如,可以采用高掺p型锗衬底。在一种可选的实施方式中,可以预先对锗衬底进行预处理,以去除表面残留的氧化物以及有机物,从而进一步保证器件性能。例如,预处理步骤可以包括:将hf酸1:50漂洗30秒以上,5分钟以下,随后用去离子水处理衬底,去除残留的氢氟酸,接着,用气枪把水渍去掉。然后,再执行步骤s402。

75.步骤s402,在锗衬底表面形成氧化锆层,用于阻断锗衬底与铁电层的接触。

76.具体来讲,如图5所示,可以在锗衬底101表面沉积氧化锆层102,沉积厚度为0.5nm~5nm,沉积温度为室温至300摄氏度皆可。例如,沉积工艺可以采用ald或其他可沉积氧化锆膜层的技术。

77.需要说明的是,氧元素比例不同将导致后续铁电性能不同,只要可以阻断锗与铁电层接触即可。在一种可选的实施方式中,可以在沉积氧化锆层的过程中,通过控制通氧量最终在锗衬底表面沉积得到较稳定的二氧化锆层,以在达到较好的阻断效果同时保证后续铁电性能。接着,再执行步骤s403。

78.步骤s403,在氧化锆层表面形成铁电层。

79.具体来讲,如图6所示,可以在氧化锆层102上沉积厚度为5~30nm的铁电材料,形成铁电层103。铁电层材料可以参照上述第一方面实施例中的相关描述,此处不再赘述。

80.进一步,再执行步骤s404。

81.步骤s404,在铁电层上形成上电极。

82.具体来讲,可以在铁电层103上沉积厚度为10nm~100nm的导电材料,形成上电极104,如图2所示。例如,电极材料可以是tin,pd,pt,w,cu,ag或者au等导电材料。

83.当然,在执行完步骤s404以后,还需要进行退火实验。例如,可以在氮气(n2)氛围下进行退火实验。需要说明的是,本实施例不局限于氮气快速热退火,任意可使铪基铁电具备铁电性的退火都包含在内。

84.第四方面,本说明书一实施例提供了一种铁电存储器件的制造方法,应用于制造晶体管型铁电存储器件。如图7所示,该方法至少可以包括以下步骤s701至步骤s703。

85.步骤s701,提供锗衬底。

86.例如,锗衬底201可以是锗晶圆片,或者,为了节约成本,锗衬底201也可以包括基底201a以及生长在基底201a上的锗材料层201b,如图8所示。例如,基底201a可以采用除锗以外的其他基底材料如硅基底。在一种可选的实施方式中,可以预先对锗衬底201进行预处理,以去除表面残留的氧化物以及有机物,从而进一步保证器件性能。例如,具体预处理步骤可以参照上述第三方面实施例中的相关描述,此处不再赘述。

87.步骤s702,在锗衬底上形成源极、漏极以及在源极和漏极之间延伸的沟道区。

88.步骤s703,在沟道区上依次层叠形成氧化锆层、铁电层以及栅极,其中,氧化锆层用于阻断沟道区锗材料与铁电层的接触。

89.需要说明的是,本实施例对步骤s702和步骤s703的先后顺序不做限定,可以先执行步骤s703,再执行步骤s702,或者,也可以先执行步骤s702,再执行步骤s703。也就是说,先长栅极再长源极和漏极,或者是,先长源极和漏极再长栅极皆可。

90.下面以先长栅极再长源极和漏极为例,对步骤s702和步骤s703的具体实施过程进行说明。

91.①

在锗衬底201表面先沉积氧化锆膜层215,如图9所示。例如,可以在p-ge上,通过ald或其他可沉积氧化锆膜的方法全层沉积0.5nm~5nm的氧化锆膜层215即界面层(il)。需要说明的是,氧化锆膜层215中氧元素比例不同将导致后续铁电性能不同,只要可以阻断锗与铁电层接触即可。在一种可选的实施方式中,氧化锆膜层215具体可以为二氧化锆膜层,其效果与实施过程可以参照第一方面实施例中的相应描述,此处不再赘述。

92.②

在氧化锆膜层215上沉积铁电材料膜层216,如图10所示。铁电材料膜层216的厚度和具体材料可以参照上述第一方面实施例中的相关描述,此处不再赘述。

93.③

在铁电材料膜层216上依次沉积10nm~100nm金属,得到栅极材料膜层217,如图11所示。栅极金属材料可以参照上述第二方面实施例中的相关描述,此处不再赘述。

94.④

利用光刻工艺以及刻蚀工艺对所沉积的膜层进行图案化处理,在锗衬底201表面预定义的栅极区域形成依次层叠的氧化锆层205、铁电层206以及栅极207,如图12所示。例如,可以分别采用电子束光刻(electron beam lithography,ebl)工艺和反应离子刻蚀(reactive ion etching,rie)工艺图案化栅极区域。

95.⑤

再对锗衬底201表面预定义的源极区域和漏极区域进行离子注入,形成源极202、漏极203以及在源极202和漏极203之间延伸的沟道区204。例如,可以在栅极定义之后,利用自对准离子注入,预定义的源区和漏区,以形成源极202和漏极203。需要说明的是,此处离子注入只要使锗形成pn结即可,不局限于离子种类或功率等具体参数。

96.⑥

在完成栅极207、源极202和漏极203的制备以后,还需要进行退火实验。例如,可以在氮气(n2)氛围下进行退火实验。需要说明的是,本实施例不局限于氮气快速热退火,任意可使铪基铁电具备铁电性的退火都包含在内。

97.可以理解的是,若需要先长源极202和漏极203再长栅极207,可以将上述步骤

⑤

与步骤

①

、

②

、

③

这三步进行顺序调换即可,本实施例不再详述。

98.进一步地,为了验证本技术方案的效果,发明人还进行了对比试验。图13中的(a)图示出了现有电容型锗基铁电存储器件的耐久性试验结果,图13中的(b)图示出了增设二氧化锆层后的器件耐久性试验结果,其中,横坐标为器件的循环次数(number of cycles),纵坐标为器件铁电层的极化值(polarization,单位为μc/cm2),也可以用pr表示。

99.具体来讲,分别对现有器件和增设二氧化锆层后的器件施加相同大小的操作电压(如3v),测得不同器件循环次数下对应的铁电层极化值。其中,(a)图中的拟合曲线c1和(b)图中的拟合曲线d1均为在施加3v正向操作电压时,铁电层极化值与器件循环次数之间的对应关系曲线。(a)图中的拟合曲线c2和(b)图中的拟合曲线d2均为在施加3v负向操作电压时,铁电层极化值与器件循环次数之间的对应关系曲线。

100.对比(a)和(b)图可以看出,(a)图中循环次数达到10的4次方后器件击穿,无法读取pr值,(b)图中循环次数达到10的6次方之前还可以读取pr值,也就是说,在增设二氧化锆层后,同等操作电压(3v)下,器件耐久性提高了两个数量级,即由10的4次方击穿,到10的6次方击穿。且极化值没有十分明显的下降,可以保证正常的读写窗口。说明本说明书提供的技术方案可有效提升锗基铁电器件的耐久性,增加器件的抗疲劳特性。

101.由此可以得到,由于下界面即锗材料与铁电层界面处容易产生缺陷,器件在循环过程中,缺陷捕获导致器件耐久性不好,易击穿,达不到存储器使用的年限。插入二氧化锆层后可以改善界面,减少缺陷的产生并降低漏电,因而耐久性可得到相应的提升。另外,二氧化锆层具有铁电性,因此极化值不会有明显的下降。

102.综上所述,本说明书实施例提供的铁电存储器件及其制造方法,通过在铁电层沉积之前沉积合适厚度的氧化锆界面层,阻断锗衬底与铁电层的接触,以达到减少锗与铁电材料界面处缺陷的产生,降低漏电,提高锗基铁电器件的耐久性,从而有利于保证器件在循环过程中,具有良好的读写能力和较低的误码率。并且,采用二氧化锆层作为界面层,二氧化锆可参与铁电极化翻转,从而保证铁电层不会损失过多的极化值,有利于在保证铁电层性能的同时,提高锗基铁电器件性能的耐久性。

103.需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

104.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

105.尽管已描述了本说明书的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本说明书范围的所有变更和修改。

106.显然,本领域的技术人员可以对本说明书进行各种改动和变型而不脱离本说明书的精神和范围。这样,倘若本说明书的这些修改和变型属于本说明书权利要求及其等同技术的范围之内,则本说明书也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1