半导体结构的制作方法及半导体结构与流程

本公开涉及半导体,尤其涉及一种半导体结构的制作方法及半导体结构。

背景技术:

1、目前,用于逻辑电路的半导体结构简单,功能单一,使得实现“与”、“或”等逻辑功能时,需要用到更多的半导体器件,且接触点较多,影响芯片的制作效率。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、本公开提供一种半导体结构的制作方法及半导体结构。

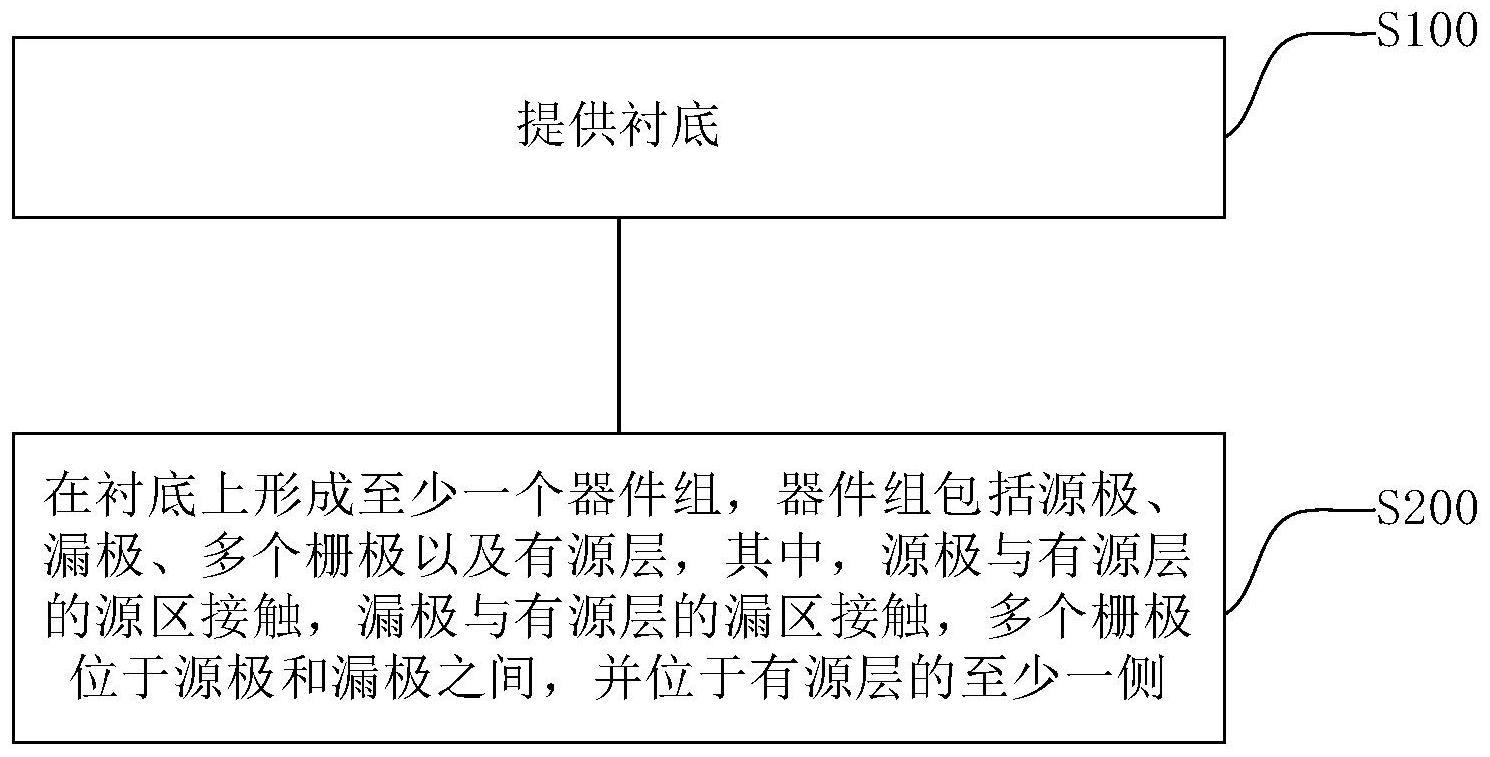

3、本公开的第一方面提供一种半导体结构的制作方法,所述半导体结构的制作方法包括:

4、提供衬底;

5、在所述衬底上形成至少一个器件组,所述器件组包括源极、漏极、多个栅极以及有源层,其中,所述源极与所述有源层的源区接触,所述漏极与所述有源层的漏区接触,所述多个栅极位于所述源极和所述漏极之间,并位于所述有源层的至少一侧。

6、在一些实施例中,所述在所述衬底上形成至少一个器件组包括:

7、在所述衬底的第一区域形成所述多个栅极;

8、形成第一栅介质层,所述第一栅介质层覆盖所述多个栅极以及所述衬底暴露的表面;

9、在所述第一栅介质层上形成源极和漏极;

10、形成有源层,所述有源层覆盖所述源极、所述漏极以及所述第一栅介质层暴露的表面。

11、在一些实施例中,所述多个栅极沿第一方向排布,形成的所述器件组包括或门电路,所述在所述第一栅介质层上形成源极和漏极,包括:

12、在所述第一栅介质层的第二区域形成源极,并在所述第一栅介质层的第三区域形成漏极,所述第二区域位于所述第一区域的第二方向的一侧,所述第三区域位于所述第一区域的第二方向的另一侧,所述第二方向与所述第一方向垂直且与所述衬底的顶面平行。

13、在一些实施例中,所述多个栅极沿第一方向排布,形成的所述器件组包括与门电路,所述在所述第一栅介质层上形成源极和漏极,包括:

14、在所述第一栅介质层的第二区域形成源极,并在所述第一栅介质层的第三区域形成漏极,所述第二区域位于所述第一区域的第一方向的一侧,所述第三区域位于所述第一区域的第一方向的另一侧。

15、在一些实施例中,在所述第一栅介质层上形成源极和漏极,包括:

16、在所述第一栅介质层上形成第一金属材料层;

17、平坦化所述第一金属材料层,并暴露出所述第一栅介质层中与所述第一区域对应的部分,保留的所述第一金属材料层构成所述源极和所述漏极。

18、在一些实施例中,所述多个栅极包括第一栅极和第二栅极,形成的所述器件组包括或门电路,所述在所述衬底上形成至少一个器件组,包括:

19、在所述衬底的第四区域形成第一栅极;

20、形成第一栅介质层,所述第一栅介质层覆盖所述第一栅极以及所述衬底暴露的表面;

21、在所述第一栅介质层上形成源极和漏极,所述源极和所述漏极沿第一方向分设在所述第一栅极的两侧;

22、形成有源层,所述有源层覆盖所述源极、所述漏极以及所述第一栅介质层暴露的表面;

23、形成覆盖所述有源层的第二栅介质层;

24、在所述第二栅介质层的第五区域形成第二栅极,所述第四区域和所述第五区域位置对应。

25、在一些实施例中,所述在所述第一栅介质层上形成源极和漏极,包括:

26、在所述第一栅介质层上形成第一金属材料层;

27、平坦化所述第一金属材料层,并暴露出所述第一栅介质层中与所述第四区域对应的部分,保留的所述第一金属材料层构成所述源极和所述漏极。

28、在一些实施例中,所述有源层的材料包括铟镓锌氧化物、铟锌氧化物、氧化铟锡。

29、本公开实施例的第二方面提供一种半导体结构,所述半导体结构包括:

30、衬底;

31、器件组,所述器件组设置于所述衬底上,所述器件组包括源极、漏极、多个栅极以及有源层,其中,所述源极与所述有源层的源区接触,所述漏极与所述有源层的漏区接触,所述多个栅极位于所述源极和所述漏极之间,并位于所述有源层的至少一侧。

32、在一些实施例中,所述多个栅极沿第一方向排布,所述多个栅极设置于所述衬底的第一区域,所述器件组包括或门电路,所述半导体结构还包括:

33、第一栅介质层,覆盖所述多个栅极以及所述衬底暴露的表面;

34、所述源极设置于所述第一栅介质层的第二区域上,所述漏极设置于所述第一栅介质层的第三区域,所述第二区域位于所述第一区域的第二方向的一侧,所述第三区域位于所述第一区域的第二方向的另一侧,所述第二方向与所述第一方向垂直且与所述衬底的顶面平行,所述有源层覆盖所述栅极、所述源极以及所述第一栅介质层暴露的表面。

35、在一些实施例中,所述栅极在所述第一方向上的尺寸小于所述第二方向上的尺寸。

36、在一些实施例中,所述多个栅极包括第一栅极和第二栅极,所述源极在所述第一方向上的尺寸大于所述第一栅极与所述第二栅极之间的距离;

37、所述漏极在所述第一方向上的尺寸大于所述第一栅极与所述第二栅极之间的距离。

38、在一些实施例中,所述多个栅极沿第一方向排布,所述多个栅极设置于所述衬底的第一区域,所述器件组包括与门电路,所述半导体结构还包括:

39、第一栅介质层,覆盖所述多个栅极以及所述衬底暴露的表面;

40、所述源极设置于所述第一栅介质层的第二区域上,所述漏极设置于所述第一栅介质层的第三区域上,所述第二区域位于所述第一区域的第一方向的一侧,所述第三区域位于所述第一区域的第一方向的另一侧,所述有源层覆盖所述栅极、所述源极以及所述第一栅介质层暴露的表面。

41、在一些实施例中,所述栅极在所述第一方向上的尺寸大于第二方向上的尺寸,所述第二方向与所述第一方向垂直且与所述衬底的顶面平行。

42、在一些实施例中,所述多个栅极包括第一栅极和第二栅极,所述源极在第二方向上的尺寸的大于所述第一栅极在所述第二方向上的尺寸,且大于所述第二栅极在所述第二方向上的尺寸,所述第二方向与所述第一方向垂直且与所述衬底的顶面平行;

43、所述漏极在所述第二方向上的尺寸大于所述第一栅极在所述第二方向上的尺寸,且大于所述第二栅极在所述第二方向上的尺寸。

44、在一些实施例中,所述多个栅极包括第一栅极和第二栅极,所述第一栅极设置于所述衬底的第四区域,所述器件组包括或门电路,所述半导体结构还包括:

45、第一栅介质层,覆盖所述第一栅极以及所述衬底暴露的表面,所述源极和漏极设置于所述第一栅介质层上并沿第一方向分设在所述第一栅极的两侧,所述有源层覆盖所述栅极、所述源极以及所述第一栅介质层暴露的表面;

46、第二栅介质层,覆盖所述有源层,所述第二栅极设置于所述第二栅介质层的第五区域,所述第四区域与所述第五区域位置对应。

47、在一些实施例中,所述第一栅极和所述第二栅极在第一方向上的尺寸大于在第二方向上的尺寸,所述第二方向与所述第一方向且与所述衬底的顶面平行。

48、在一些实施例中,所述源极在第二方向上的尺寸的大于所述第一栅极在所述第二方向上的尺寸,且大于所述第二栅极在所述第二方向上的尺寸,所述第二方向与所述第一方向垂直且与所述衬底的顶面平行。

49、本公开实施例所提供的半导体结构的制作方法及半导体结构中,通过在衬底上形成源极、漏极、多个栅极和有源层,且多个栅极位于源极和漏极之间并位于有源层的至少一侧,使得多个栅极以“串联”或“并联”的方式设置在源极和漏极之间,进而能够通过多个栅极结构控制同一组源极和漏极之间电流的导通和断开,实现“与”、“或”等逻辑电路的基础上,减少接触点,增加了集成度。。

50、在阅读并理解了附图和详细描述后,可以明白其他方面。

- 还没有人留言评论。精彩留言会获得点赞!