一种MCP-PMT读出电路

一种mcp-pmt读出电路

技术领域

1.本发明涉及mcp-pmt读出电路领域,特别是涉及一种低串扰mcp-pmt读出电路。

背景技术:

2.微通道板光电倍增管(mcp-pmt)是光电倍增管(pmt)的一种,与传统光电倍增管不同的是它使用微通道板(mcp)代替了一级级离散分布的打拿级,有着非常快的时间响应,另外其还有结构紧凑、增益高、位置分辨高、抗磁场等特性。因为mcp-pmt的优秀性能,使其在许多领域得到了广泛的应用:粒子物理实验、医学成像、国防安全等等。

3.根据阳极设计不同,mcp-pmt可分为多阳极型和单阳极型。多阳极型mcp-pmt不仅拥有单阳极mcp-pmt的所有优点,还多了位置灵敏的特性,更是成为了研究和应用的热点。然而多阳极mcp-pmt的使用一直存在一个普遍的困扰——串扰、振铃现象。串扰表现为当一个通道探测光子产生信号时,其它通道无光子也能出现信号(串扰),形状像真实信号的微分,极性与信号反相。振铃表现为一个通道探测光子产生信号的后沿存在一个衰减正弦波的振铃,而且会感应出现在所有通道上。值得注意的是,并不仅仅是光激发的信号会有串扰、振铃现象,避光环境下热噪声产生的信号也存在。当多个像素同时有信号时,感应出的串扰、振铃的幅度会叠加。这些性质导致串扰、振铃的现象影响信号形状,产生假信号,使mcp-pmt的优秀性能大打折扣。

4.现有技术的技术方案:以型号为hamamatsu sl10的mcp-pmt串扰压制技术为例,日本名古屋大学物理系和滨松公司电子管部联合研究了一种分割mcp的方法进行串扰压制。如图1所示,具体方法是将第二级mcp分割成与阳极一一对应的部分,每个分部设置电极,在分压电路上对每个mcp分部电极以及对应的阳极电极分开提供电压。串幅比下降了2倍(15%降至7%),振铃现象几乎消失。然而分割第二级mcp的方法针对阳极数量较少、阳极感应面积较大的mcp-pmt可以实现,但是对于阳极数量增加至几十上百、阳极感应面积小的mcp-pmt应用起来非常困难,所以该分割法应用受限。另外,该分割法虽然将串幅比降低至7%,但是在大信号或者多阳极着火的情况下,串扰现象仍然不可忽略,所以串幅比仍然较高,影响mcp-pmt的性能。针对上述问题,本发明提出一种mcp-pmt读出电路。

技术实现要素:

5.本发明的目的是提供一种mcp-pmt读出电路,适用于多阳极mcp-pmt,能够在读取mcp-pmt信号时,最大程度的避免串扰、振铃的现象,提高mcp-pmt的性能,使得mcp-pmt的性能更稳定。

6.为实现上述目的,本发明提供了如下方案:

7.一种mcp-pmt读出电路,包括mcp-pmt插座芯片u1、高压插座芯片u2和信号插座引脚单元u3;

8.所述mcp-pmt插座芯片u1包括第一k引脚、第一in1引脚、第一out1引脚、第一in2引脚、第一out2引脚;

9.所述mcp-pmt插座芯片u1还包括第一a1引脚,第一a2引脚,...,第一ai引脚,...,第一a16引脚;

10.所述高压插座芯片u2包括第二k引脚、第二in1引脚、第二out1引脚、第二in2引脚、第二out2引脚和gnd引脚;

11.所述信号插座引脚单元u3包括第二a1引脚,第二a2引脚,...,第二ai引脚,...,第二a16引脚;

12.所述第一k引脚与所述第二k引脚连接;所述第一in1引脚与所述第二in1引脚连接,所述第一out1引脚与所述第二out1引脚连接,所述第一in2引脚与所述第二in2引脚连接;所述第一out2引脚与所述第二out2引脚连接;所述第一out2引脚还与mcp-pmt的输出电极连接;所述gnd引脚接地;

13.所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接;

14.所述mcp-pmt插座芯片u1,用于读取所述mcp-pmt的输出电极的输出信号;

15.所述高压插座芯片u2,用于接受mcp-pmt分压电路提供的电压为所述mcp-pmt的各电极供电;

16.所述信号插座引脚单元u3,用于接收所述mcp-pmt的输出电极的输出信号并传输至前端电路。

17.可选的,所述第一out2引脚包括out2-1引脚、out2-2引脚、out2-3引脚和out2-4引脚;

18.所述out2-1引脚、所述out2-2引脚、所述out2-3引脚和所述out2-4引脚均与所述第二out2引脚连接。

19.可选的,读出电路还包括去耦电容c1、去耦电容c2、去耦电容c3和去耦电容c4;

20.所述去耦电容c1的一端连接所述out2-4引脚,所述去耦电容c1的另一端接地;

21.所述去耦电容c2的一端连接所述out2-3引脚,所述去耦电容c2的另一端接地;

22.所述去耦电容c3的一端连接所述out2-2引脚,所述去耦电容c3的另一端接地;

23.所述去耦电容c4的一端连接所述out2-1引脚,所述去耦电容c4的另一端接地。

24.可选的,读出电路还包括去耦电容c5、去耦电容c6、去耦电容c7和去耦电容c8;

25.所述去耦电容c5的一端连接于所述第一out2引脚和所述第二out2引脚的连接线上,所述去耦电容c5的另一端连接于所述第一in2引脚和所述第二in2引脚的连接线上;

26.所述去耦电容c6的一端连接于所述第一in2引脚和所述第二in2引脚的连接线上,所述去耦电容c6的另一端连接于所述第一out1引脚和所述第二out1引脚的连接线上;

27.所述去耦电容c7的一端连接于所述第一out1引脚和所述第二out1引脚的连接线上,所述去耦电容c7的另一端连接于所述第一in1引脚和所述第二in1引脚的连接线上;

28.所述去耦电容c8的一端连接于所述第一in1引脚和所述第二in1引脚的连接线上,所述去耦电容c8的另一端连接于所述第一k引脚和所述第二k引脚的连接线上。

29.可选的,所述去耦电容c1、所述去耦电容c2、所述去耦电容c3和所述去耦电容c4的电容值相同;所述去耦电容c5、所述去耦电容c6、所述去耦电容c7和所述去耦电容c8的电容值相同;所述去耦电容c1的电容值与所述去耦电容c5的电容值不同。

30.可选的,所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引

脚一一对应连接的各信号连接线上分别串联有阻尼电阻。

31.可选的,所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接的各信号连接线上分别连接有保护二极管,且每一所述保护二极管的阴极连接于对应的连接线上,每一所述保护二极管的阳极均接地。

32.可选的,读出电路设置为pcb板结构;所述pcb板结构从上至下依次包括top层、gnd1层、sig1层、sig2层、gnd2层和bottom层;

33.在所述top层上设置所述mcp-pmt插座芯片u1和所述高压插座芯片u2之间供电电极走线的一部分;

34.在所述bottom层上设置所述mcp-pmt插座芯片u1和所述高压插座芯片u2之间供电电极走线的另一部分;所述供电电极走线包括所述第一k引脚和所述第二k引脚的供电连接线、所述第一in1引脚和所述第二in1引脚的供电连接线、所述第一out1引脚和所述第二out1引脚的供电连接线、所述第一in2引脚和所述第二in2引脚的供电连接线以及所述第一out2引脚和所述第二out2引脚的供电连接线;

35.在所述sig1层上设置所述mcp-pmt插座芯片u1和所述信号插座引脚单元u3之间输出信号走线的一部分;

36.在所述sig2层上设置所述mcp-pmt插座芯片u1和所述信号插座引脚单元u3之间输出信号走线的另一部分;所述输出信号走线包括所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接的信号连接线;

37.所述gnd1层和所述gnd2层为地平面。

38.可选的,所述输出信号走线中的相邻两个所述信号连接线设于不同层,同一层上的相邻两个所述信号连接线间隔设置。

39.可选的,所述信号插座引脚单元u3中的各引脚的邻边均为接地引脚。

40.根据本发明提供的具体实施例,本发明公开了以下技术效果:

41.本发明涉及一种mcp-pmt读出电路,包括mcp-pmt插座芯片u1、高压插座芯片u2和信号插座引脚单元u3;所述mcp-pmt插座芯片u1,用于读取所述mcp-pmt的输出电极的输出信号;所述高压插座芯片u2,用于接受mcp-pmt分压电路提供的电压为所述mcp-pmt的各电极供电;所述信号插座引脚单元u3,用于接收所述mcp-pmt的输出电极的输出信号并传输至前端电路。本发明的读出电路,适用于多阳极mcp-pmt,能够在读取mcp-pmt信号时,最大程度的避免串扰、振铃的现象,提高mcp-pmt的性能,使得mcp-pmt的性能更稳定。

附图说明

42.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

43.图1为现有技术中mcp-pmt结构的分割示意图;

44.图2为本发明实施例1提供的一种mcp-pmt读出电路原理图;

45.图3为本发明实施例1提供的读出电路pcb板示意图;

46.图4为本发明实施例1提供的读出电路pcb板的top层示意图;

47.图5为本发明实施例1提供的读出电路pcb板的gnd1层示意图;

48.图6为本发明实施例1提供的读出电路pcb板的sig1层示意图;

49.图7为本发明实施例1提供的读出电路pcb板的sig2层示意图;

50.图8为本发明实施例1提供的读出电路pcb板的gnd2层示意图;

51.图9为本发明实施例1提供的读出电路pcb板的bottom层层示意图;

52.图10为本发明实施例1提供的激励通道与其它通道的串扰波形图;

53.图11为本发明实施例1提供的仿真中串幅比随信号幅度变化关系图;

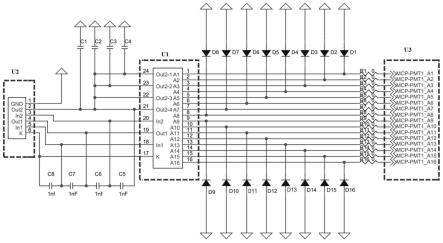

54.图12为本发明实施例1提供的仿真中振幅比随信号幅度变化关系图;

55.图13为本发明实施例1提供的未使用和使用读出电路时的mcp-pmt的信号和串扰振铃波形图。

具体实施方式

56.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

57.本发明的目的是提供一种mcp-pmt读出电路,适用于多阳极mcp-pmt,能够在读取mcp-pmt信号时,最大程度的避免串扰、振铃的现象,提高mcp-pmt的性能,使得mcp-pmt的性能更稳定。

58.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

59.实施例1

60.如图2所示,本实施例提供一种mcp-pmt读出电路,包括mcp-pmt插座芯片u1、高压插座芯片u2和信号插座引脚单元u3;

61.所述mcp-pmt插座芯片u1包括第一k引脚、第一in1引脚、第一out1引脚、第一in2引脚、第一out2引脚;对应图2中mcp-pmt插座芯片u1中的k、in1、out1、in2、out2和gnd。

62.所述mcp-pmt插座芯片u1还包括第一a1引脚,第一a2引脚,...,第一ai引脚,...,第一a16引脚;对应图2中mcp-pmt插座芯片u1中的a1至a16。

63.所述高压插座芯片u2包括第二k引脚、第二in1引脚、第二out1引脚、第二in2引脚、第二out2引脚和gnd引脚,对应图2中高压插座芯片u2中的k、in1、out1、in2、out2和gnd。

64.所述信号插座引脚单元u3包括第二a1引脚,第二a2引脚,...,第二ai引脚,...,第二a16引脚,对应图2中的mcp-pmt1-a1至mcp-pmt1-a16。

65.其中,所述第一k引脚与所述第二k引脚连接;所述第一in1引脚与所述第二in1引脚连接,所述第一out1引脚与所述第二out1引脚连接,所述第一in2引脚与所述第二in2引脚连接;所述第一out2引脚与所述第二out2引脚连接;所述第一out2引脚还与mcp-pmt的输出电极连接;所述gnd引脚接地;

66.由于结构的原因,将第一out2引脚分为了四个同电位的引脚,即所述第一out2引脚包括out2-1引脚、out2-2引脚、out2-3引脚和out2-4引脚;其中,所述out2-1引脚、所述out2-2引脚、所述out2-3引脚和所述out2-4引脚均与所述第二out2引脚连接。

67.那么第一out2引脚与mcp-pmt的输出电极连接实际上为所述out2-1引脚、所述out2-2引脚、所述out2-3引脚和所述out2-4引脚分别与mcp-pmt的四个输出电极连接。这样mcp-pmt通过mcp-pmt插座芯片u1与该读出电路相连。

68.为了保证mcp-pmt的各输出电极的阳极表面的感应电荷在其他阳极感应出串扰,可以在每一输出电极串联一去耦电容,这样使得第二级mcp表面的感应电荷第一时间被去耦电容储存。所以,读出电路还包括去耦电容c1、去耦电容c2、去耦电容c3和去耦电容c4;

69.所述去耦电容c1的一端连接所述out2-4引脚,所述去耦电容c1的另一端接地;

70.所述去耦电容c2的一端连接所述out2-3引脚,所述去耦电容c2的另一端接地;

71.所述去耦电容c3的一端连接所述out2-2引脚,所述去耦电容c3的另一端接地;

72.所述去耦电容c4的一端连接所述out2-1引脚,所述去耦电容c4的另一端接地。

73.对于所述去耦电容c1、所述去耦电容c2、所述去耦电容c3和所述去耦电容c4的电容值相同,可以将其电容值可以设置为470pf。

74.同样的为了避免高压插座芯片u2和mcp-pmt插座芯片u1的其他引脚的连接线之间的感应电荷的互相影响,可以要求读出电路还包括去耦电容c5、去耦电容c6、去耦电容c7和去耦电容c8;

75.所述去耦电容c5的一端连接于所述第一out2引脚和所述第二out2引脚的连接线上,所述去耦电容c5的另一端连接于所述第一in2引脚和所述第二in2引脚的连接线上;

76.所述去耦电容c6的一端连接于所述第一in2引脚和所述第二in2引脚的连接线上,所述去耦电容c6的另一端连接于所述第一out1引脚和所述第二out1引脚的连接线上;

77.所述去耦电容c7的一端连接于所述第一out1引脚和所述第二out1引脚的连接线上,所述去耦电容c7的另一端连接于所述第一in1引脚和所述第二in1引脚的连接线上;

78.所述去耦电容c8的一端连接于所述第一in1引脚和所述第二in1引脚的连接线上,所述去耦电容c8的另一端连接于所述第一k引脚和所述第二k引脚的连接线上。

79.其中,所述去耦电容c1的电容值与所述去耦电容c5的电容值不同。所述去耦电容c5、所述去耦电容c6、所述去耦电容c7和所述去耦电容c8的电容值相同,电容值可以设置为1nf。本实施例中设置的所有去耦电容的作用是为了存储堆积电荷。

80.由于前端电路的负载不同,为了灵活调节电路动态响应状态,可以在读出电路中设置阻尼电阻,即所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接的各信号连接线上分别串联有阻尼电阻,对应的是图2中r1至r16。mcp-pmt信号传输至前端电路经过阻尼电阻,阻尼电阻阻值50欧姆,使得信号至负载的回路动态响应恰好为临界阻尼状态,消除振铃现象。

81.考虑到mcp-pmt的大信号可能会打坏负载电路,为了保护负载电路(前端电路),可以在读出电路中设置保护二极管,所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接的各信号连接线上分别连接有保护二极管,且每一所述保护二极管的阴极连接于对应的连接线上,每一所述保护二极管的阳极均接地。对应图2中的d1至d16。

82.所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接;

83.所述mcp-pmt插座芯片u1,用于读取所述mcp-pmt的输出电极的输出信号;

84.所述高压插座芯片u2,用于接受mcp-pmt分压电路提供的电压为所述mcp-pmt的各电极供电,即为mcp-pmt供电。

85.高压插座为母插座,分压电路有匹配的公插头,两者结合完成连接。

86.所述信号插座引脚单元u3,用于接收所述mcp-pmt的输出电极的输出信号并传输至前端电路,即将mcp-pmt各个阳极的信号传输至前端电路。

87.信号插座为公插头,前端电路上有匹配的母插座,两者结合完成连接。

88.可以将本实施例中的读出电路设置为pcb板结构,其中,如图3至9所示。读出电路的pcb板结构从上至下依次包括top层、gnd1层、sig1层、sig2层、gnd2层和bottom层;

89.在所述top层上设置所述mcp-pmt插座芯片u1和所述高压插座芯片u2之间供电电极走线的一部分;

90.在所述bottom层上设置所述mcp-pmt插座芯片u1和所述高压插座芯片u2之间供电电极走线的另一部分;所述供电电极走线包括所述第一k引脚和所述第二k引脚的供电连接线、所述第一in1引脚和所述第二in1引脚的供电连接线、所述第一out1引脚和所述第二out1引脚的供电连接线、所述第一in2引脚和所述第二in2引脚的供电连接线以及所述第一out2引脚和所述第二out2引脚的供电连接线;

91.在所述sig1层上设置所述mcp-pmt插座芯片u1和所述信号插座引脚单元u3之间输出信号走线的一部分;

92.在所述sig2层上设置所述mcp-pmt插座芯片u1和所述信号插座引脚单元u3之间输出信号走线的另一部分;所述输出信号走线(阳极读出信号的走线)包括所述第一a1引脚至所述第一a16引脚与所述第二a1引脚至所述第二a16引脚一一对应连接的信号连接线;

93.信号连接线50欧姆阻抗,圆弧蛇形走线减小阻抗不连续点。降低了分布电容电感比,改善了振铃现象。线间距大于3倍线宽,信号插座的每个信号引脚的邻边都为地引脚,相邻信号线放置在不同层间隔排列,降低通道间的串扰。

94.所述gnd1层和所述gnd2层为地平面。在所述gnd1层和所述gnd2层上挖孔,通过挖孔将各引脚或各器件实现接地。如高压插座芯片u2中的gnd引脚通过挖孔与gnd1层或gnd2层连接;去耦电容的接地端通过挖孔与gnd1层或gnd2层连接实现接地;保护二极管的阳极通过挖孔与gnd1层或gnd2层连接实现接地。为了保证读出信号不受外界和高压走线的干扰,也为了保证高压不会击穿gnd1层或gnd2层,将gnd1层或gnd2层的挖空部分不对应设置。

95.所述输出信号走线中的相邻两个所述信号连接线设于不同层,换层走线附近加地过孔,减小回流面积,避免电荷积累。同一层上的相邻两个所述信号连接线间隔设置。

96.所述信号插座引脚单元u3中的各引脚的邻边均为接地引脚,即信号插座引脚单元u3中的各引脚的邻边通过挖孔与所述gnd1层或所述gnd2层连接实现接地。

97.设计pcb板时,围绕第二级mcp四周一共含4个输出电极,在每一个输出电极串联去耦电容c1-c4到地,容值为470pf。电容在pcb板上围绕mcp-pmt均匀分布,使得第二级mcp表面的感应电荷第一时间被去耦电容储存,避免其在其它阳极感应出串扰。

98.本实施例中的读出电路的pcb板结构可以同时对两支mcp-pmt进行信号读出,这种情况下的在同一pcb板上设置两组读出电路。

99.对于分割分压电路和信号读出电路,将mcp-pmt分压电路分割出去使用另一块pcb板,各电级分压通过高压插座芯片u2引入到读出电路,隔断了分压电路上电磁场的干扰。

100.本实施例中,读出电路由三个部分组成:(a)高压插座和去耦电容c1-c8,用于接受分压电路提供的电压分配至mcp-pmt各个电极,即为mcp-pmt供电,其中去耦电容用于存储堆积电荷;(b)mcp-pmt插座,保护二极管d1-d16和阻尼电阻r1-r16,用于和mcp-pmt的电极和阳极连接,其中保护二极管用于防止mcp-pmt的大信号打坏负载电路,阻尼电阻用于调节电路动态响应状态;(c)信号插座,用于将mcp-pmt信号传输至前端电路。采用该电路读出的mcp-pmt信号将具有低串扰振铃、高时间分辨、高位置分辨等特点,保证mcp-pmt的性能的稳定性。因此在弱光探测、粒子种类区分、辐射粒子能量及分布成像等方面具有显著的优势。比如:(1)应用于高能物理实验上的粒子种类识别,如belleii实验上的top探测器,要求mcp-pmt信号具有高保真、低串扰、高信噪比等特点,基于本发明的读出电路完全满足实验需求,而且无需对mcp-pmt的内部结构做任何修改。(2)应用于稀有事例搜寻实验,如nist核反应堆的mtc探测器用于探测反中微子,使用本发明作为mcp-pmt的读出电路可以减少假信号,降低误触发。解决了多阳极型mcp-pmt有着非常快的时间响应、结构紧凑、增益高、位置分辨高、抗磁场等特性,但是其串扰振铃的现象使其性能大打折扣的问题,本实施例的读出电路解决了串扰振铃现象可以使其在许多领域的应用不再受限。

101.下面使用ads软件对本实施例的读出电路设计进行了仿真,图10(a)为对ch7通道设置激励信号,其余通道的串扰现象,ch7通道信号幅度为19mv,其它通道串扰幅度最大约为500uv,串幅比最大为2.6%。图10(b)为对ch6、7、10和11通道设置的激励信号,其它通道的串扰现象。4个信号通道同时给予幅度为19mv的激励,其它通道串扰幅度最大约为700uv,串幅比最大为3.6%。

102.应用在hamamatsu r10754型号的mcp-pmt上进行了验证测试,图11为串幅比随信号幅度变化关系,圆点为原始信号,方点为使用本发明的信号,从图中可以看出串幅比从12%降至4%。图12为振幅比随信号幅度变化关系,圆点为原始信号(改进前),方点为使用本发明的信号(改进后),从图中可以看出振幅比从15%降至5%。图13展示了mcp-pmt的信号和串扰振铃波形图,图13(a)为未使用读出电路时的mcp-pmt的信号和串扰振铃波形图;图13(b)为使用读出电路时的mcp-pmt的信号和串扰振铃波形图。signal表示mcp-pmt的信号波形,crosstalk为串扰振铃波形,使用本发明以后可以看到信号后沿不再有振铃现象,其他通道的串扰振铃幅度大大降低。

103.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1