半导体装置的制作方法

1.本发明涉及半导体装置。

背景技术:

2.作为微米波的高输出放大器,已知有将设有fet(field effect transistor:场效应晶体管)等晶体管的半导体芯片安装于封装的放大器。已知使用安装于封装内的电容性部件和接合线来形成放大器的输出匹配电路、视频旁通电路等无源电路(例如专利文献1~4、非专利文献1和2)。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2014-96497号公报

6.专利文献2:日本特表2006-501678号公报

7.专利文献3:欧洲专利申请公开第3273596号说明书

8.专利文献4:日本特开2018-101975号公报

9.非专利文献

10.非专利文献1:hussain ladhani et.al.“analysis of the baseband termination of high power rf transistors”2019 ieee/mtt-s international microwave symposium

11.非专利文献2:ning zhu et.al.“compact high-efficiency high-power wideband gan amplifier supporting 395mhz instantaneous bandwidth”2019 ieee/mtt-s international microwave symposium

12.在半导体芯片的输出焊盘与地之间将电感器和电容器串联连接的情况下,在基底基板上搭载电容性部件,使用接合线将电容性部件与半导体芯片的输出连接。然而,若试图增大电感,则接合线变长而封装会大型化。如专利文献1的例如图13那样,可以想到使用布线部件来形成电感器的一部分。然而,若将微带线等布线部件搭载于内部,则封装会大型化。此外,制造成本会增加。

技术实现要素:

13.本公开是鉴于上述问题而完成的,其目的在于进行小型化和低成本化。

14.本公开的一个实施方式是半导体装置,具备:半导体芯片,搭载于基底基板的上表面,具有输出焊盘;第一电容性部件,搭载于所述基底基板的上表面,一端电连接于所述基底基板;电介质的框体,设于所述基底基板上,包围所述半导体芯片和所述第一电容性部件;输出端子,设于所述框体上;布线图案,设于所述框体的上表面;第一接合线,将所述输出焊盘与所述输出端子电连接;第二接合线,将所述第一电容性部件的另一端与所述布线图案内的第一区域电连接;以及第三接合线,将所述输出焊盘与所述布线图案内的不同于所述第一区域的第二区域电连接。

15.本公开的一个实施方式是半导体装置,具备:半导体芯片,搭载于基底基板的上表面,具有输出焊盘;第一电容性部件,搭载于所述基底基板的上表面,一端电连接于所述基底基板;电介质的框体,设于所述基底基板上,包围所述半导体芯片和所述第一电容性部件;输出端子,设于所述框体上;布线图案,设于所述框体的上表面,在所述框体上与所述输出端子电连接;第一接合线,将所述输出焊盘与所述输出端子电连接;以及第二接合线,将所述第一电容性部件的另一端与所述布线图案的区域电连接。

16.发明效果

17.根据本公开,能进行小型化和低成本化。

附图说明

18.图1是具有实施例1的半导体装置的放大器的电路图。

19.图2是实施例1的半导体装置的电路图。

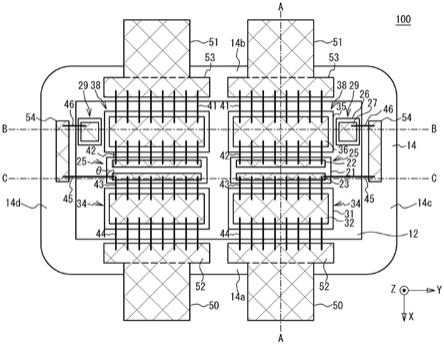

20.图3是实施例1的半导体装置的俯视图。

21.图4是图3的a-a剖视图。

22.图5是图3的b-b剖视图。

23.图6是图3的c-c剖视图。

24.图7是比较例1的半导体装置的俯视图。

25.图8是比较例2的半导体装置的俯视图。

26.图9是实施例1的变形例1的半导体装置的电路图。

27.图10是实施例1的变形例1的半导体装置的俯视图。

28.图11是实施例1的变形例2的半导体装置的俯视图。

29.图12是实施例1的变形例3的半导体装置的俯视图。

30.图13是实施例1的变形例4的半导体装置的俯视图。

31.图14是表示实施例1的变形例5中的vbw电路的电路图。

32.图15是表示实施例1的变形例6中的vbw电路的电路图。

33.图16是实施例1的变形例6的半导体装置的俯视图。

34.图17是表示实施例1的变形例7中的vbw电路的电路图。

35.图18是表示实施例1的变形例8中的vbw电路的电路图。

36.图19是实施例1的变形例8的半导体装置的俯视图。

37.附图标记说明

38.10:封装

39.12:基底基板

40.13a、13b:接合层

41.14:框体

42.14a~14d:边

43.16:盖

44.20:晶体管

45.21:半导体基板

46.22~24、27、28、32、33、36、37、72、73、76、82、84:电极

47.25:半导体芯片

48.26、31、35、71、75、78、81:电介质基板

49.29、34、38、74、80、90:电容性部件

50.41~49:接合线

51.50:输出引线

52.51:输入引线

53.52:输出图案

54.53:输入图案

55.54、79:布线图案

56.56:引线

57.60:vbw电路

58.61:内部输出匹配电路

59.62:外部输出匹配电路

60.63:内部输入匹配电路

61.64:外部输入匹配电路

62.65:输出负载

63.66:输入负载

64.70:电阻部件

65.77:布线部件

66.92、94:箭头

67.100~106、110、112:半导体装置。

具体实施方式

68.[本公开的实施方式的说明]

[0069]

首先,列举出本公开的实施方式的内容进行说明。

[0070]

(1)本公开的一个实施方式是半导体装置,具备:半导体芯片,搭载于基底基板的上表面,具有输出焊盘;第一电容性部件,搭载于所述基底基板的上表面,一端电连接于所述基底基板;电介质的框体,设于所述基底基板上,包围所述半导体芯片和所述第一电容性部件;输出端子,设于所述框体上;布线图案,设于所述框体的上表面;第一接合线,将所述输出焊盘与所述输出端子电连接;第二接合线,将所述第一电容性部件的另一端与所述布线图案内的第一区域电连接;以及第三接合线,将所述输出焊盘与所述布线图案内的不同于所述第一区域的第二区域电连接。由此,能进行小型化和低成本化。

[0071]

(2)优选的是,具备输入端子,该输入端子隔着所述半导体芯片设于与所述输出端子对置的所述框体上,电连接于所述半导体芯片的输入焊盘,所述第三接合线延伸的方向与所述输入端子、所述半导体芯片以及所述输出端子排列的方向的角度为30

°

以上。

[0072]

(3)优选的是,所述半导体芯片将高频信号放大并输出至所述输出焊盘,所述半导体芯片所放大的高频信号的频率下的所述第二接合线、所述第三接合线以及所述布线图案的合计的阻抗的绝对值大于与所述半导体芯片所放大的高频信号的带宽相当的频率下的所述第一电容性部件的阻抗的绝对值。

[0073]

(4)本公开的一个实施方式是半导体装置,具备:半导体芯片,搭载于基底基板的上表面,具有输出焊盘;第一电容性部件,搭载于所述基底基板的上表面,一端电连接于所述基底基板;电介质的框体,设于所述基底基板上,包围所述半导体芯片和所述第一电容性部件;输出端子,设于所述框体上;布线图案,设于所述框体的上表面,在所述框体上与所述输出端子电连接;第一接合线,将所述输出焊盘与所述输出端子电连接;以及第二接合线,将所述第一电容性部件的另一端与所述布线图案的区域电连接。

[0074]

(5)优选的是,所述半导体芯片将高频信号放大并输出至所述输出焊盘,所述半导体芯片所放大的高频信号的频率下的所述第二接合线和所述布线图案的合计的阻抗的绝对值大于与所述半导体芯片所放大的高频信号的带宽相当的频率下的所述第一电容性部件的阻抗的绝对值。

[0075]

(6)优选的是,具备输入端子,该输入端子设于所述框体上,与所述半导体芯片的输入焊盘电连接。

[0076]

(7)优选的是,具备外部端子,该外部端子与所述布线图案电连接,用于与外置电容性部件连接。

[0077]

(8)优选的是,所述第一接合线以不连接于搭载于所述基底基板上的其他的电容性部件的方式将所述输出焊盘与所述输出端子连接。

[0078]

(9)优选的是,具备第二电容性部件,该第二电容性部件搭载于所述基底基板的上表面,一端电连接于所述基底基板,所述第一接合线包括:第四接合线,将所述输出焊盘与所述第二电容性部件的另一端电连接;以及第五接合线,将所述第二电容性部件的另一端与所述输出端子电连接。

[0079]

[本公开的实施方式的详情]

[0080]

以下,参照附图对本公开的实施方式的半导体装置的具体例进行说明。需要说明的是,本公开并不限定于这些示例,而是由权利要求书示出,意图在于包括与权利要求书等同的含义和范围内的所有变更。

[0081]

[实施例1]

[0082]

图1是具有实施例1的半导体装置的放大器的电路图。如图1所示,放大器具备半导体装置100、外部输出匹配电路62以及外部输入匹配电路64。半导体装置100具备晶体管20、内部输出匹配电路61、内部输入匹配电路63以及vbw(video bandwidth:视频带宽)电路60。晶体管20例如为gan hemt(gallium nitride high electron mobility transistor:氮化镓高电子迁移率晶体管)或ldmos(laterally diffused metal oxide semiconductor:横向扩散金属氧化物半导体)。输入负载66经由外部输入匹配电路64、内部输入匹配电路63连接于晶体管20的栅极g。外部输入匹配电路64和内部输入匹配电路63使输入负载66与晶体管20的输入阻抗匹配。

[0083]

晶体管20的源极s接地。晶体管20的漏极d经由内部输出匹配电路61和外部输出匹配电路62连接于输出负载65。内部输出匹配电路61和外部输出匹配电路62使输出负载65与晶体管20的输出阻抗匹配。晶体管20的漏极d与内部输出匹配电路61之间的节点n1经由vbw电路60接地。vbw电路60具备串联连接于节点n1与地之间的电感器l1和电容器c1。

[0084]

图2是实施例1的半导体装置的电路图。如图2所示,半导体装置100具备封装(package)10。在封装10内搭载有晶体管20、内部输出匹配电路61、内部输入匹配电路63以

及vbw电路60。输出引线50和输入引线51将封装10内的电路连接于外部。内部输出匹配电路61是l-c-l的t型电路,具备电感器l11、l12以及电容器c11。内部输入匹配电路63是l-c-l的t型电路,具备电感器l21、l22以及电容器c21。

[0085]

vbw电路60是用于使vbw(即视频带宽)提高的电路。视频带宽被用作表示失真的频带的指标。若在vbw小的情况下测定出与放大器的带宽(例如400mhz)相当的双音(two-tone)信号的三阶互调失真(imd3:3rd order intermodulation distortion),则在低频侧的imd3分量和高频侧的imd3分量中,在信号强度上会产生差。若像这样在imd3产生非对称,则即使进行基于dpd(digital predistortion:数字预失真)的失真补偿,失真的改善量也会下降而无法得到充分的失真特性(例如参照非专利文献1)。作为产生该imd3的非对称性的原因,已知有在双音信号的差频分量中产生的二阶互调失真imd2分量。因此,通过设置vbw电路60来降低节点n1处的低频段的阻抗,由此视频带宽变大,imd2分量被抑制。由此,imd3的非对称得到改善,能通过dpd进行充分的失真补偿。

[0086]

电感器l1具有抑制放大器所放大的基波的高频信号(例如1ghz以上,例如1.8ghz或2.4ghz)经由电容器c1通向地的功能。因此,电感器l1具有在基波的频率频带中成为高阻抗这样的电感。电容器c1在与放大器所放大的高频信号的带宽相当的频率(例如0~400mhz)下成为低阻抗。因此,电容器c1具有大的电容值,从而大型化。

[0087]

图3是实施例1的半导体装置的俯视图。图4、图5以及图6分别是图3的a-a剖视图、b-b剖视图以及c-c剖视图。在图3中未图示出盖。将基底基板12的上表面的法线方向设为z方向,将从输入引线51向输出引线50的方向设为x方向,将与x方向和z方向正交的方向设为y方向。

[0088]

如图3至图6所示,在实施例1的半导体装置100中,封装10具有基底基板12、框体14以及盖16。基底基板12是例如铜和钼的层叠基板等导电体基板。接地电位等基准电位被供给至基底基板12。框体14和盖16是例如由fr-4(flame retardant type 4:阻燃型4)等树脂或陶瓷构成的电介质层。在基底基板12上搭载有半导体芯片25、电容性部件29、34以及38。半导体芯片25设有两个。与半导体芯片25对应地,输入引线51、输出引线50、电容性部件29、34以及38各设有两个。两个半导体芯片25例如相当于多赫蒂放大电路的载波放大器和峰值放大器。也可以是,半导体芯片25为一个,输入引线51、输出引线50、电容性部件29、34以及38各为一个。两个半导体芯片25、两个电容性部件34以及两个电容性部件38分别在y方向上排列。以包围半导体芯片25、电容性部件29、34以及38的方式在基底基板12上设有框体14。框体14通过金属膏(paste)或钎料等的接合层13a接合于基底基板12的上表面。盖16利用树脂等绝缘性粘接剂15接合于框体14的上表面。框体14和盖16将半导体芯片25密封在空隙内。

[0089]

框体14的平面形状为大致矩形。矩形的四边具有对置的边14a和14b、与边14a和14b交叉的边14c和14d。在框体14上设有布线图案54、输出图案52以及输入图案53。输出引线50由与输出图案52相同的金属层形成,输入引线51由与输入图案53相同的金属层形成。输出引线50和输入引线51也可以通过例如金属膏或钎料分别电接合于输出图案52和输入图案53上。输出图案52和输入图案53分别设于对置的边14a和14b,布线图案54设于边14c和14d。输出引线50从输出图案52向+x方向延伸,输入引线51从输入图案53向-x方向延伸。布线图案54、输出图案52以及输入图案53例如是金层或铜层等金属层。输入引线51和输出引

线50例如是金层或铜层等金属层。

[0090]

半导体芯片25具备:半导体基板21;电极22和23,设于半导体基板21的上表面;以及电极24,形成于半导体基板21的下表面。电极22、23以及24分别是栅电极、漏电极以及源电极,电极22和23分别是输入焊盘和输出焊盘。电极22、23以及24例如是金层等金属层。电容性部件29、34以及38分别具备:电介质基板26、31以及35;电极27、32以及36,设于电介质基板26、31以及35的上表面;以及电极28、33以及37,设于电介质基板26、31以及35的下表面。通过隔着电介质基板26、31以及35的各电极27、32以及36与电极28、33以及37形成电容器。电介质基板26、31以及35例如是氧化铝,电极27、28、32、33、36以及37是金层等金属层。电极24、28、33以及37通过金属膏或钎料等的接合层13b电接合于基底基板12。

[0091]

接合线41将输入图案53与电极36电连接。接合线42将电极36与22电连接。接合线43将电极23与32电连接。接合线44将电极32与输出图案52电连接。接合线41~44在俯视观察下大致在x方向上延伸。接合线45将电极23与布线图案54的+x方向的端部电连接。接合线46将电极27与布线图案54的-x方向的端部电连接。接合线41~46例如是金线或铝线。

[0092]

接合线41~44分别相当于图2的电感器l21、l22、l11以及l12。电容性部件34和38分别相当于图2的电容器c21和c11。电容性部件29相当于图2的电容器c1。接合线45、布线图案54以及接合线46相当于图2的电感器l1。

[0093]

[比较例1]

[0094]

图7是比较例1的半导体装置的俯视图。如图7所示,在比较例1的半导体装置110中,未设有布线图案54,半导体芯片25的电极23与电容性部件29的电极27通过接合线45连接。其他构成与实施例1相同。

[0095]

vbw电路60的电感器l1的阻抗在基波中大致为开路。因此,电感器l1的电感例如为2nh左右。若使用接合线45来形成电感器l1,则会使接合线45变长。接合线45的容许电流与接合线45的长度成反比例。若接合线45长,则可能会因流过的电流而熔断。作为熔断对策,可以想到并联设置多根接合线45。在欲得到相同的电感(例如2nh)时,与一根接合线45相比,并联两根接合线45更需要使接合线45变长。因此,即使并联两根接合线45,容许电流也小于2倍,对于熔断的改善效果小。

[0096]

此外,若接合线45在y方向上延伸,则封装10在y方向上大型化。因此,接合线45相对于x方向倾斜地延伸。为了减小封装10的y方向的宽度,接合线45的延伸方向与x方向所成的角度θ例如为30

°

以下。接合线42的电流的朝向如箭头92所示为+x方向。接合线45的电流的朝向如箭头94所示为-x方向。因此,由接合线42与45的互感(mutual inductance)引起的耦合变大。由此,有时会发生放大器的振荡。

[0097]

也可以想到将电容性部件29设于封装10之外。但是,若将电容性部件29外置,则半导体芯片25与电容性部件29之间变长,电感器l1的电感会变得过大。在这样的情况下,电容性部件29搭载于封装10内。

[0098]

[比较例2]

[0099]

图8是比较例2的半导体装置的俯视图。如图8所示,在比较例2的半导体装置112中,在基底基板12上设有布线部件77。布线部件77具备电介质基板78和设于电介质基板78的上表面的布线图案79。接合线45将电极23与布线图案79电连接。接合线46将电极27与布线图案79电连接。由接合线45、布线图案79以及接合线46形成电感器l1。接合线45和46的每

一个可以短于比较例1的接合线45。由此,能抑制接合线45的熔断。

[0100]

此外,可以将接合线45的延伸方向与接合线42的延伸方向所成的角度θ设为30

°

以上。由此,能减小接合线42与45的互感,能减小耦合。由此,能抑制放大器的振荡。

[0101]

然而,由于为了将布线部件77设于框体14内而将布线部件77搭载于基底基板12上,因此在框体14与布线部件77之间和其他部件与布线部件77之间需要空间,封装会大型化。而且,会产生由布线部件77的部件费引起的成本提高、由用于将布线部件77搭载于基底基板12上的作业费引起的成本提高。

[0102]

根据实施例1,如图3~图6所示,在框体14上设有输出引线50和输出图案52(输出端子)。在框体14的上表面设有布线图案54。电容性部件29的电极28(一端)电连接于基底基板12。接合线43和44(第一接合线)将半导体芯片25的电极23(输出焊盘)与输出图案52电连接。接合线46(第二接合线)将电容性部件29(第一电容性部件)的电极27(另一端)与布线图案54的第一区域电连接。接合线45(第三接合线)将半导体芯片25的电极23与布线图案54的不同于第一区域的第二区域电连接。

[0103]

如此,接合线45、布线图案54以及接合线46作为电感器l1发挥功能。由此,即使在形成具有大的电感的电感器l1的情况下,也可以不使用比较例1那样的长的接合线45。由此,能抑制接合线45的熔断。此外,通过将布线图案54设于框体14上,也可以不设置比较例2那样的布线部件77。在实施例1中,布线图案54例如使用与输出图案52相同的成膜工序而形成于框体14上。由此,在实施例1中,能降低比较例2那样的布线部件77的部件成本和将布线部件77搭载于基底基板12上的工序的成本。

[0104]

在比较例2中,在布线部件77与其他部件和框体14之间需要用于搭载工序的空间。在实施例1中,由于布线图案54设于框体14,因此不需要布线图案54与框体14之间的空间,能小型化。

[0105]

与半导体芯片25的电极22(输入焊盘)电连接的输入引线51和输入图案53(输入端子)隔着半导体芯片25设于与输出引线50和输出图案52对置的框体14上。由此,从输入引线51和输入图案53输入的高频信号输入至半导体芯片25的电极22。

[0106]

布线图案54的至少一部分相对于半导体芯片25位于与输入引线51、半导体芯片25以及输出引线50排列的x方向正交的y方向。由此,能增大接合线45与接合线42和43所成的角。由此,能抑制比较例1那样的接合线45与接合线42和43的耦合。由此,能抑制放大器的振荡。接合线45延伸的方向与x方向所成的角度θ优选为30

°

以上,更优选为45

°

以上,进一步优选为75

°

以上。由此,能抑制接合线45与接合线42和43的耦合,能抑制放大器的振荡。

[0107]

半导体芯片25具备将从电极22输入的高频信号放大并输出至电极23的晶体管20。基波(半导体芯片25的晶体管20主要进行放大的高频信号)的频率f下的、形成电感器l1的接合线45、46与布线图案54的合计的阻抗zl的绝对值(2

·

π

·f·

l1)大于与电容性部件29的带宽相当的频率δf下的电容器c1的阻抗zc的绝对值(1/(2

·

π

·

δf

·

c1))。由此,电感器l1抑制基波的频率f的高频信号的通过,电容器c1使与带宽相当的频率δf的高频信号通过。由此,电感器l1和电容器c1作为vbw电路60发挥功能。阻抗zl的绝对值优选比阻抗zc的绝对值大10db以上,更优选大20db以上。

[0108]

电容性部件34(第二电容性部件)的电极33(一端)电连接于基底基板12。接合线43(第四接合线)将半导体芯片25的电极23与电容性部件34的电极32(另一端)电连接,接合线

44(第五接合线)将电容性部件34的电极32与输出图案52电连接。能由电容性部件34、接合线43和44形成内部输出匹配电路61。

[0109]

[实施例1的变形例1]

[0110]

图9是实施例1的变形例1的半导体装置的电路图。如图9所示,在实施例1的变形例1的半导体装置101中,vbw电路60连接于内部输出匹配电路61与输出引线50之间的节点n2。其他电路构成与实施例1的图2相同而省略说明。

[0111]

图10是实施例1的变形例1的半导体装置的俯视图。如图10所示,在实施例1的变形例1的半导体装置101中,布线图案54在框体14上与输出图案52连接。未设有接合线45。其他构成与实施例1的图3相同而省略说明。

[0112]

也可以是,如实施例1的变形例1那样,不设置接合线45,布线图案54在框体14上与输出图案52电连接。由此,输出图案52作为图9的节点n2发挥功能。布线图案54和接合线46作为电感器l1发挥功能。通过将布线图案54形成于框体14的上表面,能与实施例1同样地进行小型化和低成本化。而且,由于可以不设置接合线45,因此不会发生接合线45与其他接合线的耦合。由此,能抑制放大器的振荡和不稳定性。

[0113]

布线图案54的至少一部分相对于半导体芯片25位于y方向的位置。由此,能延长布线图案54,能形成具有所期望的电感的电感器l1。

[0114]

接合线46和布线图案54的合计的基波的频率f下的阻抗zl的绝对值大于与电容性部件29的带宽相当的频率δf下的阻抗lc的绝对值。通过使阻抗zl的绝对值大于阻抗lc的绝对值,电感器l1和电容器c1作为vbw电路60发挥功能。阻抗zl的绝对值优选比阻抗zc的大小大10db以上,更优选大20db以上。

[0115]

[实施例1的变形例2]

[0116]

图11是实施例1的变形例2的半导体装置的俯视图。如图11所示,在实施例1的变形例2的半导体装置102中,在框体14设有引线56。引线56与布线图案54电连接。引线56连接外置的电容性部件90。除了接合线45、布线图案54以及接合线46以外,引线56也作为电感器l1发挥功能。电容性部件29和90作为电容器c2发挥功能。引线56也可以由与布线图案54相同的金属层形成。引线56也可以通过例如金属膏或钎料电接合于布线图案54上。其他构成与实施例1相同而省略说明。通过设置外置电容性部件90,能增大vbw电路60的电容器c1的电容。由此,能降低低频率下的电容器c1的阻抗,vbw电路60的设计变得容易。

[0117]

[实施例1的变形例3]

[0118]

图12是实施例1的变形例3的半导体装置的俯视图。如图12所示,在实施例1的变形例3的半导体装置103中,在实施例1的变形例1的布线图案54导电性地设有引线56。除了布线图案54和接合线46以外,引线56也作为电感器l1发挥功能。电容性部件29和90作为电容器c2发挥功能。其他构成与实施例1的变形例1和2相同而省略说明。由于可以不设置接合线45,因此能与实施例1的变形例1同样地抑制放大器的振荡和不稳定性。此外,通过设置外置电容性部件90,能与实施例1的变形例2同样地增大vbw电路60的电容器c1的电容。由此,能降低低频率下的电容器c1的阻抗,vbw电路60的设计变得容易。

[0119]

如实施例1的变形例2和3那样,引线56(外部端子)是与布线图案54电连接且用于与外置电容性部件连接的端子。由此,能增大vbw电路60的电容器c1的电容。由此,能降低低频率下的电容器c1的阻抗,vbw电路60的设计变得容易。

[0120]

[实施例1的变形例4]

[0121]

图13是实施例1的变形例4的半导体装置的俯视图。如图13所示,在实施例1的变形例4的半导体装置104中,未设有电容性部件34,接合线47将半导体芯片25的电极23与输出图案52电连接。即,接合线47以不连接于搭载于基底基板12上的其他电容性部件的方式将电极23与输出图案52连接。其他构成与实施例1相同而省略说明。如实施例1的变形例4那样可以不设置内部输出匹配电路61。在实施例1的变形例1至3中,也可以不设置内部输出匹配电路61。通过不在基底基板12上设置内部输出匹配电路61,能使半导体装置小型化。

[0122]

[实施例1的变形例5]

[0123]

图14是表示实施例1的变形例5中的vbw电路的电路图。如图14所示,也可以在电感器l1与电容器c1之间连接有电阻r1和电感器l2。在将具有大的电容的电容器c1经由电感器l1连接于半导体芯片25的情况下,由半导体芯片25在内部所具有的寄生电容、电容器c1以及电感器l1产生谐振。因此,通过如图14那样插入电阻r1来作为阻尼电阻(damping resistor),能抑制谐振。电感器l2相当于将电阻r1与电容器c1连接的接合线。其他构成与实施例1及其变形例1至4相同而省略说明。

[0124]

[实施例1的变形例6]

[0125]

图15是表示实施例1的变形例6中的vbw电路的电路图。如图15所示,在电感器l1与电容器c1之间串联连接有电感器l2、电阻r1以及电感器l3,在电感器l1与l2之间的节点n3与地之间,与电感器l2、电阻r1、电感器l3以及电容器c1并联连接有电容器c2。电阻r1是阻尼电阻,电感器l2和l3是用于连接电阻r1的接合线。电容器c2的电容选择小于电容器c1的电容。通过追加电容器c2,能抑制与电容器c1不同的低频段的阻抗。由此,vbw电路60被宽带化。其他构成与实施例1及其变形例1至4相同而省略说明。

[0126]

图16是实施例1的变形例6的半导体装置的俯视图。如图16所示,在实施例1的变形例6的半导体装置105中,在基底基板12上搭载有电阻部件70和电容性部件74。电阻部件70具备电介质基板71和设于电介质基板71的上表面的电极72和73。在电极72与73之间连接有电阻体。电容性部件74具备电介质基板75和设于电介质基板75的上表面的电极76。设于电介质基板75的下表面的电极与基底基板12电连接。接合线48将电容性部件29的电极27与电阻部件70的电极72电连接。接合线49将电阻部件70的电极73与电容性部件74的电极76电连接。接合线48和49分别相当于电感器l2和l3。电阻部件70和电容性部件74分别相当于电阻r1和电容器c1。除了电容性部件29以外,还使用电阻部件70和电容性部件74,由此能实现图15的实施例1的变形例6。其他构成与实施例1相同而省略说明。

[0127]

如实施例1的变形例5和6那样,vbw电路60也可以具备除了电感器l和电容器c1以外的电感器、电容器和/或电阻。如实施例1的变形例6那样,可以分别将接合线、电容性部件以及电阻部件用作电感器、电容器以及电阻。

[0128]

[实施例1的变形例7]

[0129]

图17是表示实施例1的变形例7中的vbw电路的电路图。如图17所示,也可以在电感器l1与电容器c1之间连接有电阻r1。电阻r1和电容器c1也可以设于ipd(integrated passive device:集成无源器件)80。电阻r1作为抑制谐振的阻尼电阻发挥功能。通过将电容器c1和电阻r1形成于ipd80,能实现部件的小型化。其他构成与实施例1及其变形例1至4相同而省略说明。

[0130]

[实施例1的变形例8]

[0131]

图18是表示实施例1的变形例8中的vbw电路的电路图。如图18所示,在电感器l1与电容器c1之间串联连接有电阻r1,在电感器l1与电阻r1之间的节点n3与地之间与电阻r1和电容器c1并联连接有电容器c2。电阻r1作为抑制谐振的阻尼电阻发挥功能。通过追加电容器c2并使用电容不同的电容器c1和c2,能使vbw电路60宽带化。其他构成与实施例1及其变形例1至4相同而省略说明。

[0132]

图19是实施例1的变形例8的半导体装置的俯视图。如图19所示,在实施例1的变形例8的半导体装置106中,在基底基板12上搭载有ipd80。ipd80具备电介质基板81、设于电介质基板81的上表面的电极82、84以及电阻体83。在电介质基板81的下表面设有与基底基板12电连接的电极。隔着电介质基板81的电极82和84与下表面的电极分别形成电容器c1和c2。ipd80是具有电容器c1的电容性部件。连接于电极82与84之间的电阻体83形成电阻r1。通过将电容器c1、c2以及电阻r1形成于ipd80,能实现部件的小型化。其他构成与实施例1相同而省略说明。

[0133]

如实施例1的变形例7和8那样,vbw电路60的一部分也可以由ipd80形成。如实施例1的变形例8那样,电感器、电容器以及电阻中的至少一个可以由ipd80形成。

[0134]

在实施例1及其变形例中,对电感器l1和电容器c1形成vbw电路60的例子进行了说明,但电感器l1和电容器c1也可以是vbw电路60以外的电路,例如也可以是内部输出匹配电路61的至少一部分。

[0135]

应该认为本次所公开的实施方式在所有方面均是示例而不是限制性的。本公开的范围并不是上述的含义,而是由权利要求书示出,意图在于包括与权利要求书等同的含义和范围内的所有变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1