半导体元件的制造方法与流程

1.本揭露是关于一种半导体元件的制造方法。

背景技术:

2.物理气相沉积(physical vapor deposition,pvd)或溅射为一种用于制造电子元件的制程。pvd为在真空腔室中执行的电浆制程,在真空腔室中负偏置的目标暴露于具有相对重原子的惰性气体(例如氩气(ar))或包括此惰性气体的气体混合物的电浆。惰性气体的离子对目标的轰击引起目标材料的原子的喷射。喷射的原子作为沉积膜累积在置放在基板支撑基座上的基板上,基板支撑基座安置在腔室内。

技术实现要素:

3.于一些实施方式中,半导体元件的制造方法是用以优化沉积在一半导体处理腔室中的一半导体基板上的一目标材料膜的厚度。半导体处理腔室包含位于半导体处理腔室上的一磁性组件,磁性组件包含在磁性组件内的多个磁柱。方法包括以下步骤:操作半导体处理腔室以在位于半导体处理腔室内的一半导体基板上沉积一目标材料膜;量测沉积膜的一均匀性;调整一个或多个磁柱在磁性组件中的一位置;及在调整一个或多个磁柱的位置之后,操作半导体处理腔室以沉积目标材料的膜。

4.于一些实施方式中,半导体元件的制造方法是使用一半导体处理腔室。半导体处理腔室包含一磁性组件,磁性组件包含位于半导体处理腔室上的多个磁柱。方法包括以下步骤:监测在半导体处理腔室中一目标材料的一侵蚀及沉积在位于半导体处理腔室中的一半导体基板上的目标材料的一膜的一厚度;当目标材料的侵蚀均匀性及/或沉积膜的厚度均匀性超过一对应临限值时,自磁性组件中移除三个磁柱,以使得目标材料以一基本均匀的方式被侵蚀,且具有一基本均匀的厚度的一膜沉积在半导体基板上;及在移除三个磁柱之后,使用磁性组件在半导体基板上执行一半导体制造制程。

5.于一些实施方式中,半导体元件的制造方法包括以下步骤:量测由位于一真空腔室上方的一磁性组件中的多个磁体形成的一磁场,一目标置放于真空腔室中,且磁性组件包含多个磁体;沿着远离目标的一方向调整一个或多个磁体的多个位置;及使用目标在一半导体基板上执行一溅射操作。

附图说明

6.当结合随附附图阅读时,根据以下详细描述最佳地理解本揭露。需要强调的是,根据行业中的标准实践,各种特征未按比例绘制且仅出于说明目的而使用。实务上,为了论述清楚起见,各种特征的尺寸可以任意增加或减小。

7.图1说明半导体处理腔室;

8.图2a为说明在重复沉积制程之后钛目标表面的侵蚀轮廓的曲线图;

9.图2b为说明在重复沉积制程之后氮化钛目标表面的侵蚀轮廓的曲线图;

10.图3为说明沉积膜的不均匀性的曲线图;

11.图4a说明图1中的包含多个磁体的组件的局部等角视图;图4b为图4a中的组件的平面图;

12.图5说明图4a及图4b中的磁性组件的磁通量密度分布图;

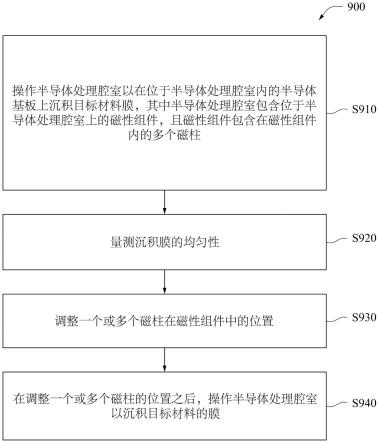

13.图6说明根据本揭露的实施例的图4a及图4b中的磁性组件的在移除磁柱19、23及38之后所获得的磁通量密度分布图;

14.图7为描绘半导体基板上的沉积膜的电阻率随目标与基板的间距的变化而变化的曲线图;

15.图8a及图8b示出了根据本揭露的实施例的控制器;

16.图9为根据本揭露的实施例的优化沉积在半导体处理腔室中的半导体基板中的目标材料膜的厚度的方法的流程图;

17.图10为根据本揭露的实施例的使用半导体处理腔室的方法的流程图;

18.图11为根据本揭露的实施例的操作半导体处理腔室的方法的流程图。

19.【符号说明】

20.19、23、38:磁柱

21.42:中心区域

22.44:外边缘区域

23.100:物理气相沉积腔室

24.101:基板

25.102:腔室壁

26.103:基板支撑件

27.104:提升机构

28.105:处理区

29.106:绝缘体

30.107:配接器

31.110:溅射目标

32.120:沉积屏蔽件

33.121:上部屏蔽件

34.122:下部屏蔽件

35.123:盖环

36.151:真空泵

37.152:阀

38.153:气源

39.154:dc电源

40.190:系统控制器

41.400:磁体组件

42.402:磁体

43.403:支撑结构

44.411、413:组

45.500、600:磁通量密度分布图

46.502:标尺

47.702、704:曲线

48.800:计算机系统

49.801:计算机

50.802:键盘

51.803:鼠标

52.804:显示器

53.805:光盘只读记忆体驱动器

54.806:磁盘驱动器

55.811:处理器

56.812:rom

57.813:随机存取记忆体

58.814:硬盘

59.815:总线

60.821:光盘

61.822:磁盘

62.900、1000、1100:方法

63.a、b:点

64.s910、s920、s930、s940、s1010、s1020、s1030、s1110、s1120、s1130:操作

具体实施方式

65.应理解,以下揭露内容提供了用于实施本揭露的不同特征的许多不同的实施例或实例。下文描述元件及配置的特定实施例或实例以简化本揭露。当然,这些特定实施例或实例仅为实例,而不旨在进行限制。例如,部件的尺寸不限于所揭露的范围或值,而是可以取决于制程条件及/或元件的期望性质。此外,在以下描述中第一特征在第二特征上方或上的形成可以包含第一特征及第二特征直接接触地形成的实施例,且亦可以包含额外特征可以形成为插入第一特征与第二特征之间以使得第一特征及第二特征可以不直接接触的实施例。为了简单及清楚起见,可以以不同的比例任意绘制各种特征。

66.另外,为了便于描述,本文中可以使用空间相对术语(诸如“在...之下”、“在...下方”、“底部”、“在...上方”、“上部”及其类似者),以描述如附图中所说明的一个部件或特征与另一部件或特征的关系。除了在附图中所描绘的定向之外,空间相对术语亦旨在涵盖元件在使用或操作中的不同定向。元件可以以其他方式定向(旋转90度或处于其他定向),且因此可以相应地解释本文中所使用的空间相对描述词。此外,术语“由

……

制成”可以意谓“包括”或“由

……

组成”。

67.本揭露的实施例通常是关于诸如物理气相沉积(physical vapor deposition,pvd)制程设备的电浆制程设备及优化由物理气相沉积(physical vapor deposition,pvd)制程设备产生的磁场的方法。更特定而言,本揭露的实施例是针对优化由物理气相沉积(physical vapor deposition,pvd)制程设备中的磁性组件产生的磁场以在半导体基板上

沉积目标材料的较均匀的膜。

68.在半导体集成电路的制造中,金属导线用于互连半导体基板上的元件电路中的多个元件。用于在半导体基板上沉积金属导线图案的通用制程包含:在半导体基板上方沉积导电层;使用微影技术形成呈所需的金属导线图案的形式的光阻剂遮罩或由诸如氧化钛或氧化硅的氧化物制成的其他硬遮罩;对半导体基板进行干式蚀刻制程以自未经遮罩覆盖的区域移除导电层,从而以经遮罩的导线图案的形式留下金属层;及使用反应性电浆移除遮罩层,从而暴露金属导线的顶表面。导电及绝缘材料的多个交替层依次沉积在半导体基板上,且半导体基板上方的不同位准处的导电层可以通过在绝缘层中蚀刻通孔或开口而彼此电连接且使用铝、钨或其他金属填充通孔以建立导电层之间的电连接。

69.可以使用物理气相沉积(physical vapor deposition,pvd)来实现导电层在半导体基板上的沉积。物理气相沉积(physical vapor deposition,pvd)包含蒸发、电子束蒸发、电浆喷涂沉积及溅射。在溅射中,通过在半导体基板的表面上沉积或“溅射”源材料的金属层,源材料在真空中实体地转移至半导体基板上。源材料存在于在沉积操作中充当阴极的目标中。

70.在溅射阴极中,以目标的形式提供的源材料被来自电浆放电的高能离子侵蚀,且由离子释放的材料经由物理气相沉积(physical vapor deposition,pvd)在基板上沉积为薄膜。电浆放电通常在工作气体(例如惰性气体,如氩气)的受控流动下以在目标阴极与阳极之间由电源施加的电位及放电电流维持在例如真空室的抽真空制程腔室中。

71.在导电目标材料的情况下,为目标供应连续或脉动负电压,以使得在目标表面上方形成电浆。借助于在电浆与目标表面之间形成的电场,来自电浆的带正电的离子朝向负偏置的目标表面(即阴极)移动,从而轰击目标表面且通过自目标释放材料而引起目标的侵蚀且导致材料自目标表面溅射离开。自侵蚀目标释放的材料被引导至半导体基板或位于沉积腔室中的其他工件。

72.在溅射系统中,目标上方的电浆密度使用磁场来强烈增加。由磁场产生的高电浆密度区中的离子变得高度赋能。磁场由配置成紧邻目标的磁体产生。磁体安置在与目标溅射表面相对的目标的一侧上,即在一些实施例中在目标后面。

73.物理气相沉积(physical vapor deposition,pvd)制程腔室内的沉积经由许多变数来控制,这些变数包含腔室真空程度、制程气体的组成、电浆密度及均匀性、施加至晶圆的偏置等。除了上文变数之外,使用物理气相沉积技术沉积的膜的均匀性及质量亦取决于物理气相沉积(physical vapor deposition,pvd)制程腔室的几何形状(诸如磁剖面)及腔内的制程套件元件的形状、目标与晶圆的间距及其类似者。

74.图1为根据本揭露的各种实施例的物理气相沉积(physical vapor deposition,pvd)腔室100的示意性横截面图示。pvd腔室100用以将材料沉积至基板101上,作为制造电子电路(诸如集成电路晶片及显示器)的制程的一部分。更具体而言,pvd腔室100由pvd或“溅射”制程将来自溅射目标110的材料沉积至基板101上,其中高能离子撞击溅射目标110,从而使得目标材料颗粒自溅射目标110喷射且在基板101上沉积为膜。可以由pvd腔室100沉积的材料的实例包含但不限于:各种金属,诸如铝(al)、铜(cu)、钨(w)、钼(mo)、钽(ta)、钛(ti)、钴(co)、铂(pt)、钌(rt)及其合金;及/或金属化合物,诸如氮化钽(tan)、氮化钨(w2n、wn或wn2)、氮化钛(tin)、氮化铝(aln)、氮化铝钪(scaln或sc

x

al

x

n)及其类似者。

75.pvd腔室100包含腔室壁102。如所示出,pvd腔室100进一步包含安置在腔室壁102内的耦接至提升机构104的基板支撑件103及一个或多个沉积屏蔽件120。pvd腔室100进一步包含安装在腔室壁102上或耦接至腔室壁102的溅射目标110。在图1中所说明的实施例中,溅射目标110由绝缘体106与腔室壁102电隔离,绝缘体106安置在安装在腔室壁102上的配接器107上。溅射目标110、沉积屏蔽件120及基板支撑件103(当提升至接近目标110的处理位置时)一起限定处理区105,在pvd腔室100中执行的沉积制程期间在处理区105中形成电浆。

76.pvd腔室100进一步包含:一个或多个真空泵151,经由相应的阀152流体耦合至pvd腔室100;气源153,流体耦合至pvd腔室100;及dc电源154,电耦合至溅射目标110。在操作中,溅射目标110用作阴极且例如通过电耦合至dc电源154而带负电。真空泵151用以在pvd腔室100中在半导体基板101上执行的沉积制程期间产生目标真空程度。气源153用以在此沉积制程期间提供一种或多种制程气体。此外,磁体组件400安置在pvd腔室100的外部及溅射目标110附近,且围封在水冷腔室中。磁体组件400在带负电的溅射目标110上方捕获电子,从而增加目标溅射速率,且因此在基板101上创建较高的沉积速率。

77.dc电源154在沉积制程期间电耦合至溅射目标110,以使得溅射目标110具有针对在处理区105中产生的电浆的适合的电荷。在一些实施例中,基板支撑件103亦耦合至dc或射频(radio frequency,rf)电源以提高沉积在基板101上的材料的均匀性或其他膜特性。

78.在一些实施例中,dc电源154用以作为可程序电源,可程序电源回应于诸如来自针对pvd腔室100的控制器的命令的命令而产生可变dc输出。可变dc输出可以由dc电源154经由不同功率幅度的脉冲dc输出来实施。另外,可变dc输出可以遵循随时间而变的输出曲线。例如,可变dc输出可以遵循包含在pvd制程的开始时段期间的特定功率斜升曲线及在pvd制程的结束时段期间的功率斜降曲线的曲线。替代地或附加地,可变dc输出根据任何适合的函数随时间变化,函数包含阶跃函数、正弦函数或任何其他适合的时变函数。在其他实施例中,dc电源154用以作为可控电源,可控电源用以回应于特定输入值来产生特定dc输出。在这些实施例中,与pvd腔室100相关联的控制器传输实时改变的输入,且从而在pvd腔室100中的pvd制程期间直接控制dc电源154的dc功率输出。

79.溅射目标110为固体金属或其他待沉积材料,且耦接至背板且由背板支撑。在操作中,溅射目标110用作阴极,且在一些实施例中,例如通过电耦合至dc电源154而带负电。

80.沉积屏蔽件120保护腔室壁102及pvd腔室100内的其他元件免于接收溅射材料的沉积。在图1中所说明的实施例中,沉积屏蔽件120包含安装在配接器107上的上部屏蔽件121、下部屏蔽件122及盖环123,但pvd腔室100可以包含沉积屏蔽件的任何其他技术上可实行的组态或不超出本揭露的范畴的单个沉积屏蔽件。

81.pvd腔室100由系统控制器190控制,系统控制器190促进处理腔室100的控制及自动化且通常包含中央处理单元(central processing unit,cpu)、记忆体及支援电路(或i/o)。cpu可为在工业设置中用于控制各种系统功能、基板移动、腔室制程及支撑硬件(例如感测器、机器人、电动机等)且监测制程(例如基板支撑温度、电源变数、腔室制程时间、i/o信号等)的任何形式的计算机处理器中的一者。记忆体连接至cpu,且可为容易获得的记忆体中的一者或多者,诸如随机存取记忆体(random access memory,ram)、只读记忆体(read only memory,rom)、软盘、硬盘或本地或远端的任何其他形式的数字储存器。软件指令及数

据可以被编码且储存在记忆体内以用于指导cpu。支援电路亦连接至cpu,以用于以常规方式支撑处理器。支援电路包含快取、电源、时钟电路、输入/输出电路系统、子系统及其类似者。系统控制器190可读的程序(或计算机指令)确定将在基板上执行哪些任务。程序为系统控制器190可读的软件,软件包含执行与移动的监测、执行及控制相关的任务的程序码及在pvd腔室100中执行的各种制程配方任务及配方步骤。例如,系统控制器190包括程序码,程序码包含用以操作基板支撑件的基板定位指令集、用以操作流量控制阀以设置至处理腔室100的溅射气体流量的气流控制指令集、用以操作节流阀或闸阀以维持处理腔室100中的压力的气体压力控制指令集、用以控制基板支撑件中的温度控制系统的温度控制指令集及用以监测处理腔室100中的制程的制程监测指令集。

82.使用磁体400产生具有均匀通量分布的磁场为具有挑战性的。因此,目标110的面向处理区105的表面上的某些区域比其他区域受到更多的轰击。此情况是由处理区105中的电浆中的非均匀电浆离子分布引起的,其又由非均匀磁通量分布引起。

83.不均匀目标侵蚀的实例在图2a中的侵蚀曲线中示出,其中金属目标110的表面中的某些区域遭受较多的电浆离子轰击,从而导致对钛目标的较多侵蚀。当在金属目标上形成此非均匀侵蚀曲线时,目标必须比正常需要更频繁地更换,以便避免目标上的某些区域由非均匀轰击磨损。如图2a中所见,当与钛目标的中心区域42相比时,钛目标在外边缘区域44处几乎磨损了2/3(当自目标的顶部观察时以圆环形式示出)说明tin目标的非均匀磨损的类似曲线图在图2b中示出。

84.图2a及图2b中所示出的金属目标表面的不均匀的磨损或消耗不仅会导致过早失效及对更换金属目标的需要,而且会影响沉积膜的均匀性。此情况在图3中示出了tin膜的溅射沉积的膜厚度的不均匀性或偏差随时间变化的曲线图。在点a及b处,安装了新的目标以更换过早磨损的目标。如图3中所见,每次安装新目标之后,沉积膜的不均匀性以大致相同的速率逐渐增加。图3的数据可以与图2b的数据协调,此是由于ti目标被侵蚀得愈严重(即,形成的峰值及谷值愈严重),磁通量密度分布愈不均匀,从而导致沉积的tin膜中的不均匀性愈大。在图3中可见,在新目标开始时,沉积的tin膜的不均匀性极小。不均匀性随着金属目标的表面被更严重地侵蚀而逐渐增加,从而形成归因于不均匀的磁通量分布而被电浆离子更严重地轰击的圆环区部。如先前所论述,不均匀磁通量分布由阴极引起,阴极具有在顶部安装在固定位置中的磁体。

85.本揭露的实施例是针对一种用于溅射沉积的磁性组件,磁性组件变化能够产生基本均匀的磁通量分布的磁体配置。基本均匀的磁通量分布引起在半导体基板上溅射沉积较均匀厚度的金属膜。均匀金属膜在整个膜的区域中表现出较均匀的电阻率。

86.尽管参考磁性组件400论述了本揭露的实施例,但实施例不限于此。在不脱离本揭露的范畴的情况下,本揭露的实施例同样适用于处理腔室中所使用的其他类型的磁场产生器,其中期望获得较均匀的磁场。

87.图4a说明图1中的包含多个磁体402的组件400的局部等角视图。图4b说明图4a中的组件400的平面图。参考图4a及图4b,每一磁体402具有柱(或导柱)形状,且多个磁柱402以期望的配置被配置。在一些实施例中,磁柱402包含由稀土、高强度材料制成的永磁体。多个磁柱402参考水平线(图1)配置在基本竖直的位置中。支撑结构403将多个磁柱402固定在其位置中。在一些实施例中,且如所说明,多个磁柱402包含45个磁柱。每一磁体磁柱402配

置在特定位置处且被具体编号。

88.在一些实施例中,且如所说明,多个磁柱402经由不同的支撑结构403配置在两组或更多组磁柱402中。磁性组件包含磁柱402的组411及413。尽管每一组411及413说明为包含多个磁柱402,但在一些实施例中,一个或多个组可以包含单个磁柱402。每一组411及413由磁柱402形成,这些磁柱402由对应的支撑结构403固定就位。如下文所论述,每一组411及413可以具有不同的磁通量密度值。在一些实施例中,多个磁柱402以包含期望数目的列及行的矩阵类型配置被配置。在其他实施例中,且如所说明,多个磁柱402以螺旋配置被配置。在一些实施例中,相邻磁柱402的北(n)极及南(s)极交替配置。

89.图5说明图4a及图4b中的磁性组件400的磁通量密度分布图500。亦在图5中说明的为指示针对磁性组件400的磁通量密度的不同值的不同阴影的标尺502。标尺502描绘了磁通量密度自标尺的底部至顶部递增的值,其中标尺上的最高值最大且最低值最低。

90.参考图4a、图4b及图5,组411具有大致第一磁通量密度值,而组413具有大致第二磁通量密度值。

91.参考标尺502,观察到与其余组411及组413中的磁通量密度值相比,组411中的区域a中的磁通量密度最大。磁通量密度的此相对不均匀的分布导致磁场的较大变化,因此,目标金属的非均匀膜沉积在半导体基板上。期望减小区域a中的磁通量密度以获得较均匀的磁通量密度分布。

92.通过调整多个磁柱402产生的磁场,可以获得磁柱的一组或多组内较均匀的磁通量密度分布。在一些实施例中,磁场可以通过改变一个或多个磁柱的位置来调整,且从而获得较均匀的磁通量密度分布。例如,一个或多个磁柱自处理区105移开(升高)以减少由磁性组件400产生的磁场。在其他实施例中,磁场可以通过自磁性组件中移除一个或多个磁柱来调整,且从而获得较均匀的磁通量密度分布。在一些实施例中,移动磁柱19、23及38以获得较均匀的磁通量密度分布。在一些实施例中,移除编号为19、23及38的磁柱以获得较均匀的磁通量密度分布。在一些实施例中,移除磁柱,以使得两个相邻(紧邻)磁柱402之间的分隔(缝隙)大于磁性组件400中超过至少80%磁体之间的分隔。在其他实施例中,分隔大于磁性组件400中的至少90%磁体。在其他实施例中,移动或移除除编号为19、23及38的磁柱外的磁柱以获得较均匀的磁通量密度分布。应当注意,待移除或升高的磁柱取决于组件400中的多个磁柱402的配置(组态),且磁通量密度分布是使用配置获得。因此,在磁柱的不同配置中,移除不同的磁柱以获得较均匀的磁通量密度分布。

93.在一些实施例中,为了确定磁通量密度分布的均匀性,执行测试操作(或类似操作),其中停止半导体处理操作且量测组件400的磁通量密度分布且确定磁通量密度分布的变化。

94.针对形成金属膜的半导体元件的不同部分,所沉积的金属膜的均匀性为不同的。例如,半导体基板的一些区(例如栅极)具有比半导体基板的其他区相对较厚的膜。在其他实例中,各个元件(例如晶体管)之间的一些金属互连可能比其他金属互连更厚。因此,针对半导体基板的不同区分别确定金属膜的均匀性。如此,取决于在半导体基板上制造的元件,金属膜在整个半导体基板上方将为不均匀的,但在半导体基板的特定区中可能为均匀的。

95.图6说明根据本揭露的实施例的图4a及图4b中的磁性组件400的在移除磁柱19、23及38之后所获得的磁通量密度分布图600。如所说明,归因于移除了磁柱19、23及38,区域a

中的磁通量密度降低,且自磁性组件400的组411中获得了较均匀的磁通量密度分布。

96.由于组411及413中较均匀的磁通量密度分布,较均匀的金属膜沉积在半导体基板上。均匀金属膜在整个膜的区域中表现出较均匀的电阻率。此外,目标材料被较均匀地侵蚀。为了本文中论述的目的,应当注意,均匀的磁通量分布可以指示磁性组件400的整个磁通量分布具有基本相同的值(在可接受的变化内)。替代地,均匀的磁通量分布可以指示磁性组件400的一组磁柱402表现出具有基本上第一值的磁通量分布,且磁性组件400的另一组磁柱402(不同于第一)表现出具有基本上第二值的磁通量分布。在情况下,虽然不同组的磁通量分布不同,但每一组内的磁通量分布基本相同。此情况与图5中所说明的场景不同,其中组411中的磁柱402的磁通量分布包含区域a,区域a具有明显高于组411的其余部分的磁通量分布的值。

97.在一些实施例中,在半导体元件的制造期间沉积在半导体基板上的膜的厚度例如以期望的间隔被监测。在一些实施例中,以期望的间隔执行测试操作(或类似操作),在间隔期间暂停半导体处理操作(例如pvd操作)以量测组件400的磁通量密度分布、磁通量密度分布的变化及沉积膜的厚度。附加地或替代地,亦监测了目标材料的侵蚀。如下文所论述,在一些实施例中,可以基于沉积膜的电阻率来确定膜的厚度。当沉积膜的不同区域中的沉积膜的厚度差值大于临限值时,由磁性组件400产生的磁场根据本文中所揭露的实施例被优化为更均匀的。附加地或替代地,当目标材料的不同位置处的目标材料的厚度差值超过临限值时,指示目标材料的不期望的非均匀侵蚀,由磁性组件400产生的磁场根据本文中所揭露的实施例被优化为更均匀的,以使得目标材料被更均匀地侵蚀且在半导体基板上沉积更均匀的膜。

98.除了移除磁柱402之外,半导体基板101(图1)与溅射目标110(图1)之间的间距亦发生变化,以在半导体基板101上沉积更均匀的金属膜。在一些实施例中,间距减小。在一些实施例中,间距自约60mm减小至约53mm。在一些其他实施例中,间距自约60mm减小至约55mm。在一些实施例中,在减小间距之后,间距小于53mm。

99.图7为描绘半导体基板上的沉积膜的电阻率均匀性随目标与基板的间距的变化而变化的曲线图。电阻率均匀性沿着纵坐标绘制为半导体基板上方的电阻率的百分比(%)标准偏差,且目标与基板的间距沿着横坐标绘制。曲线702指示当磁柱19、23及38保持在磁性组件400(图4a及图4b)中且目标与基板的间距基板上为大约60mm(具有某一可接受的变化)时,沉积膜的电阻率随目标与基板的间距的变化而进行的变化。曲线704指示当磁柱19、23及38自磁性组件400(图4a及图4b)中移除且目标与基板的间距基板上为大约53mm(具有某一可接受的变化)时,沉积膜的电阻率随目标与基板的间距的变化而进行的变化。如所见,当目标与基板的间距基本上为大约53mm且不存在磁柱19、23及38时,沉积膜的电阻率的变化为最低的。电阻率的低值指示具有更均匀厚度的膜已经沉积在半导体基板上。在一些实施例中,膜包含氮化钛(tin)且具有大约1%的电阻率均匀性及小于约10μω-cm的电阻率。在一些实施例中,电阻率使用四点探针来量测。

100.图8a为计算机系统的示意图,计算机系统作为控制器(例如控制器190)操作以用于确定沉积在半导体基板上的目标膜的厚度、确定目标材料的侵蚀、操作半导体处理腔室100及执行本揭露中所提到的其他任务。可以使用计算机硬件及在其上执行的计算机程序来实现前述实施例。在图8a中,计算机系统800设置有计算机801、键盘802、鼠标803及显示

器804,计算机801包含光盘只读记忆体(例如cd-rom或dvd-rom)驱动器805及磁盘驱动器806。

101.图8b为示出计算机系统800的内部组态的图。在图8b中,除了光盘驱动器805及磁盘驱动器806之外,计算机801亦设置有一个或多个处理器811,诸如微处理单元(micro processing unit,mpu)、rom 812(存储程序(诸如启动程序))、随机存取记忆体(random access memory,ram)813(连接至mpu 811且其中临时储存应用程序的命令且提供临时储存区域)、硬盘814(其中储存应用程序、系统程序及数据)及总线815(连接mpu 811、rom 812及其类似者)。注意,计算机801可以包含用于提供与lan的连接的网卡(未示出)。

102.用于使计算机系统800执行前述实施例中所论述的操作/任务的程序码可以储存在光盘821或磁盘822中,光盘821或磁盘822插入至光盘驱动器805或磁盘驱动器806中且传输至硬盘814。替代地,程序可以经由网络(未示出)传输至计算机801且储存在硬盘814中。在执行时,将程序加载至ram 813中。程序可以自光盘821或磁盘822加载,或直接自网络加载。

103.本揭露的实施例为根据图9中所说明的流程图的优化沉积在半导体处理腔室中的半导体基板中的目标材料膜的厚度的方法900。应理解,可以在图9中所论述的制程之前、期间及之后提供额外的操作,且针对方法的额外实施例,可以将下文所描述的一些操作替换或消除。操作/制程的顺序可为可互换的,且至少一些操作/制程可以以不同的序列执行。可以在时间上重叠或几乎同时地执行至少两个或更多个操作/制程。

104.方法包含操作半导体处理腔室以在位于半导体处理腔室内的半导体基板上沉积目标材料膜的操作s910。半导体处理腔室包含位于半导体处理腔室上的磁性组件,且磁性组件包含在磁性组件内的多个磁柱。在操作s920中,量测沉积膜的均匀性。在操作s930中,调整一个或多个磁柱在磁性组件中的位置。在操作s940中,在调整一个或多个磁柱的位置之后,操作半导体处理腔室以沉积目标材料的膜。

105.本揭露的实施例为根据图10中所说明的流程图使用半导体处理腔室的方法1000。应理解,可以在图10中所论述的制程之前、期间及之后提供额外的操作,且针对方法的额外实施例,可以将下文所描述的一些操作替换或消除。操作/制程的顺序可为可互换的,且至少一些操作/制程可以以不同的序列执行。可以在时间上重叠或几乎同时地执行至少两个或更多个操作/制程。

106.方法包含监测在半导体处理腔室中目标材料的侵蚀及沉积在位于半导体处理腔室中的半导体基板上的目标材料的膜的厚度的操作s1010。半导体处理腔室包含磁性组件,磁性组件包含位于半导体处理腔室上的多个磁柱。在操作s1020中,当目标材料的侵蚀均匀性及/或沉积膜的厚度均匀性超过对应临限值时,自磁性组件中移除三个磁柱,以使得目标材料以基本均匀的方式被侵蚀,且具有基本均匀的厚度的膜沉积在半导体基板上。在操作s1030中,在移除三个磁柱之后,使用磁性组件在半导体基板上执行半导体制造制程。

107.本揭露的实施例为根据图11中所说明的流程图操作半导体处理腔室的方法1100。应理解,可以在图11中所论述的制程之前、期间及之后提供额外的操作,且针对方法的额外实施例,可以将下文所描述的一些操作替换或消除。操作/制程的顺序可为可互换的,且至少一些操作/制程可以以不同的序列执行。可以在时间上重叠或几乎同时地执行至少两个或更多个操作/制程。

108.方法包含量测由位于真空腔室上方的磁性组件中的多个磁体形成的磁场的操作s1110,目标置放于真空腔室中,且磁性组件包含多个磁体。在操作s1120中,沿着远离目标的方向调整一个或多个磁体的位置。在操作s1130中,使用目标在半导体基板上执行溅射操作。

109.本揭露的实施例提供了一种使用pvd腔室改进沉积在半导体基板上的目标膜的厚度的有利方法。方法亦确保目标材料被更均匀地侵蚀。

110.应理解,并非所有优点皆在本文中被必要地论述,所有实施例或实例不需要特定优点,且其他实施例或实例可提供不同的优点。

111.本揭露的实施例是针对一种用于优化沉积在半导体处理腔室中的半导体基板上的目标材料膜的厚度的方法。半导体处理腔室包含位于半导体处理腔室上的磁性组件,且磁性组件包含在磁性组件内的多个磁柱。方法包含:操作半导体处理腔室以在位于半导体处理腔室内的半导体基板上沉积目标材料膜;量测沉积膜的均匀性;调整一个或多个磁柱在磁性组件中的位置;及在调整一个或多个磁柱的位置之后,操作半导体处理腔室以沉积目标材料的膜。在一些实施例中,停止半导体处理腔室的操作,且自磁性组件中移除一个或多个磁柱。在一些实施例中,停止半导体处理腔室的操作,且沿着远离配置在半导体处理腔室中的目标材料的方向移动磁性组件的一个或多个磁柱。在一些实施例中,通过量测在半导体基板的不同区处的沉积膜的电阻率以确定在半导体基板的不同区中的每一者中所沉积的膜的厚度来量测沉积膜的均匀性。在一些实施例中,减小目标材料与半导体基板之间的间距,且在减小间距之后及在自磁性组件中移除两个或更多个磁柱之后操作半导体处理腔室以沉积目标材料的膜。在一些实施例中,间距自大约60mm减小至大约53mm。在一些实施例中,目标材料的膜包含具有1%的电阻率变化及小于10μω-cm的电阻率的氮化钛(tin)。在一些实施例中,多个磁柱包含永磁材料。在一些实施例中,目标材料膜包含选自由铝(al)、铜(cu)、钨(w)、钼(mo)、钽(ta)、钛(ti)、氮化钽(tan)、氮化钨(w2n、wn或wn2)、氮化钛(tin)、氮化铝(aln)及氮化铝钪(scaln或sc

x

al

x

n)组成的群组的材料。

112.本揭露的实施例是针对一种使用半导体处理腔室制造半导体元件的方法。半导体处理腔室包含磁性组件,磁性组件包含位于半导体处理腔室上的多个磁柱。方法包含:监测在半导体处理腔室中目标材料的侵蚀及沉积在位于半导体处理腔室中的半导体基板上的目标材料的膜的厚度;当目标材料的侵蚀均匀性及/或沉积膜的厚度均匀性超过对应临限值时,自磁性组件中移除三个磁柱,以使得目标材料以基本均匀的方式被侵蚀,且具有基本均匀的厚度的膜沉积在半导体基板上;及在移除三个磁柱之后,使用磁性组件在半导体基板上执行半导体制造制程。在一些实施例中,减小目标材料与半导体基板之间的间距,且在减小间距之后执行半导体制造制程以沉积目标材料的膜。在一些实施例中,间距自大约60mm减小至大约53mm。在一些实施例中,目标材料的膜包含具有1%的电阻率变化及小于10μω-cm的电阻率的氮化钛(tin)。在一些实施例中,半导体制造操作包含沉积操作或蚀刻操作。在一些实施例中,多个磁体包含永磁体。在一些实施例中,移除三个磁柱,以使得归因于多个磁体所致的磁通量密度基本均匀。在一些实施例中,其中将多个磁柱配置成两组或更多组,且移除来自一组或多组中的磁柱。

113.根据本揭露的一些实施例,一种方法包含:量测由位于真空腔室上方的磁性组件中的多个磁体形成的磁场,目标置放于真空腔室中,且磁性组件包含多个磁体;沿着远离目

标的方向调整一个或多个磁体的位置;及使用目标在半导体基板上执行溅射操作。在一些实施例中,基于沉积在半导体基板上的目标的膜的厚度来调整一个或多个磁体的位置。在一些实施例中,调整一个或多个磁体的位置以使得产生基本均匀的磁场。

114.于一些实施方式中,半导体元件的制造方法是用以优化沉积在一半导体处理腔室中的一半导体基板上的一目标材料膜的厚度。半导体处理腔室包含位于半导体处理腔室上的一磁性组件,磁性组件包含在磁性组件内的多个磁柱。方法包括以下步骤:操作半导体处理腔室以在位于半导体处理腔室内的一半导体基板上沉积一目标材料膜;量测沉积膜的一均匀性;调整一个或多个磁柱在磁性组件中的一位置;及在调整一个或多个磁柱的位置之后,操作半导体处理腔室以沉积目标材料的膜。于一些实施方式中,调整位置的步骤包含以下步骤:停止半导体处理腔室的一操作,及自磁性组件移除一个或多个磁柱。于一些实施方式中,调整位置的步骤包含以下步骤:停止半导体处理腔室的一操作,及沿着远离配置在半导体处理腔室中的一目标材料的一方向移动磁性组件的一个或多个磁柱。于一些实施方式中,通过量测在半导体基板的多个不同区处的沉积膜的一电阻率以确定在半导体基板的多个不同区中的每一者中所沉积的膜的一厚度来量测沉积膜的均匀性。于一些实施方式中,方法,进一步包括以下步骤:减小目标材料与半导体基板之间的一间距;及在减小间距之后及在自磁性组件移除两个或多个磁柱之后,操作半导体处理腔室以沉积目标材料的膜。于一些实施方式中,间距自大约60mm减小至大约53mm。于一些实施方式中,目标材料膜包含具有1%的一电阻率变化及小于10μω-cm的一电阻率的氮化钛(tin)。于一些实施方式中,多个磁柱包含永磁材料。于一些实施方式中,目标材料膜包含选自由铝(al)、铜(cu)、钨(w)、钼(mo)、钽(ta)、钛(ti)、氮化钽(tan)、氮化钨(w2n、wn或wn2)、氮化钛(tin)、氮化铝(aln)及氮化铝钪(scaln或sc

x

al

x

n)组成的群组的一材料。

115.于一些实施方式中,半导体元件的制造方法,使用一半导体处理腔室,其中半导体处理腔室包含一磁性组件,磁性组件包含位于半导体处理腔室上的多个磁柱,方法包括以下步骤:监测在半导体处理腔室中一目标材料的一侵蚀及沉积在位于半导体处理腔室中的一半导体基板上的目标材料的一膜的一厚度;当目标材料的侵蚀均匀性及/或沉积膜的厚度均匀性超过一对应临限值时,自磁性组件中移除三个磁柱,以使得目标材料以一基本均匀的方式被侵蚀,且具有一基本均匀的厚度的一膜沉积在半导体基板上;及在移除三个磁柱之后,使用磁性组件在半导体基板上执行一半导体制造制程。于一些实施方式中,方法,进一步包括以下步骤:减小目标材料与半导体基板之间的一间距;及在减小间距之后,执行半导体制造制程以沉积目标材料的膜。于一些实施方式中,间距自大约60mm减小至大约53mm。于一些实施方式中,目标材料膜包含具有1%的一电阻率变化及小于10μω-cm的一电阻率的氮化钛(tin)。于一些实施方式中,半导体制造操作变化一沉积操作或一蚀刻操作。于一些实施方式中,多个磁体包含永磁体。于一些实施方式中,自磁性组件移除多个磁柱中的三个磁柱的步骤包含移除三个磁柱以使得归因于多个磁体所致的一磁通量密度基本均匀的步骤。于一些实施方式中,多个磁柱配置成两组或更多组,且移除多个磁柱中的三个磁柱的步骤包含自一组或多组中移除多个磁柱的步骤。

116.于一些实施方式中,半导体元件的制造方法,包括以下步骤:量测由位于一真空腔室上方的一磁性组件中的多个磁体形成的一磁场,一目标置放于真空腔室中,且磁性组件包含多个磁体;沿着远离目标的一方向调整一个或多个磁体的多个位置;及使用目标在一

半导体基板上执行一溅射操作。于一些实施方式中,基于沉积在半导体基板上的目标的一膜的一厚度来调整一个或多个磁体的多个位置。于一些实施方式中,调整一个或多个磁体的多个位置以使得产生一基本均匀的磁场。

117.前述概述了若干实施例或实例的特征,以使得熟悉此项技术者可以较佳地理解本揭露的态样。熟悉此项技术者应当了解,其可以容易地将本揭露用作设计或修改其他制程及结构的基础,以供实现本文中所引入的实施例或实例的相同目的及/或达成相同优点。熟悉此项技术者亦应认识到,这些等效构造并不脱离本揭露的精神及范畴,且在不脱离本揭露的精神及范畴的情况下,熟悉此项技术者可以进行各种改变、取代及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1