一种石墨烯熔丝器件及其制备方法与流程

1.本发明涉及一种纳米半导体器件及其制备方法,尤其涉及一种石墨烯熔丝器件及其制备方法。

背景技术:

2.一次性可编程存储器是非挥发存储器的一种,在应用过程中只允许进行一次写入,信息一旦写入后无法更改。目前总的来说,它具有熔丝和反熔丝两种形态,也正是由于它的一次性编程特性,使得其在可靠性和安全方面更有优势,可被集成于fpga、prom(programmable read only memory,一次可编程只读存储器)等一次性编程存储器内部,并广泛的应用于高可靠性的航空航天、军工fpga等领域。

3.传统的电熔丝(e-fuse)为两端结构,包括阳极、阴极以及阳极和阴极相连接的细条状熔丝。器件在未编程时处于导通状态,编程过程中用瞬态的大电流将熔丝烧断,通过电流实现低阻(逻辑1)到高阻(逻辑0)的转换。熔丝在编程前等效为一个电阻,在编程后等效为一个电容。

4.传统两端熔丝器件的一个关键挑战是需要提供足够大的编程电流使得细条状熔丝中产生电迁移,大电流编程造成严重的热量积累,影响芯片的使用寿命和性能;两端熔丝需要大电流或者大电压来编程,同时它依靠热来编程,在编程过程中需要热量积累,导致编程速度慢,功耗大;

5.由于编程电压较高(15v以上),在存储单元中必须使用高压晶体管,高压晶体管的作用有两个:一是起隔离作用,二是作为编程的选通管。随着半导体工艺节点的不断降低,高压晶体管的制作会越来越困难,所以必须降低编程电压。

6.因此,如何获得低编程电压、低功耗的熔丝器件并且能够与cmos工艺兼容是当前面临的重大难题。

技术实现要素:

7.本发明针对以上现有技术中存在问题,为获得低编程电压、低功耗的熔丝器件,提出一种基于石墨烯的新型熔丝器件及其制备方法,本发明的技术方案具体如下:

8.本发明第一方面的实施例提出一种石墨烯熔丝器件,具有一衬底,在上述衬底上具有石墨烯,在上述石墨烯两端分别具有源极和漏极,上述源极和上述漏极之间形成一栅窗口,在上述栅窗口中具有一金属栅,上述金属栅与上述石墨烯之间具有一栅氧化层。

9.在本发明第一方面的实施例中,上述石墨烯为石墨烯纳米带。

10.在本发明第一方面的实施例中,上述金属栅为金属al栅,上述栅氧化层为al2o3。

11.在本发明第一方面的实施例中,上述源极或上述漏极为ti、和au组成的双层结构。

12.在本发明第一方面的实施例中,上述金属栅与上述石墨烯的延展方向垂直。

13.本发明第二方面的实施例提出了一种石墨烯熔丝器件的制备方法,包括如下步骤:

14.提供一衬底,并在上述衬底上转移石墨烯;

15.在对上述石墨烯两端沉积源极和漏极;

16.在上述源极和上述漏极之间沉积金属栅;

17.通过退火氧化,在上述石墨烯与金属栅的界面处形成栅氧化层。

18.在本发明第一方面的实施例中,通过机械剥离或cvd原位生长在所示衬底上形成石墨烯薄膜。

19.在本发明第一方面的实施例中,通过电子束曝光和电子束蒸镀形成上述源极和漏极。

20.在本发明第一方面的实施例中,在上述源极和上述漏极之间沉积金属al形成上述金属栅。

21.在本发明第一方面的实施例中,通过在120℃-180℃温度下退火30-90min在石墨烯薄膜与金属栅的界面处形成上述栅氧化层。

22.与现有一次性编程技术相比,本发明提供了一种存储的新机制,存储体为半导体沟道-石墨烯,存储机制为石墨烯击穿,通过在熔丝器件的栅极施加编程电压,使栅极到沟道的隧穿电流将沟道材料石墨烯烧断,器件从低阻状态变成电阻较大的高阻状态。

23.本发明提供的石墨烯熔丝器件可将编程电压降低到4v左右,同时降低编程电流,实现温和低功耗。

附图说明

24.通过以下参照附图对本发明的技术方案进行描述,本发明的上述以及其他目的、特征和优点将更为清楚,在附图中:

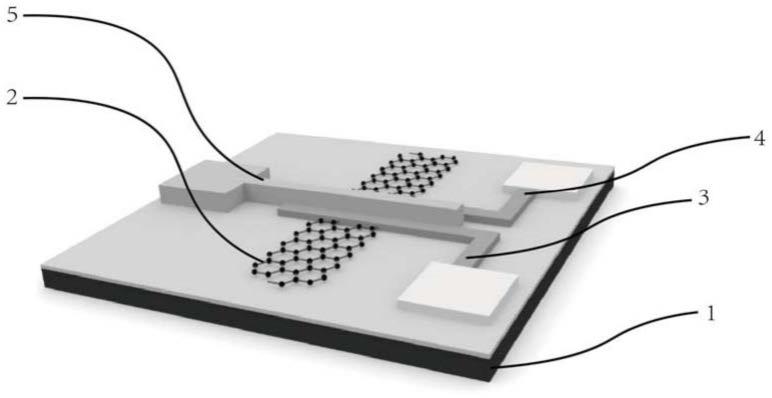

25.图1为三端熔丝器件结构图;

26.图2为金属栅结构示意图;

27.图3为在衬底上转移石墨烯沟道步骤;

28.图4为沉积源漏电极步骤;

29.图5为沉积铝栅电极步骤;

30.图6为退火氧化步骤;

31.图7为对器件编程后石墨烯熔断示意图;

32.图8为熔丝器件结构的sem表征图;

33.图9为熔丝器件的编程特性曲线;

34.图10为本发明熔丝器件的电流开关比;

35.图11为基于石墨烯材料的传统两端熔丝器件结构;

36.图12为两端熔丝的编程曲线;

37.图13为两端熔丝烧断后石墨烯的sem表征;

具体实施方式

38.下面将参照附图详细说明本发明的实施方式。在各附图中,相同的元件采用相同的附图标记来表示,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在一幅图中描述经过数个步骤后获得的半导体结构。

39.应当理解,在描述器件的结构时,当将一层、一个区域称为位于另一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或区域。并且,如果将器件翻转,该一层、一个区域将位于另一层、另一个区域“下面”或“下方”。

40.如果为了描述直接位于另一层、另一个区域上面的情形,本文将采用“a直接在b上面”或“a在b上面并与之邻接”的表述方式。在本技术中,“a直接位于b中”表示a位于b中,并且a与b直接邻接,而非a位于b中形成的掺杂区中。

41.本发明一个实施例提出一种石墨烯熔丝器件,如图1所示,具有一衬底1,在衬底1上具有石墨烯2,在石墨烯2两端分别具有源极3和漏极4,源极3和漏极4之间形成一栅窗口,在栅窗口中具有一金属栅5,金属栅5与石墨烯2的延展方向垂直,金属栅5与石墨烯2之间具有一栅氧化层6。在另一个实施例中,上述石墨烯为石墨烯纳米带。

42.金属栅5为金属al栅。在金属al栅的上表面以及金属al栅和石墨烯薄膜的交叠区域生成一层致密的氧化铝薄膜,栅窗口的结构示意图如图2所示,金属al栅和石墨烯薄膜之间的氧化铝薄膜作为熔丝存储器件的栅氧化层6。上述源极3或漏极4可为相同材料,优选为ti和au组成的双层结构。

43.在另一个实施例提出了一种石墨烯熔丝器件的制备方法,包括如下步骤:

44.为了器件的后续微纳加工和图形套刻,首先在衬底上制作标记,因为钛与衬底的粘附性较强,采用5nm钛和50nm金制作标记以防止标记脱落。

45.如图3所示,提供一氧化硅衬底1,并在氧化硅衬底1上转移一层石墨烯薄膜2,具体的,首先在铜箔上用cvd生长得到石墨烯薄膜,接着将铜箔上的石墨烯材料转移到氧化硅衬底上,通过电子束曝光(ebl)和氧等离子体刻蚀(icp)分别对石墨烯进行图形化和刻蚀得到石墨烯沟道。在其他的实施例中,可以采用机械剥离的方式转移石墨烯薄膜2,则不需要进行图形化和刻蚀,通过光学显微镜对石墨烯进行定位,之后将源漏电极搭在石墨烯材料上。

46.如图4所示,采用电子束曝光和电子束蒸镀技术,在衬底1上制作晶体管的源极3和漏极4;

47.如图5所示,通过电子束曝光和电子束蒸镀在源极3和漏4极之间沉积金属栅5;

48.进一步图6所示,通过在120℃-180℃温度下进行30-90min退火氧化,优选在150℃下烘烤40min,在石墨烯薄膜与金属栅的界面处形成一层致密的金属氧化物薄膜。其中,晶体管的栅极为金属al栅,将金属al沉积在石墨烯薄膜上,再通过退火氧化将器件在150度条件下烘烤40min,可在金属栅5的上表面以及金属栅5和石墨烯薄膜2的交叠区域生成一层致密的氧化铝薄膜,al和碳管之间的氧化铝薄膜作为熔丝存储器件的栅氧化层。

49.图8是熔丝器件结构的sem表征图,图9是本发明熔丝器件的编程特性曲线,其中纵坐标为栅电压v

gs

,横坐标为源漏电流i

ds

,源漏电压v

ds

恒定为0.1v,通过在栅极上施加正向扫描电压,达到一定的电压后,栅极到沟道的隧穿电流将石墨烯烧断,如图7所示,在栅极下方的沟道与源漏极之间的沟道之间出现小的裂缝而烧断,源漏电阻增大,表现为高阻态。从上述特性曲线可以看出,器件的编程电压在4v左右,编程电流在40na左右,编程时通过降低源漏电压v

ds

,可进一步降低编程电流。

50.图10是本发明熔丝器件结构的电流开关比,其中横坐标为时间,纵坐标为源漏电流i

ds

。红色曲线为石墨烯未烧断时(编程前)的开态特性曲线,开态电流在10-4

a左右,下面

的灰色曲线为经过图2的编程操作后的关态特性曲线,烧断后,器件从高电流转换为低电流,并且关态电流可低到10-14

a,电流开关比(存储窗口)大于9个量级,读取时可以对逻辑1和逻辑0的状态进行无误读出。

51.作为一个比较实施例,图11是基于石墨烯材料的传统两端熔丝器件结构,图12为两端熔丝的编程曲线,通过在两个金属电极上施加横向电压,发生电迁移使得石墨烯熔丝烧断,图13为两端熔丝烧断后石墨烯的sem表征,可以清楚地看到石墨烯的裂缝。从两端熔丝的编程曲线可以看出,两端熔丝的编程电压高达8v左右,同时编程电流达到毫安量级。

52.综上所述,本发明提供的石墨烯熔丝器件可将编程电压降低到4v左右,同时显著降低编程电流,实现温和低功耗。

53.虽然,上文中已经用一般性说明、具体实施方式,对本发明作了详尽的描述,但在本发明基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本发明精神的基础上所做的这些修改或改进,均属于本发明要求保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1