在晶片上生长外延层的方法与流程

在晶片上生长外延层的方法

1.本技术要求于2021年3月30日提交的韩国专利申请第10-2021-0041234号的权益,该专利申请通过引用整体并入本文,如在本文中完整阐述。

技术领域

2.实施例涉及在晶片上生长外延层的方法,更具体地,涉及在生长外延层的过程期间减轻晶片的翘曲以防止大错位凹陷(large dislocation pit,ldp)和局部光散射(lls)的发生率的方法。

背景技术:

3.晶片(诸如单晶硅晶片)经受各种处理,诸如在晶片的表面上沉积一层预定材料、蚀刻表面上的预定材料层、或对整个晶片进行热处理。这些处理可以被分为分批式(batch-type)处理(其中多个晶片被容纳于用作反应器的腔室中,并同时被处理)和单个式(single-type)处理(其中一次只有一个晶片被处理)。

4.在单个式处理中,晶片被安置在基座或卡盘上以被处理,并且已知有晶片处理装置,该晶片处理装置具有使用晶片升降杆通过通孔抬升晶片的底表面的结构,当将晶片安置在基座上或当从该基座分离经处理的晶片时,该结构形成于基座的预定部分中。

5.对于使用此类处理装置在晶片上的预定材料层的蒸汽相生长,在晶片被装载进入腔室后,当其被升降杆支撑时,预定材料层可以蒸汽相生长。

6.然而,在晶片上生长外延层的传统方法具有以下问题。

7.在使用升降杆抬升的晶片的底表面的部分处,可能生成一种被称为杆痕的污染或缺陷。考虑到此类杆痕在包括高温热的处理(例如,外延生长、热处理等)中频繁地生成,假设杆痕是因为由升降杆引起的局部热损失导致的晶片中的温度均匀性变差而产生的。而且,杆痕可能是由升降杆的表面上的硅层或颗粒导致的。

8.此外,当室温下的晶片被引入高温下的处理腔室时,由翘曲引起的大错位凹陷(ldp)的发生可能增加,并且局部光散射(lls)也可能增加。此处,“lls”是使用激光分析的缺陷之中,通过光散射观察的缺陷的通用术语,并且lls可以是通过散射观察的晶片表面上的所有缺陷。

9.为了降低上述晶片上的缺陷的发生率,已经有根据晶片的类型改变装载温度或改善装载时间的尝试。

10.然而,尚未有通过调整处理腔室中的灯的输出平衡以控制晶片的翘曲的尝试。

技术实现要素:

11.因此,本发明涉及一种在晶片上生长外延层的方法,其基本上避免了由于相关技术的限制和缺点而导致的一个或多个问题。

12.本发明的目的是提供一种调整处理腔室中的灯的输出平衡的方法,以便减少由于晶片的翘曲导致的大错位凹陷(ldp)和局部光散射(lls)的发生率。

13.本发明的附加优点、目的和特征将在下面的描述中部分阐述,并且在对以下内容进行检查后,对于本领域的普通技术人员,部分将变得显而易见,或者可以从本发明的实践中学习。本发明的目的和其他优点可以通过在本发明的书面说明书和权利要求以及附图中特别指出的结构来实现和获得。

14.为了实现这些目的和其他优点,并根据本发明的目的,如本文所体现和广泛描述的,在晶片上生长外延层的方法包括以下步骤:(a)将至少一个晶片引入处理腔室中,(b)在使用升降杆支撑晶片的同时将晶片装载到与基座邻近的区域,(c)预加热晶片,以及(d)将晶片放入基座的袋中并加热晶片,以在晶片上沉积外延层,其中,步骤(a)和(b)中的基座上方的第一灯和基座下方的第二灯的输出被设置为与步骤(c)和(d)中的第一灯和第二灯的输出不同。

15.步骤(c)和(d)中的第一灯和第二灯的输出之和可被设置为大于步骤(a)和(b)中的第一灯和第二灯的输出之和。

16.第一灯可包括中心区域中的第一-1灯和边缘区域中的第一-2灯,并且第二灯可包括中心区域中的第二-1灯和边缘区域中的第二-2灯。步骤(a)和(b)中的第一-1灯的输出比可被设置为与步骤(c)和(d)中的第一-1灯的输出比相同。

17.步骤(a)至(d)中的第一-1灯的输出比可被设置为48%到86%。

18.第一灯可包括中心区域中的第一-1灯和边缘区域中的第一-2灯,并且第二灯可包括中心区域中的第二-1灯和边缘区域中的第二-2灯。步骤(a)和(b)中的第二灯的输出比可被设置为与步骤(c)和(d)中的第二灯的输出比不同。

19.步骤(a)和(b)中的第二灯的输出比可被设置为30%到90%,并且步骤(c)和(d)中的第二灯的输出比可被设置为50%到62%。

20.第一灯可包括中心区域中的第一-1灯和边缘区域中的第一-2灯,并且第二灯可包括中心区域中的第二-1灯和边缘区域中的第二-2灯。步骤(a)和(b)中的第二-1灯的输出比可被设置为与步骤(c)和(d)中的第二-1灯的输出比不同。

21.步骤(a)和(b)中的第二-1灯的输出比可被设置为11.5%到21%,并且步骤(c)和(d)中的第二-1灯的输出比可被设置为11.5%到25%。

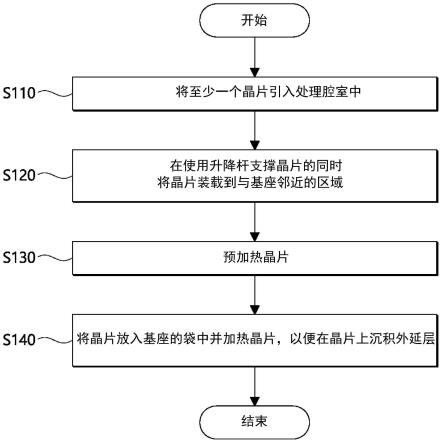

22.在步骤(a)至(d)中可通过处理腔室的晶片可视区域观察晶片的翘曲。

23.在步骤(a)至(c)的每个中,晶片可能向上翘曲。

24.应当理解,本发明的前述一般描述和以下详细描述都是示例性的和解释性的,并且旨在提供如要求保护的本发明的进一步解释。

附图说明

25.包括附图以提供对本发明的进一步理解,附图并入本技术并构成本技术的一部分,附图示出了本发明的(多个)实施例,并与说明书一起用于解释本发明的原理。在附图中:

26.图1是根据实施例在晶片上生长外延层的方法的流程图。

27.图2示出了图1中的每个步骤中晶片、基座和升降杆的相对位置。

28.图3是说明根据实施例的用于在晶片上生长外延层的装置的视图。

29.图4示出了根据实施例在晶片上生长外延层的方法的结果;并且

30.图5示出了根据比较实施例在晶片上生长外延层的方法的结果。

具体实施方式

31.在下文中,将参考附图详细描述本发明的实施例。

32.本发明的实施例可以被修改为各种形式,并且本发明的范围不应被解释为限于以下实施例。提供这些实施例以使得本公开将是透彻且完整的,并且将向本领域技术人员充分传达本公开的范围。

33.另外,以下描述中使用的诸如例如,“第一”、“第二”、“上(on)/上部(upper)/上方(above)”和“下(beneath)/下部(lower)/下方(below)”等的相对术语可用于区分任何一种物质或元件与另一种物质或元件,而不要求或暗示这些物质或元素之间的任何物理或逻辑关系或顺序。

34.硅晶片可以通过执行以下处理制备:磨削处理,该磨削处理对使用直拉方法(czochralski method)等等生长的单晶硅锭的外圆周表面进行处理;切片处理,该切片处理将单晶硅锭薄切成晶片;研磨处理,该研磨处理将晶片抛光到所需的厚度以改善平坦度;蚀刻处理,该蚀刻处理从晶片移除受损层;以及抛光处理,该抛光处理用于表面镜面光洁度和改善平坦度;并且通过最后执行清洁处理、形成氧化膜的处理和快速热处理等,如稍后将描述的,以从晶片的表面移除污染物。

35.外延晶片是通过在以此种方法生长的经抛光的晶片的表面上生长外延层制造的,外延层是另一单晶膜。此处,外延晶片可具有比经抛光的晶片更少的表面缺陷,并且可以能够用于控制杂质的浓度或类型。此外,外延层具有高纯度和极好的结晶度,因此,可具有提高成品率和改善高度集成的半导体器件的特性的优点。

36.图1是根据实施例在晶片上生长外延层的方法的流程图,图2示出了图1中的每个步骤中晶片、基座和升降杆的相对位置,并且图3是说明根据实施例的用于在晶片上生长外延层的装置的视图。下面,将参考图1至图3描述一种根据实施例在晶片上生长外延层的方法。

37.在根据实施例在晶片上生长外延层的方法中使用的装置中,外延层可在晶片上生长,该晶片被设置于设置在处理腔室内的基座200上,并且第一灯500和第二灯600可分别被设置在处理腔室的上部部分和下部部分,如图3所示。此外,温度计400a和温度计400b可分别被提供在处理腔室的上部部分和下部部分,但实施例不限于此。

38.基座200可包括作为中心轴的主轴210;从主轴210朝向晶片边缘延伸的三个支撑轴220a、220b和220c;被设置在三个支撑轴220a、220b和220c的端部以支撑晶片的第一至第三升降杆240a、240b和240c;但实施例不限于此。

39.处理腔室可包括上圆顶100和下圆顶150,其分别被提供在基座200和第一至第三升降杆240a、240b和240c的上方和下方。此处,上圆顶100内部的区域和下圆顶150内部的区域可形成用于生长外延层的空间。此外,进气口(入口)和出气口(出口)可被形成于处理腔室中,以便形成薄膜,诸如在晶片表面上的外延层。

40.尽管未示出,晶片可视区可被提供于上圆顶100内,并且可通过该晶片可视区观察到在沉积外延层的过程期间的晶片的翘曲。

41.在晶片上生长外延层所需的运载气体,诸如氢气和/或气源(source gas)(诸如硅

烷(sihcl3或sih2cl2))(或反应物气体),可通过进气口(入口)引入以在晶片上形成外延层,并且在形成外延层后,剩余气体可通过出气口(出口)排出。如所说明的,进气口(入口)和出气口(出口)可形成为面向彼此,但实施例不限于此。

42.此外,由于基座200被提供在进气口(入口)和出气口(出口)之间,并且由于进气口(入口)和出气口(出口)被定位于与基座200的上表面基本相同的高度,通过入气口(入口)引入的气源可在晶片的表面上流动。

43.为了控制处理腔室内部的温度,光从分别被设置在基座200的上方和下方的第一灯500和第二灯600放出,分别照向基座200的上部区域和下部区域,并且从第一灯500和第二灯600放出的辐射热可被转移到晶片上。此处,第一灯500可称为上灯,且第二灯600可称为下灯。

44.在基座200的上部区域中提供的第一灯500可被分为提供在中心区域中的第一-1灯500a和提供在边缘区域中的第一-2灯500b,并且在基座200的下部区域中提供的第二灯600可被分为提供在中心区域中的第二-1灯600a和提供在边缘区域中的第二-2灯600b。

45.在根据实施例在晶片上生长外延层的方法中,在将晶片引入到处理腔室中、装载晶片、预加热晶片、和沉积外延层的步骤中,上文描述的灯的输出被调整。下文将对此进行详细描述。

46.首先,在步骤s110中,至少一个晶片被引入到处理腔室中。

47.在图2中,首先执行了从处理腔室中取出晶片(在该晶片上已经完成了外延层沉积过程)并将新晶片引入到处理腔室中的过程(交换过程)。之后,升降杆被带至靠近晶片的底表面(杆靠近(pinclose)),并且升降杆被带至接触晶片的底表面(杆接触(pincontact))以支撑晶片。

48.然后,在步骤s120中,在使用升降杆支撑晶片的同时将晶片装载到与基座邻近的区域。图2中,支撑晶片的升降杆被降低以便将晶片装载到与基座邻近的区域。

49.上述引入步骤和装载步骤的组合可被称为转移晶片的过程,并且稍后将描述的预加热过程和沉积过程的组合可被称为加热过程。此外,如稍后将讨论的,转移晶片的过程中的灯的输出可以和加热过程中的灯的输出不同。例如,在转移过程中,晶片的环境温度可被设置至800℃,并且在加热过程中,晶片的环境温度可被设置至900℃。

50.此处,在上述的引入步骤和装载步骤中,第一灯和第二灯的输出可保持相同。然而,引入步骤和装载步骤中的第一灯和第二灯的输出可以和预加热过程和沉积过程中的第一灯和第二灯的输出不同,如稍后将描述的。具体地,预加热过程和沉积过程中的第一灯和第二灯的输出之和可以被设置为大于引入步骤和装载步骤中的第一灯和第二灯的输出之和。例如,引入步骤和装载步骤中的第一灯和第二灯的总输出可以是30kw(千瓦),并且预加热步骤和沉积步骤中的第一灯和第二灯的总输出可以是60kw。

51.此处,引入步骤和装载步骤中的第一-1灯的输出比可以被设置为与预加热步骤和沉积步骤中的第一-1灯的输出比相同。例如,第一-1灯的输出比可以保持在48%到86%。此处,当第一-1灯的输出比是48%到86%时,意味着第一-1灯的输出比占据第一灯的总输出的48%到86%。

52.然后,在步骤s130处,晶片被预加热。如图2中所示的,在预加热过程中,晶片被带至靠近基座但与基座分隔开,并且稍后将描述的沉积外延层的过程可在晶片被带至接触基

座以便被插入到袋中(入袋(in-pocket))之后执行。

53.然后,在步骤s140处,将晶片放入基座的袋中并加热晶片,以便在晶片上沉积外延层。

54.在预加热过程和沉积过程中,除了从第一灯和第二灯放出的辐射热到晶片的直接转移之外,从经加热的基座放出的热可被转移至晶片,导致晶片的翘曲,特别是在向上的方向中。

55.此外,上述引入步骤和装载步骤中的第二灯的输出比可被设置为与上述预加热步骤和沉积步骤中的灯的输出比不同。例如,引入步骤和装载步骤中的第二灯的输出比可被设置为30%到90%,并且预加热步骤和沉积步骤中的第二灯的输出比可被设置为50%到62%。此处,当第二灯的输出比是30%到90%时,意味着第二灯的输出比占据第一灯和第二灯的总输出的30%到90%。当第二灯的输出比是50%到62%时,意味着第二灯的输出比占据第一灯和第二灯的总输出的50%到62%。

56.此外,上述引入步骤和装载步骤中的第二-1灯的输出比可被设置为与上述预加热步骤和沉积步骤中的第二-1灯的输出比不同。例如,上述引入步骤和装载步骤中的第二-1灯的输出比可被设置为11.5%到21%,并且上述预加热步骤和装载步骤中的第二-1灯的输出比可被设置为11.5%到25%。此处,当第二-1灯的输出比是11.5%到21%时,意味着第二-1灯的输出比占据第二灯的总输出的11.5%到21%。当第二-1灯的输出比是11.5%到25%时,意味着第二-1灯的输出比占据第二灯的总输出的11.5%到25%。

57.在上文描述的引入过程、装载过程、预加热过程和沉积过程期间,可以通过上文描述的晶片可视区域观察到晶片的翘曲。例如,图3中,晶片可能向上翘曲。当观察到晶片的翘曲时,可重新调整上文描述的灯的输出。

58.在晶片被装载到基座上之前,晶片的翘曲可能由于灯的辐射热等等发生,并且在装载过程之后的预加热过程和沉积过程中,除了由于灯的辐射热的翘曲之外,可能由由于晶片与基座接触的热转移生成缺陷。

59.在实施例中,引入晶片的过程和装载晶片的过程中的灯的输出被设置为与预加热晶片的过程和沉积晶片的过程中的灯的输出不同,并且通过处理腔室的晶片可视区域实时观察晶片的翘曲,以便将输出设置为彼此不同,从而减少晶片的缺陷,诸如翘曲。

60.图4示出了根据实施例在晶片上生长外延层的方法的结果,并且图5示出了根据比较实施例在晶片上生长外延层的方法的结果。

61.如在实施例中,当在晶片上生长外延层期间当转移过程中的灯的输出被设置为与加热过程中的灯的输出不同时,相较于当灯的输出被设置为相同时,晶片的翘曲可以减轻。此外,即使当转移过程和加热过程中的每个的灯的输出被设置为彼此不同时,在遵循根据上述实施例的条件的情况下,可以获得具有减少的翘曲的晶片。

62.图4中,在转移过程中,第二灯的输出比被设置为30%,第一-2灯的输出比被设置为77%,并且第二-1灯的输出比被设置为25%;在加热过程中,第二灯的输出比被设置为50%,第一-2灯的输出比被设置为48%,并且第二-1灯的输出比被设置为21%。

63.图5中,在转移过程中,第二灯的输出比被设置为58%,第一-2灯的输出比被设置为86%,并且第二-1灯的输出比被设置为9.5%;在加热过程中,第二灯的输出比被设置为50%,第一-2灯的输出比被设置为60%,并且第二-1灯的输出比被设置为14.5%。

64.如所示的,根据图4的实施例中的在晶片上生长外延层的方法,转移过程和加热过程中的灯的输出比受到控制的晶片相较于通过根据图5的比较实施例的过程制造的晶片表现出减少的翘曲。

65.根据根据实施例的在晶片上生长外延层的方法,当转移过程中的灯的输出被设置为与加热过程中的灯的输出不同时,相较于当灯的输出被设置为相同时,晶片的翘曲可以减轻。此外,即使当转移过程和加热过程中的每一个中,灯的输出被设置为不同时,在遵循根据上述实施例的条件的情况下,可以获得具有减少的翘曲的晶片。

66.对本领域技术人员显而易见的是,可以对本发明作出各种修改和变化而不背离本发明的精神或范围。因此,本发明旨在涵盖本发明的多种修改和变化,只要这些修改和变化在所附权利要求书及其等效方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1