半导体器件及其制备方法、电子设备与流程

本技术涉及半导体,尤其涉及有一种半导体器件及其制备方法、电子设备。

背景技术:

1、考虑到源漏外延工艺中的高温处理步骤对互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)中的栅极叠层(gate stack)的性能以及可靠性的影响,半导体制备工艺过程大多从先制备栅极再制备源极和漏极,转变为先制备牺牲栅后制备源极和漏极,再将牺牲栅替换为金属栅极,也即转变为替代金属栅工艺(replacement metal gate,rmg)。

2、rmg工艺虽然能够避免源漏外延工艺对栅极的影响,但也会使半导体器件结构更加复杂,从而使器件表面的形貌更加复杂,使得器件的平坦化工艺受到更大挑战。器件在平坦化工艺后,若表面高低不平,则会对后续工艺产生不良影响,最终有可能导致器件失效,良率降低。

技术实现思路

1、本技术实施例提供一种半导体器件及其制备方法、电子设备,用于改善半导体器件平坦化工艺后表面高低不平的问题,以提高半导体器件的良率。

2、为达到上述目的,本技术的实施例采用如下技术方案:

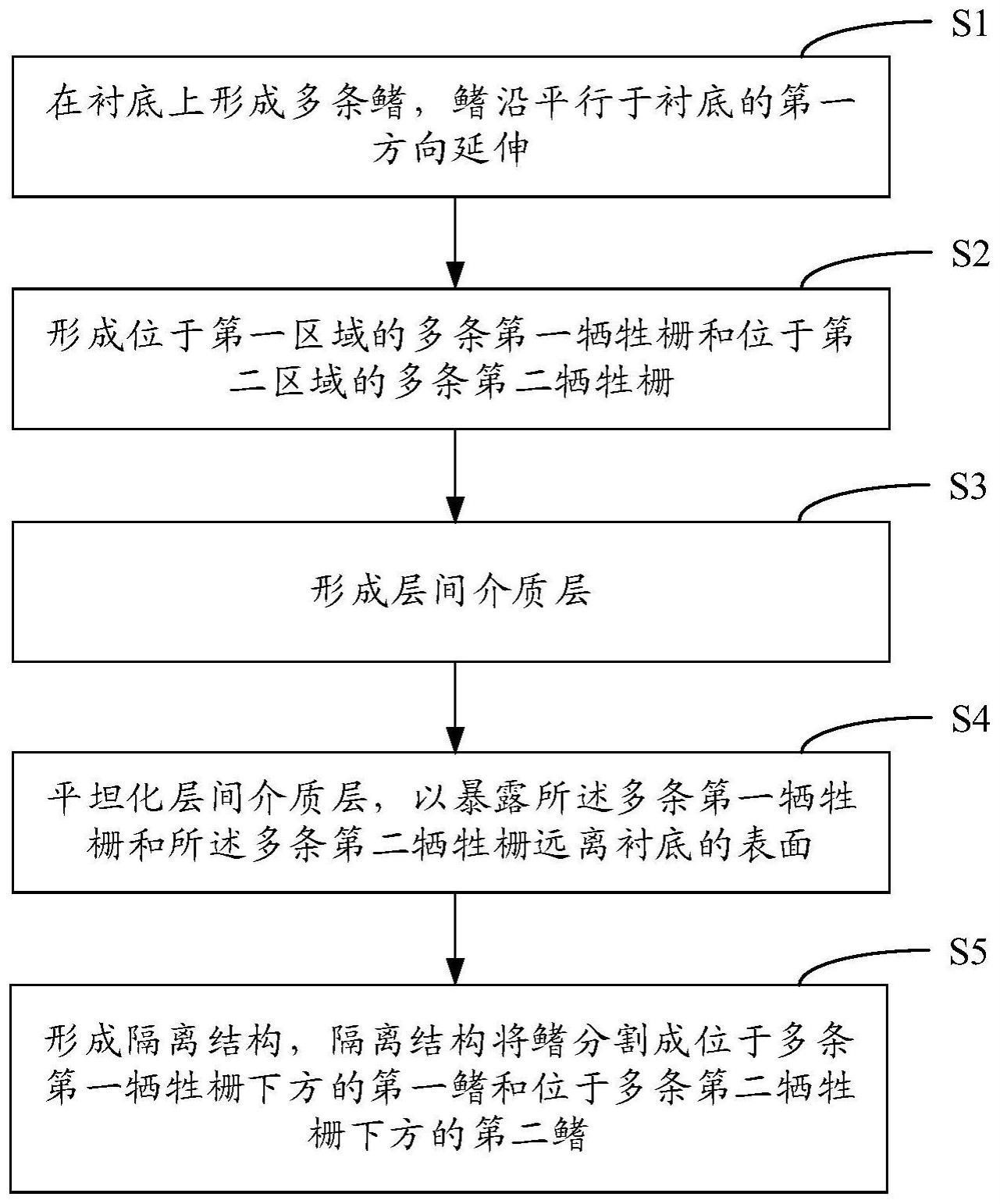

3、第一方面,提供了一种半导体器件的制备方法,该制备方法包括:在衬底上形成多条鳍,所述鳍沿平行于所述衬底的第一方向延伸;形成位于第一区域的多条第一牺牲栅和位于第二区域的多条第二牺牲栅,所述第一牺牲栅和所述第二牺牲栅沿平行于所述衬底的第二方向延伸,所述第一方向和所述第二方向相交叉;所述多条第一牺牲栅和所述多条第二牺牲栅跨设在所述多条鳍上,且所述第二区域在所述第一区域的周围;形成层间介质层,所述层间介质层覆盖所述多条第一牺牲栅和所述多条第二牺牲栅;平坦化所述层间介质层,以暴露所述多条第一牺牲栅和所述多条第二牺牲栅远离所述衬底的表面;形成隔离结构,所述隔离结构将所述鳍分割成位于所述多条第一牺牲栅下方的第一鳍和位于所述多条第二牺牲栅下方的第二鳍,所述隔离结构围绕多条所述第一鳍和所述多条第一牺牲栅。

4、本技术一些实施例所提供的半导体器件的制备方法中,先在衬底上设置鳍、且在第一区域上设置有第一牺牲栅,在第二区域上设置有第二牺牲栅,然后形成层间介质层,对层间介质层进行平坦化处理,最后形成隔离结构将鳍划分成第一鳍和第二鳍。这样,在进行平坦化处理之前,半导体器件中鳍、第一牺牲栅和第二牺牲栅在衬底上的分布较为均匀,因此在层间介质层平坦化过程中,不容易因衬底上电路结构分布不均匀,不同区域研磨速度不同,出现半导体器件的表面高度差异较大,表面高度不均匀的问题,从而有效的提高半导体器件的良率,提高半导体器件的性能。

5、同时,与相关技术中先制备电路结构,再在相邻的两个电路结构间隙中设置虚设结构,电路结构与虚设结构之间的间隙较大的情况相比,本技术一些实施例所提供的半导体器件的制备方法中,间隔在第一鳍和第二鳍,第一牺牲栅和第二牺牲栅之间的隔离结构的尺寸可以更小,从而不容易对后续其他平坦化工艺产生影响,进一步提高了半导体器件的良率,提高了半导体器件的性能。

6、在一些实施例中,所述形成隔离结构,包括:刻蚀第一预设区域内的第二牺牲栅和鳍,形成第一隔离槽;沿所述第二方向,所述第一预设区域位于所述多条第一牺牲栅的一侧,所述第一隔离槽沿所述第一方向延伸。在所述第一隔离槽内形成第一隔离部。刻蚀第二预设区域内的层间介质层和鳍,形成第二隔离槽;沿所述第一方向,所述第二预设区域位于所述多条第一牺牲栅的一侧,所述第二隔离槽沿所述第二方向延伸。在所述第二隔离槽内形成第二隔离部。其中,所述隔离结构包括所述第一隔离部和所述第二隔离部。这样,利用第一隔离部和第二隔离部能够较好的将第一牺牲栅和第二牺牲栅间隔开,从而在将第一牺牲栅替换成第一栅,将第二牺牲栅替换成第二栅后,将第一栅和第二栅更好的间隔开,保证第一栅的使用性能。

7、在一些实施例中,所述第一隔离部在所述第二方向上的尺寸小于或等于,相邻两个鳍的中心线之间的距离的二倍;和/或,所述衬底上设有至少一个第一牺牲栅组,所述第一牺牲栅组包括多条所述第一牺牲栅;所述第二隔离部在所述第一方向上的尺寸小于或等于,与所述第二隔离部相邻的第一牺牲栅组中相邻两个第一牺牲栅的中心线之间的距离的二倍。这样,第一隔离部在第二方向上的尺寸较小,第二隔离部在第一方向上的尺寸也较小,从而在后续进行其他平坦化工艺过程中,不容易因第一隔离部和/或第二隔离部的设置,导致半导体器件表面出现明显的高度差异,从而进一步提高了半导体器件的良率。

8、在一些实施例中,所述刻蚀第一预设区域内的第二牺牲栅和鳍,形成第一隔离槽,包括:在所述层间介质层上形成第一掩膜层,所述第一掩膜层包括第一开口,所述第一开口沿所述第一方向延伸,且暴露多条所述第二牺牲栅靠近所述多条第一牺牲栅的端部。经由所述第一开口,刻蚀多条所述第二牺牲栅所暴露的端部,以及所述端部下方的鳍,形成第一隔离槽。

9、在一些实施例中,在所述形成多条第一牺牲栅和多条第二牺牲栅之前,所述制备方法还包括:在所述衬底上形成绝缘层,所述鳍的部分嵌入所述绝缘层中,其余部分凸出于所述绝缘层的上表面。所述经由所述第一开口,刻蚀所述多条第二牺牲栅所暴露的端部,以及所述端部下方的鳍,形成第一隔离槽,包括:刻蚀所述第一开口所暴露的多条所述第二牺牲栅的端部,暴露出所述端部下方的鳍。刻蚀所述鳍,形成位于所述绝缘层中的第一凹陷,和位于所述绝缘层上的第二凹陷。其中,所述第一隔离槽包括所述第一凹陷和所述第二凹陷。

10、在一些实施例中,所述刻蚀第二预设区域内的层间介质层和鳍,形成第二隔离槽,包括:在所述层间介质层上形成第二掩膜层,所述第二掩膜层包括第二开口,所述第二开口沿所述第二方向延伸,且暴露第一目标牺牲栅和第二目标牺牲栅之间的层间介质层;所述第一目标牺牲栅和所述第二目标牺牲栅为,沿所述第一方向,所述多条第一牺牲栅和所述多条第二牺牲栅中距离最近的第一牺牲栅和第二牺牲栅。经由所述第二开口,刻蚀所暴露的层间介质层,以及所述层间介质层下方的鳍,形成第二隔离槽。这样,在形成第二隔离槽的过程中,刻蚀的材料较少,刻蚀工艺简单,有利于提高半导体器件的制备效率。

11、在一些实施例中,在所述形成层间介质层之前,所述制备方法还包括:形成介质层,所述介质层覆盖所述多条第一牺牲栅和所述多条第二牺牲栅在所述第一方向上相对的两个侧面。在所述鳍上形成源极和漏极;沿所述第一方向,所述源极和所述漏极分别位于所述第一牺牲栅的两侧,以及所述第二牺牲栅的两侧。形成刻蚀停止层,所述刻蚀停止层覆盖所述介质层,以及所述源极和所述漏极。

12、在一些实施例中,所述经由所述第二开口,刻蚀所暴露的层间介质层,以及所述层间介质层下方的鳍,形成第二隔离槽,包括:刻蚀所述第二开口所暴露的层间介质层,暴露出所述层间介质层下方的刻蚀停止层。刻蚀所暴露的刻蚀停止层,暴露出所述刻蚀停止层下方的源极或漏极。刻蚀所暴露的源极或漏极,以及所述源极或所述漏极下方的鳍,形成所述第二隔离槽。

13、在一些实施例中,所述第二开口还暴露所述第一目标牺牲栅靠近所述第二目标牺牲栅的部分表面,以及所述第二目标牺牲栅靠近所述第一目标牺牲栅的部分表面。在所述经由所述第二开口,刻蚀所暴露的层间介质层,以及所述层间介质层下方的鳍,形成第二隔离槽的过程中,还刻蚀所述第一目标牺牲栅和所述第二目标牺牲栅。这样,第二开口在第一方向上的尺寸较大,图案化第二掩膜层的工艺较为简单。同时,第二隔离槽在第一方向上的尺寸也较大,第二隔离部的尺寸也随之较大,从而能够更好的将第一牺牲栅和第二牺牲栅间隔开,也将后续形成的第一栅和第二栅间隔开。

14、在一些实施例中,覆盖所述第一目标牺牲栅靠近所述第二目标牺牲栅的侧面的介质层为第一目标介质层,覆盖所述第一目标介质层的刻蚀停止层为第一目标刻蚀停止层,覆盖所述第二目标牺牲栅靠近所述第一目标牺牲栅的侧面的介质层为第二目标介质层,覆盖所述第二目标介质层的刻蚀停止层为第二目标刻蚀停止层。所述第二开口还暴露所述第一目标介质层、所述第一目标刻蚀停止层、所述第二目标介质层和所述第二目标刻蚀停止层远离所述衬底的端面。

15、所述刻蚀第二预设区域内的层间介质层和鳍,形成第二隔离槽,包括:经由所述第二开口,同步刻蚀所述第一目标牺牲栅、所述第一目标介质层、所述第一目标刻蚀停止层、所述第二目标牺牲栅、所述第二目标介质层、所述第二目标刻蚀停止层,以及所述第一目标牺牲栅和所述第二目标牺牲栅之间的层间介质层,形成第三凹陷;沿垂直于所述衬底的方向,所述第三凹陷的底面与位于所述第一目标牺牲栅和所述第二目标牺牲栅之间的源极或漏极的上表面之间具有间距。刻蚀剩余的第一目标介质层、第一目标刻蚀停止层、第二目标介质层和第二目标刻蚀停止层。刻蚀所述第一目标牺牲栅和所述第二目标牺牲栅之间剩余的层间介质层,暴露出所述层间介质层下方的刻蚀停止层。刻蚀剩余的第一目标牺牲栅和第二目标牺牲栅、暴露出的刻蚀停止层、所述刻蚀停止层下方的源极或漏极,以及所述源极或所述漏极下方的鳍,形成第二隔离槽。

16、在一些实施例中,在形成隔离结构之前,沿所述第二方向,所述多条第一牺牲栅与所述多条第二牺牲栅之间存在间隙。所述间隙小于或等于相邻两条鳍的中心线之间的距离。这样,各条鳍上可以均设置有第一牺牲栅或第二牺牲栅,使得第一牺牲栅和第二牺牲栅在衬底上均匀分布,从而有利于改善因衬底上牺牲栅结构分布不均匀,导致的半导体器件在平坦化工艺后表面高低不平的问题,提高半导体器件的良率,提高半导体器件的性能。

17、在一些实施例中,所述制备方法还包括:将所述第一牺牲栅替换成第一栅,将所述第二牺牲栅替换成第二栅。

18、第二方面,提供了一种半导体器件,该半导体器件包括衬底、多条第一鳍和多条第二鳍、多条第一栅和多条第二栅、层间介质层和隔离结构。多条第一鳍和多条第二鳍,设于所述衬底上,且沿平行于所述衬底的第一方向延伸。多条第一栅和多条第二栅,沿平行于所述衬底的第二方向延伸,所述第一方向与所述第二方向相交叉;所述多条第一栅跨设在所述多条第一鳍上,所述多条第二栅跨设在所述多条第二鳍上。所述层间介质层覆盖所述多条第一栅之间的区域和所述多条第二栅之间的区域,暴露出所述多条第一栅和所述多条第二栅远离所述衬底的表面。隔离结构,间隔所述多条第一鳍和所述多条第二鳍,以及间隔所述多条第一栅和所述多条第二栅,且围绕所述多条第一鳍和所述多条第一栅。其中,所述多条第一鳍和所述多条第二鳍材料相同且同层设置,所述多条第一栅和所述多条第二栅材料相同且同层设置。

19、本技术一些实施例所提供的半导体器件中,第一鳍和第二鳍材料相同且同层设置,第一栅和第二栅材料相同,且同层设置,即第一鳍和第二鳍均由鳍切割得到,第一栅和第二栅同时制备。因此,在半导体器件的制备过程中,是在衬底上先均匀铺设鳍,形成第一栅所对应的第一牺牲栅和第二栅对应的第二牺牲栅,然后形成层间介质层,平坦化层间介质层,最后形成隔离结构将鳍分割成第一鳍和第二鳍,且将第一牺牲栅和第二牺牲栅间隔开来的。这样,在进行平坦化处理之前,半导体器件中鳍、第一牺牲栅和第二牺牲栅在衬底上的分布较为均匀,因此在层间介质层平坦化过程中,不容易因衬底上电路结构分布不均匀,不同区域研磨速度不同,出现半导体器件的表面高度差异较大,表面高度不均匀的问题,从而有效的提高半导体器件的良率,提高半导体器件的性能。

20、同时,与相关技术中先制备电路结构,再在相邻的两个电路结构间隙中设置虚设结构,电路结构与虚设结构之间的间隙较大的情况相比,本技术一些实施例所提供的半导体器件中,间隔在第一鳍和第二鳍,第一牺牲栅和第二牺牲栅之间的隔离结构的尺寸可以更小,从而不容易对后续其他平坦化工艺产生影响,进一步提高了半导体器件的良率,提高了半导体器件的性能。

21、在一些实施例中,所述隔离结构包括第一隔离部和第二隔离部。第一隔离部,沿所述第一方向延伸,且沿所述第二方向,所述第一隔离部位于所述多条第一栅的一侧。第二隔离部,沿所述第二方向延伸,且沿所述第一方向,所述第二隔离部位于所述多条第一栅的一侧。这样,在第一方向和第二方向上均可以较好的将第一栅和第二栅间隔开。

22、在一些实施例中,所述第一隔离部包括沿所述第一方向间隔排列的多个隔离子部,所述隔离子部位于所述第二栅的延长线上,且所述隔离子部在所述第一方向上的宽度与所述第二栅在所述第一方向上的宽度相等。

23、在一些实施例中,半导体器件还包括绝缘层。所述多条第一鳍和所述多条第二鳍的部分嵌入所述绝缘层中,其余部分凸出于所述绝缘层的上表面。所述隔离子部包括嵌入所述绝缘层中的第一部分和位于所述绝缘层上的第二部分;所述第一部分在所述第二方向上的尺寸与所述第二鳍在所述第二方向上的尺寸相等。

24、在一些实施例中,沿所述第一方向,所述多条第一栅和所述多条第二栅中距离最近的第一栅和第二栅,分别为第一目标栅和所述第二目标栅。所述半导体器件还包括:覆盖所述第一目标栅靠近所述第二目标牺牲栅的侧面的第一目标介质层;覆盖所述第一目标介质层的第一目标刻蚀停止层;覆盖所述第二目标栅靠近所述第一目标牺牲栅的侧面的第二目标介质层;覆盖所述第二目标介质层的第二目标刻蚀停止层。其中,沿所述第一方向,所述第二隔离部位于所述第一目标刻蚀停止层和所述第二目标刻蚀停止层之间。

25、在一些实施例中,所述半导体器件还包括:第一介质层和第二介质层,分别覆盖所述第二隔离部在所述第一方向上相对的两个侧面。第一刻蚀停止层和第二刻蚀停止层,所述第一刻蚀停止层覆盖所述第一介质层,所述第二刻蚀停止层覆盖所述第二介质层。

26、在一些实施例中,所述隔离结构包括两个所述第一隔离部和两个所述第二隔离部,沿所述第二方向,两个所述第一隔离部分别位于所述多条第一栅的相对两侧;沿所述第一方向,两个所述第二隔离部分别位于所述多条第一栅的相对两侧;两个所述第一隔离部和两个所述第二隔离部相连成框形。

27、在一些实施例中,所述半导体器件还包括第三介质层、源极和漏极,以及第三刻蚀停止层。第三介质层,覆盖所述多条第一栅和所述多条第二栅在所述第一方向上的相对的两个侧面;源极和漏极,位于所述多条第一鳍和所述多条第二鳍上;沿所述第一方向,所述源极和所述漏极分别位于所述第一栅的两侧和所述第二栅的两侧;第三刻蚀停止层,覆盖所述第三介质层、所述源极和所述漏极。

28、在一些实施例中,所述第一隔离部在所述第二方向上的尺寸小于或等于,相邻两个第一鳍的中心线之间的距离的二倍;和/或,所述衬底上设有至少一个第一栅组,所述第一栅组包括多条所述第一栅;所述第二隔离部在所述第一方向上的尺寸小于或等于,与所述第二隔离部相邻的第一栅组中相邻两个第一栅的中心线之间的距离的二倍。通过这样设置,第一隔离部和/或第二隔离部的尺寸较小,在后续进行其他平坦化工艺时,不容易因第一隔离部和/或第二隔离部与第一栅、第二栅的材料不同,出现平坦化工艺后半导体器件表面高低不平的问题,有效的提高了半导体器件的良率。

29、在一些实施例中,所述多条第一鳍和所述多条第二鳍的宽度相等;和/或,所述多条第一鳍和所述多条第二鳍中任意相邻两条鳍之间的间距相等;和/或,所述多条第二栅的宽度相等;和/或,任意相邻两条所述第二栅之间的间距相等。这样,第一鳍、第二鳍以及第二栅的分别较为均匀,在制备半导体器件时,鳍和第二牺牲栅的分布较为均匀,从而有效的改善了因结构分布不均匀导致研磨速率不同,半导体器件表面高度不同的问题,提高了半导体器件的良率。

30、第三方面,提供了一种电子设备,该电子设备包括印刷电路板和上述第二方面任一实施例所述的半导体器件;所述半导体器件和所述印刷线路板电连接。

- 还没有人留言评论。精彩留言会获得点赞!