包括通路结构的半导体器件的制作方法

包括通路结构的半导体器件

1.相关申请的交叉引用

2.本技术要求于2021年7月5日在韩国知识产权局提交的韩国专利申请no.10-2021-0087703的优先权,其公开内容通过引用整体合并于此。

技术领域

3.一些示例实施例涉及半导体器件和用于制造该半导体器件的方法。具体地,一些示例实施例涉及包括通路结构的半导体器件和/或用于制造该半导体器件的方法。

背景技术:

4.半导体器件根据其诸如小型化、多功能化、制造成本低等中的一种或更多种之类的特性在电子行业中作为重要元件备受关注。半导体器件可以分类为存储逻辑数据的半导体存储器件、用于对逻辑数据进行算术处理的半导体逻辑器件、包括存储元件和逻辑元件的混合半导体器件等。随着电子行业的进步,对半导体器件的特性的需求/期望正在逐渐增加。例如,对半导体器件的高可靠性、高速、多功能性等中的一种或更多种的需求或期望正在逐渐增加。为了满足这些要求的特性,半导体器件中的结构变得越来越复杂。另外,半导体器件的集成度变得越来越高。

技术实现要素:

5.本发明构思的示例实施例提供了具有相对小的尺寸的半导体器件。

6.根据一些示例实施例的半导体器件包括:衬底;绝缘结构,所述绝缘结构覆盖所述衬底;晶体管,所述晶体管位于所述衬底和所述绝缘结构之间;通路绝缘层,所述通路绝缘层延伸穿过所述绝缘结构和所述衬底;多个通路结构,所述多个通路结构延伸穿过所述通路绝缘层;多个导电结构,所述多个导电结构分别连接到所述多个通路结构;以及多个凸块,所述多个凸块分别连接到所述导电结构。

7.根据一些示例实施例的半导体器件包括:衬底;绝缘结构,所述绝缘结构覆盖所述衬底的第一表面;晶体管,所述晶体管位于所述衬底的所述第一表面上;通路绝缘层,所述通路绝缘层延伸穿过所述衬底和所述绝缘结构;以及多个第一通路结构,所述多个第一通路结构被所述通路绝缘层围绕。

8.根据一些示例实施例的半导体器件包括:衬底;绝缘结构,所述绝缘结构覆盖所述衬底;第一晶体管,所述第一晶体管位于晶体管区域中并位于所述衬底和所述绝缘结构之间;以及第一通路结构,所述第一通路结构位于通路区域中并且延伸穿过所述衬底和所述绝缘结构。所述第一晶体管与所述通路区域分开。所述晶体管区域位于所述通路区域之间。

9.根据一些示例实施例的用于制造半导体器件的方法包括:在衬底上形成晶体管;形成覆盖所述晶体管的绝缘结构;通过蚀刻所述绝缘结构和所述衬底形成沟槽;在所述沟槽中形成通路绝缘层;在所述通路绝缘层中形成通孔;以及在所述通孔中形成通路结构。

附图说明

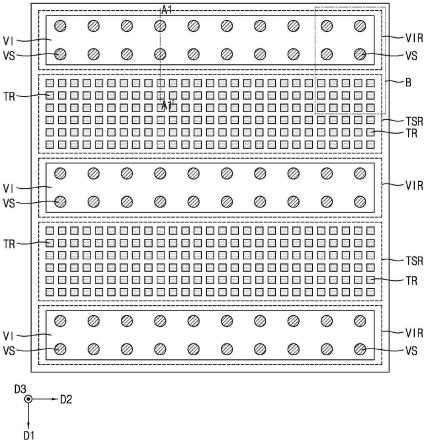

10.图1a是根据本公开的一些示例实施例的半导体器件的俯视图。

11.图1b是沿着图1a中的线a1-a1'截取的截面图。

12.图1c是图1a的部分b的放大图。

13.图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h和图2i是说明用于制造根据图1a、图1b和图1c的半导体器件的方法的截面图。

14.图3是根据本公开的一些示例实施例的半导体器件的俯视图。

15.图4a是根据本公开的一些示例实施例的半导体器件的俯视图。

16.图4b是沿着图4a中的线a2-a2'截取的截面图。

17.图4c是沿着图4a中的线c2-c2'截取的截面图。

18.图5a、图5b、图5c、图5d、图5e和图5f是说明用于制造根据图4a、图4b和图4c的半导体器件的方法的截面图。

19.图6是根据本公开的一些示例实施例的半导体器件的俯视图。

20.图7是根据本公开的一些示例实施例的半导体器件的俯视图。

21.图8是根据本公开的一些示例实施例的半导体器件的俯视图。

22.图9是根据本公开的一些示例实施例的半导体器件的截面图。

23.图10a、图10b和图10c是说明用于制造根据图9的半导体器件的方法的截面图。

24.图11是根据本公开的一些示例实施例的半导体器件的截面图。

25.图12是根据本公开的一些示例实施例的半导体器件的截面图。

具体实施方式

26.图1a是根据本公开的一些示例实施例的半导体器件的俯视图。图1b是沿着图1a中的线a1-a1'截取的截面图。图1c是图1a的部分b的放大图。

27.参照图1a和图1b,半导体器件可以包括衬底100。衬底100可以具有沿着由第一方向d1和第二方向d2限定的平面延伸的板的形式。第一方向d1和第二方向d2可以彼此相交。例如,第一方向d1和第二方向d2可以彼此垂直地相交。在一些示例实施例中,衬底100可以是诸如单晶衬底的半导体衬底。例如,衬底100可以包括硅、锗、硅锗、gap或gaas,并且可以是掺杂的或未掺杂的。

28.半导体器件可以包括通路区域vir和晶体管区域tsr。通路区域vir和晶体管区域tsr可以互不相同。通路区域vir和晶体管区域tsr可以是在由第一方向d1和第二方向d2限定的平面上彼此分开的区域。通路区域vir和晶体管区域tsr可以在第二方向d2上延伸;然而,示例实施例不限于此。通路区域vir和晶体管区域tsr可以在第一方向d1上交替地布置。晶体管区域tsr可以设置在通路区域vir之间。

29.可以提供覆盖衬底100的第一表面101的绝缘结构ins。绝缘结构ins的第一表面ins_1可以接触(例如,直接接触)衬底100的第一表面101。当从根据图1b的视角观看时,衬底100的第一表面101可以是衬底100的底表面,并且绝缘结构ins的第一表面ins_1可以是绝缘结构ins的顶表面。衬底100的第一表面101可以是或对应于衬底100的有源表面。衬底100可以设置在绝缘结构ins上。绝缘结构ins可以包括覆盖衬底100的第一表面101的第一绝缘层110和覆盖第一绝缘层110的底表面的掩模层ma。在一些示例实施例中,第一绝缘层

110和掩模层ma均可以为多个层。第一绝缘层110和掩模层ma可以包括绝缘材料。在一些示例实施例中,与所示的情况不同,绝缘结构ins可以不包括掩模层ma,并且可以由第一绝缘层110单独地构成或只对应于第一绝缘层110。

30.晶体管tr可以设置在绝缘结构ins和衬底100之间。晶体管tr可以是平面晶体管;然而,示例实施例不限于此。晶体管tr可以是nfet晶体管或pfet晶体管;然而,示例实施例不限于此。例如,晶体管tr可以是构成存储器件、逻辑器件或图像传感器器件或者包括在存储器件、逻辑器件或图像传感器器件中的单元晶体管和/或外围晶体管。晶体管tr可以仅设置在晶体管区域tsr中。晶体管tr可以不设置在通路区域vir中。晶体管tr可以与通路区域vir间隔开。晶体管tr可以被绝缘结构ins的第一绝缘层110覆盖。晶体管tr可以设置在衬底100的第一表面101上。尽管图1a示出了晶体管tr以常规方式布置,但是示例实施例不限于此。

31.晶体管tr可以包括杂质区dr以及设置在杂质区dr之间的沟道和栅极结构。栅极结构可以包括栅极间隔物gs以及设置在栅极间隔物gs之间的栅极绝缘膜gi、栅电极ge和栅极覆盖膜gp。因为在衬底100中注入杂质,所以可以形成杂质区dr。栅极间隔物gs、栅极绝缘膜gi和栅极覆盖膜gp可以包括绝缘材料。栅电极ge可以包括导电材料。晶体管tr的结构不限于所示的且上面描述的结构。在一些示例实施例中,晶体管tr可以包括掩埋栅电极。在一些示例实施例中,晶体管tr可以包括垂直栅电极。在一些示例实施例中,晶体管可以包括全环绕栅极(gaa)结构。

32.元件隔离膜is可以设置在衬底100中。晶体管tr可以设置在元件隔离膜is之间。元件隔离膜is可以限定晶体管tr的有源区。元件隔离膜is可以包括绝缘材料。

33.第一接触ct1和第一接触线cl1可以设置在绝缘结构ins的第一绝缘层110中。第一接触ct1可以连接到晶体管tr,并且第一导电线cl1可以连接到第一接触ct1。第一接触ct1和第一导电线cl1可以包括导电材料,诸如金属或掺杂的多晶硅中的至少一种。

34.可以提供覆盖绝缘结构ins的第二表面ins_2的第二绝缘层120。绝缘结构ins的第二表面ins_2可以是绝缘结构ins的与第一表面ins_1相对的表面。当从根据图1b的视角(例如,在截面中)观看时,绝缘结构ins的第二表面ins_2可以是绝缘结构ins的底表面。绝缘结构ins可以设置在第二绝缘层120上。在一些示例实施例中,第二绝缘层120可以为多个层。第二绝缘层120可以包括绝缘材料,诸如氧化硅或氮化硅中的至少一种。

35.导电结构cs可以设置在第二绝缘层120中。每个导电结构cs可以包括第二导电线cl2、第二接触ct2和第一焊盘pa1。第二导电线cl2和第二接触ct2可以在第三方向d3上交替地布置。第三方向d3可以与第一方向d1和第二方向d2相交。例如,第三方向d3可以与第一方向d1和第二方向d2垂直地相交。第二接触ct2可以连接到第二导电线cl2。第二导电线cl2和第二接触ct2可以包括导电材料。尽管附图仅在第二绝缘层120中/内示出了第二导电线cl2和第一焊盘pa1,但是示例实施例不限于此,并且可以在第二绝缘层120内存在更多个层。

36.第一焊盘pa1可以设置在第二绝缘层120的最下部分处。第一焊盘pa1的底表面可以与第二绝缘层120的底表面共面。第一焊盘pa1可以连接到第二接触ct2。第一焊盘pa1可以包括诸如金属的导电材料。

37.可以提供覆盖第二绝缘层120的底表面的第一保护膜pl1。第一保护膜pl1可以起到保护第二绝缘层120和第一焊盘pa1的作用。第一保护膜pl1可以包括绝缘材料,诸如氧化

硅或氮化硅中的至少一种。

38.可以提供凸块bp。凸块bp可以延伸穿过第一保护膜pl1。凸块bp可以连接到导电结构cs的第一焊盘pa1。凸块bp可以包括导电材料,例如金属(诸如焊料金属)。

39.可以提供覆盖衬底100的第二表面102的第三绝缘层130。衬底100的第二表面102可以是衬底100的与第一表面101相对的表面。当从根据图1b的视角观看时,衬底100的第二表面102可以是衬底100的顶表面。第三绝缘层130可以设置在衬底100上。第三绝缘层130可以包括诸如氧化硅或氮化硅中的至少一种的绝缘材料,并且可以与第一绝缘材料110和第二绝缘材料120中的任一者或两者的材料相同或不同。

40.可以提供覆盖第三绝缘层130的顶表面的第二保护膜pl2。第二保护膜pl2可以起到保护第三绝缘层130和衬底100的作用。第二保护膜pl2可以包括绝缘材料。在一些示例实施例中,与所示的情况不同,第二保护膜pl2可以在未提供第三绝缘层130的情况下设置在衬底100上(例如,直接设置在衬底上)。

41.第二焊盘pa2可以设置在第二保护膜pl2中。第二焊盘pa2可以暴露到第二保护膜pl2的外部。第二焊盘pa2的顶表面可以与第二保护膜pl2的顶表面共面。第二焊盘pa2可以包括导电材料。

42.可以提供延伸穿过衬底100和绝缘结构ins的通路绝缘层vi。通路绝缘层iv可以在第三方向d3上延伸,这样,可以延伸穿过衬底100和绝缘结构ins。通路绝缘层vi可以延伸穿过衬底100的第一表面101和绝缘结构ins的第一表面ins_1。通路绝缘层vi可以设置在通路区域vir中/内。通路绝缘层vi可以在第二方向d2上沿着通路区域vir延伸。晶体管区域tsr可以限定在通路绝缘层vi之间/外部。通路绝缘层vi可以包括绝缘材料。例如,通路绝缘层vi可以包括氧化物和/或氮化物。

43.通路绝缘层vi的第一表面vi_1可以接触第二绝缘层120。通路绝缘层vi的第一表面vi_1可以接触导电结构cs的第二导电线cl2。通路绝缘层vi的第一表面vi_1可以与绝缘结构ins的第二表面ins_2共面。当从根据图1b的视角/截面观看时,通路绝缘层vi的第一表面vi_1可以是通路绝缘层vi的底表面。通路绝缘层vi的第二表面vi_2可以接触第三绝缘层130。通路绝缘层vi的第二表面vi_2可以与衬底100的第二表面102共面。通路绝缘层vi的第二表面vi_2可以是通路绝缘层vi的与第一表面vi_1相对的表面。当从根据图1b的视角/截面观看时,通路绝缘层vi的第二表面vi_2可以是通路绝缘层vi的顶表面。通路绝缘层vi在第三方向d3上的长度可以等于衬底100在第三方向d3上的长度与绝缘结构ins在第三方向d3上的长度之和。通路绝缘层vi可以与任意或全部晶体管tr间隔开。

44.可以提供通路结构vs。通路结构vs可以在第三方向d3上延伸,这样,可以彻底地/完全地延伸穿过通路绝缘层vi、绝缘结构ins和衬底100。通路结构vs可以设置在通路区域vir中,并且在晶体管区域tsr中可以没有通路结构vs。多个通路结构vs可以延伸穿过一个通路绝缘层vi。多个通路结构vs可以被一个通路绝缘层vi围绕。一个通路绝缘层vi可以接触多个通路结构vs的外侧壁vs_os。

45.导电结构cs的第二导电线cl2可以连接到通路结构vs。通路结构vs的底表面vs_b可以接触导电结构cs的第二导电线cl2。通路结构vs的底表面vs_b可以与通路绝缘层vi的第一表面vi_1和绝缘结构ins的第二表面ins_2共面。通路结构vs可以连接到第二焊盘pa2。通路结构vs的顶表面vs_t可以接触第二焊盘pa2。通路结构vs的顶表面vs_t可以与第三绝

缘层130的顶表面共面。通路结构vs在第三方向d3上的长度(例如,通路结构vs的垂直长度)可以大于通路绝缘层vi在第三方向d3上的长度。通路结构vs在第三方向d3上的长度可以大于衬底100在第三方向d3上的长度与绝缘结构ins在第三方向d3上的长度之和。

46.通路绝缘层vi在第一方向d1上的宽度可以大于多个通路结构vs在第一方向d1上的宽度之和。例如,通路绝缘层vi在第一方向d1上的宽度可以大于两个通路结构vs在第一方向d1上的宽度之和。通路绝缘层vi在第二方向d2上的宽度可以大于多个通路结构vs在第二方向d2上的宽度之和。例如,通路绝缘层iv在第二方向d2上的宽度可以大于10个通路结构vs在第二方向d2上的宽度之和。

47.在一些示例实施例中,与所示的情况不同,通路结构vs在第三方向d3上的长度(例如,通路结构vs的高度)可以等于通路绝缘层vi在第三方向d3上的长度。在这种情况下,通路结构vs的顶表面vs_t、通路绝缘层vi的第二表面vi_2和衬底100的第二表面102可以是共面的。

48.通路结构vs中的每一者或者一者或更多者可以包括阻挡层ba和导电层co。导电层co和阻挡层ba均可以在第三方向d3上延伸,这样,可以延伸穿过衬底100、绝缘结构ins和通路绝缘层vi。阻挡层ba可以围绕导电层co。阻挡层ba可以接触导电层co的外侧壁。导电层co和阻挡层ba可以接触导电结构cs的第二导电线cl2。导电层co和阻挡层ba可以接触第二焊盘pa2。导电层co和阻挡层ba可以分别包括不同的导电材料。例如,导电层co可以包括铜,并且阻挡层ba可以包括氮化钛,然而,示例实施例不限于此。

49.随着通路结构vs远离第二保护膜pl2延伸,通路结构vs的宽度可以逐渐地增大。随着通路结构vs朝向第二绝缘层120、第二接触ct2、第二导电线cl2、第一焊盘pa1、第一保护膜pl1和凸块bp延伸,通路结构vs的宽度可以逐渐地增大。通路结构vs可以具有渐窄的轮廓。

50.参照图1c,相邻的晶体管tr之间的距离(诸如最小距离)可以被定义为第一距离l1。

51.与晶体管tr相邻的每个通路结构vs和与其相邻的晶体管tr之间的最小距离可以是恒定的。例如,当与晶体管tr相邻的第一通路结构vs1和与其相邻的第一晶体管tr1之间的最小距离被定义为第二距离l2并且与晶体管tr相邻的第二通路结构vs2和与其相邻的第二晶体管tr2之间的最小距离被定义为第三距离l3时,第二距离l2和第三距离l3可以是相等的。第二距离l2和第三距离l3可以大于第一距离l1。尽管图1c示出了通路结构vs布置在方形的角处,但是示例实施例不必限于此。尽管图1c示出了晶体管tr布置在方形的角处,但是示例实施例不必限于此。

52.相邻的通路结构vs之间的最小距离可以大于彼此相邻的通路结构vs和晶体管tr之间的最小距离。例如,当第一通路结构vs1和第二通路结构vs2之间的最小距离被定义为第四距离l4时,第四距离l4可以大于第二距离l2和第三距离l3。

53.在一些示例实施例中,除了晶体管tr之外的元件可以设置在通路区域vir的通路结构vs之间。例如,电容器和/或电阻器可以设置在通路区域vir的通路结构vs之间。

54.在根据本公开的示例实施例的半导体器件中,通路结构vs可以单独地设置在通路区域vir中而未设置任何晶体管tr。因此,可以无需或不需要/不期望将通路结构vs设置在晶体管区域tsr中,这样,晶体管tr可以相对密集地设置在晶体管区域tsr中。因此,可以减

小半导体器件的尺寸。因为半导体器件的尺寸减小,所以可以改善产率和/或制造成本。

55.图2a、图2b、图2c、图2d、图2e、图2f、图2g、图2h和图2i是说明用于制造/制作根据图1a、图1b和图1c的半导体器件的方法的截面图。

56.参照图2a,可以在衬底100中形成元件隔离膜is,并且可以在衬底100上形成晶体管tr、第一接触ct1、第一导电线cl1以及包括第一绝缘层110和掩模层ma的绝缘结构ins。晶体管tr可以形成在晶体管区域tsr中,并且可以不形成在通路区域vir中。晶体管tr可以形成在衬底100的第一表面101上。

57.可以形成延伸穿过绝缘结构ins和衬底100的一部分的沟槽tc。沟槽tc可以形成在通路区域vir中。沟槽tc的形成可以包括形成第一光刻胶图案pp1以及使用第一光刻胶图案pp1作为蚀刻掩模对绝缘结构ins和衬底100进行蚀刻(例如,湿蚀刻和/或干蚀刻)。沟槽tr可以由绝缘结构ins的表面和衬底100的表面限定。沟槽tc可以在第二方向d2上延伸。在形成沟槽tc之后,可以去除剩余的光刻胶图案pp1。

58.参照图2b,可以在沟槽tc中形成通路绝缘层vi。通路绝缘层vi的形成可以包括在绝缘结构ins的表面和衬底100的表面上沉积绝缘材料以及执行平坦化工艺。可以利用化学气相沉积(cvd)工艺和/或原子层沉积(ald)工艺来沉积绝缘材料;然而,示例实施例不限于此。平坦化工艺可以是或可以包括化学机械平坦化(cmp)工艺和/或回蚀工艺;然而,示例实施例不限于此。

59.参照图2c,可以在通路绝缘层vi中形成通孔vh。通孔vh的形成可以包括在绝缘结构ins和通路绝缘层vi上形成第二光刻胶图案pp2以及使用第二光刻胶图案pp2作为蚀刻掩模来蚀刻通路绝缘层iv。多个通孔vh可以形成在一个通路绝缘层vi处或一个通路绝缘层vi内。通孔vh可以由通路绝缘层vi的表面限定。在形成通孔vh之后,可以去除剩余的第二光刻胶图案pp2。

60.参照图2d,可以形成预备阻挡层pba和预备导电层pco。预备阻挡层pba可以形成在绝缘结构ins的表面和通路绝缘层vi的表面上,并且预备导电层pco可以形成在预备阻挡层pba上。预备阻挡层pba和预备导电层pco可以填充通孔vh。预备阻挡层pba和预备导电层pco可以分别包括相同和/或不同的导电材料。

61.参照图2e,可以形成通路结构vs。在一些示例实施例中,可以通过执行抛光工艺来去除预备阻挡层pba的上部和预备导电层pco的上部。其上部已经被去除的预备阻挡层pba可以被定义为阻挡层ba。其上部已经被去除的预备导电层pco可以被定义为导电层co。

62.参照图2f,可以在绝缘结构ins、通路绝缘层vi和通路结构vs上形成第二绝缘层120、第二导电线cl2、第二接触ct2、第一焊盘pa1、第一保护膜pl1和凸块bp。

63.参照图2g,可以颠倒(例如,翻转)衬底100。随后,可以利用诸如cmp工艺和/或蚀刻工艺之类的工艺去除衬底100的一部分和通路绝缘层vi的一部分,从而暴露通路结构vs。因为衬底100的一部分和通路绝缘层vi的一部分被去除,所以通路结构vs的阻挡层ba可以被暴露。

64.参照图2h,可以形成覆盖衬底100、通路绝缘层vi和通路结构vs的第三绝缘层130。例如,第三绝缘层130可以共形地沉积在衬底100、通路绝缘层vi和通路结构vs上。

65.参照图2i,可以去除第三绝缘层130的一部分和通路结构vs的一部分。在一些示例实施例中,可以通过抛光工艺去除第三绝缘层130的一部分和通路结构vs的一部分;然而,

示例实施例不限于此。

66.通路结构vs的顶表面vs_t可以被暴露。第三绝缘层130的顶表面和通路结构vs的顶表面vs_t可以变为共面。

67.在一些示例实施例中,可以在形成凸块bp并且随后颠倒衬底100之后执行用于去除衬底100的上部、通路绝缘层vi的上部和通路结构vs的上部的抛光工艺。例如,通路结构vs的一部分可以在如参照图2g描述的去除衬底100的一部分和通路绝缘层vi的一部分的工艺中与这些部分一起被去除。在这种情况下,衬底100的顶表面、通路结构vs的顶表面和通路绝缘层vi的顶表面可以变为共面。

68.返回参照图1b,可以形成覆盖第三绝缘层130的第二保护膜pl2,并且可以在第二保护膜pl2中形成第二焊盘pa2。

69.图3是根据本公开的一些示例实施例的半导体器件的俯视图。

70.参照图3,半导体器件可以包括其中设置有晶体管tra的晶体管区域tsra和其中设置有通路结构vsa的通路区域vira。在半导体器件的任何通路区域vira中可以没有晶体管tra,并且在半导体器件的晶体管区域tsra中可以没有通路结构vsa。

71.多个通路绝缘层via可以设置在每个通路区域vira中。设置在第一通路区域vir1a中的通路绝缘层via可以在第二方向d2上布置。设置在第一通路区域vir1a中的通路绝缘层via可以在第二方向d2上彼此间隔开。

72.设置在第二通路区域vir2a中的通路绝缘层via可以在第一方向d1上布置。设置在第二通路区域vir2a中的通路绝缘层via可以在第一方向d2上彼此间隔开。

73.图4a是根据本公开的一些示例实施例的半导体器件的俯视图。图4b是沿着图4a中的线a2-a2'截取的截面图。图4c是沿着图4a中的线c2-c2'截取的截面图。

74.参照图4a、图4b和图4c,半导体器件可以包括其中设置有晶体管trb的晶体管区域tsrb、其中设置有第一通路结构vs1b的通路区域virb以及其中设置有晶体管trb和第二通路结构vs2b的晶体管通路区域tvrb。晶体管区域tsrb可以设置在通路区域virb之间,并且晶体管通路区域tvrb可以设置在晶体管区域tsrb之间。在任何通路区域中没有晶体管,并且在任何晶体管区域中可以没有通路结构。

75.可以提供第一外绝缘层oi1b。第一外绝缘层oi1b可以设置在通路区域virb中。第一外绝缘层oi1b可以围绕第一通路结构vs1b。第一外绝缘层oi1b可以接触第一通路结构vs1b的外侧壁。多个第一外绝缘层oi1b可以被一个通路绝缘层vib围绕。多个第一外绝缘层oi1b的外侧壁可以接触一个通路绝缘层vib。多个第一外绝缘层oi1b可以延伸穿过一个通路绝缘层vib。第一外绝缘层oi1b可以包括绝缘材料。例如,第一外绝缘层oi1b可以包括氧化物。

76.可以提供第二外绝缘层oi2b。第二外绝缘层oi2b可以设置在晶体管通路区域tvrb中。第二外绝缘层oi2b可以围绕第二通路结构vs2b。第二外绝缘层oi2b可以接触第二通路结构vs2b的外侧壁。多个第二外绝缘层oi2b可以被衬底100b围绕。多个第二外绝缘层oi2b的外侧壁可以接触衬底100b。第二外绝缘层oi2b可以包括绝缘材料。例如,第二外绝缘层oi2b可以包括氧化物和/或氮化物。

77.与晶体管区域tsrb相邻的第一通路结构vs1b和相邻于其的晶体管trb之间的距离(诸如最小距离)、第二通路结构vs2b和晶体管区域tsrb中的相邻于其的晶体管trb之间的

最小距离以及第二通路结构vs2b和晶体管通路区域tvrb中的相邻于其的晶体管trb之间的最小距离可以是恒定的。

78.图5a、图5b、图5c、图5d、图5e和图5f是说明用于制造根据图4a、图4b和图4c的半导体器件的方法的截面图。

79.参照图5a和图5b,可以形成衬底100b和绝缘结构insb,并且可以在衬底100b和绝缘结构insb之间形成晶体管trb。随后,可以在通路区域virb中形成通路绝缘层vib。

80.可以在绝缘结构insb和通路绝缘层vib上形成光刻胶图案ppb。可以使用光刻胶图案ppb作为蚀刻掩模蚀刻通路绝缘层vib、绝缘结构insb和衬底100b,由此形成第一通孔vh1b和第二通孔vh2b。第一通孔vi1b可以形成在通路区域virb中。第二通孔vh2b可以形成在晶体管通路区域tvrb中。在形成第一通孔vh1b和第二通孔vh2b之后,可以去除剩余的光刻胶图案ppb。

81.参照图5c和图5d,可以形成预备外绝缘层poib。预备外绝缘层poib可以共形地覆盖通路区域virb、晶体管区域tsrb和晶体管通路区域tvrb。预备外绝缘层poib可以共形地覆盖通路绝缘层vib的表面、绝缘结构insb的表面和衬底100b的表面。预备外绝缘层poib的一些部分可以形成在第一通孔vh1b和第二通孔vh2b中。

82.参照图5e和图5f,可以形成第一通路结构vs1b和第二通路结构vs2b。第一通路结构vs1b和第二通路结构vs2b的形成可以包括沉积预备阻挡层和预备导电层以及执行去除预备阻挡层的上部和预备导电层的上部的抛光工艺。

83.根据去除预备阻挡层的上部和预备导电层的上部的抛光工艺,可以去除预备外绝缘层poib的上部。因为预备外绝缘层poib的上部被去除,所以预备外绝缘层poib可以分离为第一外绝缘层oi1b和第二外绝缘层oi2b。

84.参照图4a、图4b和图4c,可以通过与上面描述的工艺类似的工艺形成半导体器件的其余构成元件。

85.图6是根据本公开的一些示例实施例的半导体器件的俯视图。

86.参照图6,半导体器件可以包括其中设置有通路结构vsc和通路绝缘层vic的通路区域virc以及其中设置有晶体管trc的晶体管区域tsrc。

87.晶体管区域tsrc的一部分可以设置在通路区域virc之间。通路区域virc的四个侧之中的三个侧可以面对晶体管区域tsrc。

88.图7是根据本公开的一些示例实施例的半导体器件的俯视图。

89.参照图7,半导体器件可以包括其中设置有通路结构vsd和通路绝缘层vid的通路区域vird以及其中设置有晶体管trd的晶体管区域tsrd。晶体管区域tsrd可以围绕通路区域vird。

90.图8是根据本公开的一些示例实施例的半导体器件的俯视图。

91.参照图8,半导体器件可以包括其中设置有通路结构vse和通路绝缘层vie的通路区域vire以及其中设置有晶体管tre的晶体管区域tsre。通路区域vire可以分别设置在半导体器件的相对的侧端处。晶体管区域tsre可以设置在通路区域vire之间。晶体管区域tsre可以设置在半导体器件的中心部分处。

92.图9是根据本公开的一些示例实施例的半导体器件的截面图。

93.参照图9,随着通路结构vsf朝向凸块bpf、连接到凸块bpf的第一焊盘pa1f以及与

凸块bpf和第一焊盘pa1f接触的第一保护膜pl1f延伸,通路结构vsf的宽度可以逐渐减小。例如,通路结构vsf在第一方向d1上的宽度可以被定义为第一宽度w1,并且随着通路结构vsf朝向凸块bpf、第一焊盘pa1f和第一保护膜pl1f延伸,第一宽度w1可以逐渐减小。

94.随着通路结构vsf远离第二焊盘pa2f和围绕第二焊盘pa2f的第二保护膜pl2f延伸,通路结构vsf的宽度可以逐渐减小。通路结构vsf可以具有渐窄的轮廓。例如,随着通路结构vsf远离第二焊盘pa2f和第二保护膜pl2f延伸,第一宽度w1可以逐渐减小。

95.图10a、图10b和图10c是说明用于制造/制作根据图9的半导体器件的方法的截面图。

96.参照图10a,可以在衬底100f和绝缘结构insf中形成通路绝缘层vif。随后,可以在通路绝缘层vif和绝缘结构insf中形成绝缘层120f以及位于绝缘层120f中的导电线clf、接触ctf和第一焊盘pa1f。

97.可以在绝缘层120f上形成第一保护膜pl1f和凸块bpf。

98.参照图10b,可以颠倒衬底100f。之后,可以去除衬底100f的一部分和通路绝缘层vif的一部分,由此暴露通路绝缘层vif。

99.参照图10c,可以蚀刻暴露的通路绝缘层vif,由此形成通孔vhf。随着通孔vhf朝向凸块bpf、第一焊盘pa1f和第一保护膜pl1f延伸,通孔vhf的宽度可以逐渐减小。

100.参照图9,可以在通孔vhf中分别形成通路结构vsf,并且可以形成第二焊盘pa2f和第二保护膜pl2f。

101.图11是根据本公开的一些示例实施例的半导体器件的截面图。

102.参照图11,半导体器件可以包括中介件(interposer)300g、多个半导体芯片scg和模制层mdg。中介件300g可以包括外端子otg和焊盘pag。

103.多个半导体芯片scg可以在第三方向d3上堆叠在中介件300g上。例如,多个半导体芯片scg可以垂直地堆叠在中介件300g上。每个半导体芯片scg可以包括晶体管。多个半导体芯片scg中的至少一者可以包括通路绝缘层vig和延伸穿过通路绝缘层vig的通路结构vsg。

104.模制层mdg可以围绕多个半导体芯片scg。模制层mdg可以包括聚合物材料。例如,模制层mdg可以包括环氧树脂。

105.图12是根据本公开的一些示例实施例的半导体器件的截面图。

106.参照图12,半导体器件可以包括位于衬底100h和绝缘结构insh之间的外围晶体管ptrh和单元晶体管ctrh。外围晶体管ptrh和单元晶体管ctrh可以设置在晶体管区域tsrh中。半导体器件可以包括限定外围晶体管ptrh和单元晶体管ctrh的有源区的元件隔离膜ish、连接到外围晶体管ptrh的第一接触ct1h和第一导电线cl1h、连接到单元晶体管ctrh的第二接触ct2h和第三接触ct3h、连接到第二接触ct2h的位线blh以及连接到第三接触ct3h的信息存储元件dsh。例如,信息存储元件dsh可以是电容器和/或忆阻器。

107.可以提供延伸穿过衬底100h和绝缘结构insh的通路绝缘层vih,并且可以提供延伸穿过通路绝缘层vih的通路结构vsh。通路绝缘层vih和通路结构vsh可以设置在通路区域virh中。外围晶体管ptrh和单元晶体管ctrh可以不设置在通路区域virh中。

108.在根据本公开的示例实施例的半导体器件中,通路结构可以单独地设置在通路区域中而没有设置任何晶体管,这样,晶体管可以相对密集地设置在晶体管区域中。因此,半

导体器件可以具有相对小的尺寸,和/或可以具有改善的良率和/或降低的制造成本。

109.尽管已经参照附图描述了本发明构思的各种示例实施例,但是本领域普通技术人员应当理解,在不脱离本公开的范围并且不改变其基本特征的情况下,可以进行各种修改。此外,示例实施例不必被解释为相互排斥。例如,一些示例实施例可以包括参考一个或更多个附图描述的特征,并且还可以包括参考一个或更多个其他附图描述的其他特征。因此,上述实施例应仅在描述性意义上考虑,而不是出于限制的目的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1