1.本发明实施例涉及一种半导体装置技术,尤其涉及一种内连接结构及其制造方法。

背景技术:

2.随着半导体行业推出具有更高效能及更多功能的新一代集成电路(integrated circuit,ic),形成集成电路(ic)的元件密度增加,而部件或元件之间的尺寸、大小及间距却减少。半导体行业持续通过不断缩小最小特征尺寸来提高各种电子部件(例如,晶体管、二极管、电阻器、电容器等)的集积密度,使得更多的部件可以整合至一给定的区域。

3.为了于基底上制造不同的导电层,可以利用自对准接触(self-aligned contact,sac)工艺来避免误对准。然而,整合制造也带来了一些问题,例如可靠度、高电容或高电阻。因此,本技术领域需要提供改进的装置或方法,以解决上述的问题。

技术实现要素:

4.在一些实施例中,一种内连接结构包括一第一介电层;一第一导电特征部件,设置于第一介电层内;一第二介电层,位于第一介电层上,其中第二介电层与第一介电层直接接触;一导电层,设置于第二介电层内;一衬层,设置于导电层与第二介电层之间;一第三介电层,位于第二介电层上;一第二导电特征部件,设置于第三介电层内;以及一第一上盖层,设置于二导电特征部件与第三介电层之间。

5.在一些实施例中,一种内连接结构包括:一第一介电层;一第一导电特征部件,设置于第一介电层内;一第二介电层,位于第一介电层上;一导电层,设置于第二介电层内;一衬层,设置于导电层与第二介电层之间;一第一上盖层设置于第一导电特征部件与导电层之间,其中第一上盖层包括一二维材料;一第三介电层,位于第二介电层上;一第二导电特征部件,设置于第三介电层内;以及一第二上盖层,设置于第二导电特征部件与第三介电层之间。

6.在一些实施例中,一种内连接结构的制造方法包括:形成一第一导电特征部件及一第二导电特征部件于一第一介电层内;形成一第一上盖层于第一导电特征部件及第二导电特征部件的上表面上;形成一第二介电层于第一介电层及第一上盖层上;移除一部分的第二介电层,以形成一第一开口于第二介电层内而露出位于第一导电特征部件上方的第一上盖层;形成一第一导电层于第一开口内;以及形成一第三导电特征部件于第一导电特征部件上。

附图说明

7.图1示出根据一些实施例的半导体装置结构的各个制造阶段的立体示意图。

8.图2a至图2b示出根据一些实施例的半导体装置结构的各个制造阶段的剖面示意图。

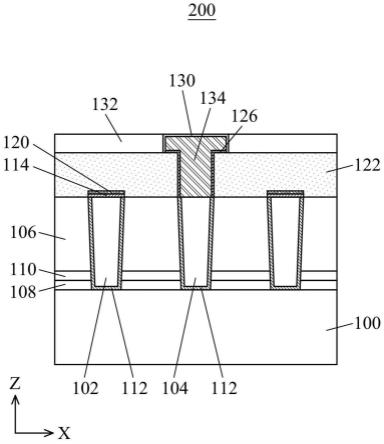

9.图3a至图3j示出根据一些实施例的半导体内连接结构的各个制造阶段的剖面示意图。

10.图4a至图4c示出根据一些实施例的另一半导体内连接结构的各个制造阶段的剖面示意图。

11.图5a至图5e示出根据一些实施例的又一半导体内连接结构的各个制造阶段的剖面示意图。

12.图6a至图6c示出根据一些实施例的又一半导体内连接结构的各个制造阶段的剖面示意图。

13.图7a至图7d示出根据一些实施例的又一半导体内连接结构的各个制造阶段的剖面示意图。

14.图8a至图8c示出根据一些实施例的又一半导体内连接结构的各个制造阶段的剖面示意图。

15.图9示出根据一些实施例的半导体内连接结构的制造方法流程图。

16.附图标记如下:

17.100:半导体装置结构

18.102,104,134,142:导电特征部件

19.106:第一介电层

20.108,110:蚀刻停止层(esl)

21.112:阻挡层

22.114:第一上盖层

23.116:牺牲层

24.118,124:开口

25.120:第二上盖层

26.122:第二介电层

27.126:衬层

28.128:第一导电层

29.130:第三上盖层

30.132:第三介电层

31.140:第二导电层

32.150:第四上盖层

33.200,300,400,500,600,700:内连接结构

34.601:基底

35.602:装置

36.603:隔离区域

37.604:源极/漏极(s/d)区域

38.606:栅极堆叠

39.608:通道区域

40.610:栅极电极层

41.614:栅极介电层

insulator,soi)基底,其包括设置于两硅层之间的一绝缘层(未示出)。在一型态中,绝缘层为一含氧材料,例如氧化物。

55.基底601可以包括已经适当地掺入杂质(例如,p型或n型杂质)的各种区域。举例来说,掺杂物,用于n型鳍式场效晶体管(fin field effect transistor,finfet)的磷及用于p型鳍式场效晶体管(finfet)的硼。

56.如上所述,装置602可以为任何合适的装置,诸如晶体管、二极管、图像感测器、电阻器、电容器、电感器、记忆单元或其组合。在一些实施例中,装置602为晶体管,诸如平面式场效晶体管(fet)、鳍式场效晶体管(finfet)、纳米结构晶体管或其他合适的晶体管。纳米结构晶体管可以包括纳米片晶体管、纳米线晶体管、栅极全绕式(gate-all-around,gaa)晶体管、多桥通道式(multi-bridge channel,mbc)晶体管或任何具有栅极电极局部或完全环绕通道的晶体管。形成于基底601与内连接结构(如图3a至图3j所示的内连接结构200)之间装置602的一示例可以为鳍式场效晶体管(finfet)或纳米结构,其示出于图2a及图2b。一示例性的装置602可以包括源极/漏极(s/d)区域604及设置于作为源极的源极/漏极(s/d)区域604与作为漏极的源极/漏极(s/d)区域604之间的栅极堆叠606。虽然基底601上只形成一栅极堆叠606,然而可以考虑形成二或多个栅极堆叠606于基底601上。通道区域608形成于作为源区的源极/漏极(s/d)区域604与作为漏极的源极/漏极(s/d)区域604之间。

57.源极/漏极(s/d)区域604可以包括半导体材料,诸如si或ge、iii-v化合物半导体、ii-vi化合物半导体或其他合适的半导体材料。示例性的源极/漏极(s/d)区域604可以包括但不限于ge、sige、gaas、algaas、gaasp、sip、inas、alas、inp、gan、ingaas、inalas、gasb、alp、gap或相似物。源极/漏极(s/d)区域604可包括p型掺杂物(例如,硼)、n型掺杂物(例如,磷或砷)及/或其他合适的掺杂物(包括其组合)。源极/漏极(s/d)区域604可以通过使用化学气相沉积(cvd)、原子层沉积(atomic layer deposition,ald)或分子束外延(molecular beam epitaxy,mbe)的外延生长方法形成。通道区域608可包括一或多种半导体材料,诸如si、ge、gesn、sige、gaas、insb、gap、gasb、inalas、ingaas、gasbp、gaassb、gan、gap或inp。在一些实施例中,通道区域608包括与基底601相同的半导体材料。在一些实施例中,装置602为鳍式场效晶体管(finfet),而通道区域608为多个鳍部,每个鳍部至少具有三个表面由栅极堆叠606所包围。在其他一些实施例中,装置602为纳米片晶体管,而通道区域608则被栅极堆叠606所包围。

58.各个栅极堆叠606包括设置于通道区域608上或局部/完全围绕通道区域608的栅极电极层610。栅极电极层610可以为含金属的材料,诸如钨、钴、铝、钌、铜、其多层或相似物,并可以通过原子层沉积(ald)、等离子体增强化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)、mbd、物理气相沉积(physical vapor deposition,pvd)或任何合适的沉积技术进行沉积。各个栅极堆叠606可以包括一界面介电层612、设置于界面介电层612上的一栅极介电层614以及设置于栅极介电层614上的一或多个顺应性层616。栅极电极层610可以设置于顺应性层616上。界面介电层612可包括介电材料,诸如含氧材料或含氮材料或其多层,并可通过任何合适的沉积方法形成,诸如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)或原子层沉积(ald)。栅极介电层614可以包括介电材料,例如含氧材料或含氮材料,其具有大于二氧化硅的k值的高k值介电材料或其多层。栅极介电层614可以通过任何合适的方法形成,诸如化学气相沉积(cvd)、等离子体增强化学气

相沉积(pecvd)或原子层沉积(ald)。顺应性层616可以包括一或多个阻挡层及/或上盖层,例如含氮材料,诸如氮化钽(tan)、氮化钛(tin)或相似材料。顺应性层616可以进一步包括一或多个功函数层,诸如碳化铝钛、氧化铝钛、氮化铝钛或相似物。用语“顺应性”在此可用于描述在不同区域具有实质上相同厚度的膜层。顺应性层616可以通过原子层沉积(ald)、等离子体增强化学气相沉积(pecvd)、mbd或任何合适的沉积技术进行沉积。

59.一或多个栅极间隔件618顺沿着栅极堆叠606的侧壁(例如,栅极介电层614的侧壁)形成。栅极间隔件618可包括碳氧化硅、氮化硅、氮氧化硅、氮化硅碳或相似物、其多层或其组合,并可通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的沉积技术进行沉积。

60.局部的栅极堆叠606及局部的栅极间隔件618可以形成于隔离区域603上。隔离区域603形成于基底601上。隔离区域603可包括绝缘材料,诸如含氧材料、含氮材料或其组合。绝缘材料可以通过高密度等离子体化学气相沉积(high-density plasma chemical vapor deposition,hdpcvd)、流动式化学气相沉积(flowable chemical vapor deposition,fcvd)或其他合适的沉积工艺形成。在一型态中,隔离区域603包括由流动式化学气相沉积(fcvd)工艺形成的氧化硅。

61.形成一接触蚀刻停止层(contact etch stop layer,cesl)624于一部分的源极/漏极(s/d)区域604上及隔离区域603上,并且形成一第一层间介电(interlayer dielectric,ild)层626于接触蚀刻停止层(cesl)624上。在形成开口第一层间介电(ild)层626内时,接触蚀刻停止层(cesl)624可以提供一种机制来停止蚀刻工艺。接触蚀刻停止层(cesl)624可以顺应性沉积于源极/漏极(s/d)区域604及隔离区域603的表面上。接触蚀刻停止层(cesl)624可包括含氧材料或含氮材料,诸如氮化硅、氮化硅碳、氮氧化硅、氮化碳、氧化硅、氧化硅碳、相似物或其组合,并可通过化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、物理气相沉积(pvd)、原子层沉积(ald)或任何合适的沉积技术进行沉积。第一层间介电(ild)层626可包括由四乙基正硅酸盐(tetraethylorthosilicate,teos)、未掺杂的硅酸盐玻璃或掺杂的氧化硅(诸如硼磷硅酸盐玻璃(borophosphosilicate glass,bpsg)、熔融石英玻璃(fused silica glass,fsg)、磷硅酸盐玻璃(phosphosilicate glass,psg)、掺硼硅玻璃(boron doped silicon glass,bsg)、有机硅酸盐玻璃(organosilicate glass,osg)、sioc及/或任何合适的低k值介电材料(例如,具有低于二氧化硅的介电常数的材料)),并且可以通过旋涂、化学气相沉积(cvd)、流动式化学气相沉积(fcvd)、等离子体增强化学气相沉积(pecvd)、物理气相沉积(pvd)或任何合适的沉积技术沉积。

62.如图2a及图2b所示,形成一硅化层620于各个源极/漏极(s/d)区域604的至少一部分上。硅化层620可以包括具有si、cosi、nisi、tisi、mosi及tasi中的一或多种材料。在一些实施例中,硅化层620包括金属或金属合金硅化物,并且上述金属包括贵金属、耐火金属、稀土金属、其合金或其组合。一导电接点622设置于各个硅化层620上。导电接点622可包括具有ru、mo、co、ni.w、ti、ta、cu、al、tin或tan中的一或多种材料,导电接点622可通过任何合适的方法形成,如电化学镀(electro-chemical plating,ecp)或物理气相沉积(pvd)。硅化层620及导电接点622可以通过先形成开口于第一层间介电(ild)层626及接触蚀刻停止层(cesl)624内,以露出源极/漏极(s/d)区域604的至少一部分,然后形成硅化层620于源极/

漏极(s/d)区域604的露出部分上,再在硅化层620上形成导电接点622。

63.图3a至图3j示出根据一些实施例的内连接结构200的各个制造阶段的剖面示意图。在一些实施例中,内连接结构200可以形成于半导体装置结构100上、上方及/或下方。举例来说,如图3a所示,内连接结构200可以形成于半导体装置结构上,例如半导体装置结构100。可以理解的是,内连接结构200并不限于直接形成于半导体装置结构100上。其他结构(例如,中段(middle end of the line,meol)结构)可以形成于内连接结构200与半导体装置结构100之间。因此,内连接结构200的层间介电层(例如,以下所要讨论的第一介电层106),可以为内连接结构中任何层位的层间介电层。图9示出根据一些实施例用于内连接结构200的示例性制造方法800的流程图。为了更佳说明本公开内容,图3a至图3j中的内连接结构200的剖面示意图及图9中的方法800将一同说明。可以理解的是,方法800中所示的操作步骤并未详尽,其他操作步骤也可以在任何附图的操作步骤之前、之后或其间进行。再者,一些操作步骤可以同时进行,或者以不同于图3a至图3j及图9中所示的顺序来进行。

64.如图3a及图9中的操作步骤802所示,形成一导电特征部件102及一导电特征部件104于一第一介电层106内。在一些实施例中,一或多个蚀刻停止层(etch stop layer,esl)108及110可以形成于第一介电层106下方。蚀刻停止层(esl)108及110可在形成导电特征部件102及导电特征部件104于第一介电层106内时使用,以控制第一介电层106的蚀刻深度。在一些实施例中,蚀刻停止层(esl)108可包括sinx、sic

x

ny、aln

x

、alo

x

、ao

x

ny或其他合适的材料。在一些实施例中,蚀刻停止层(esl)108可以在低于425摄氏温度下通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,蚀刻停止层(esl)110可包括sio

x

、sic

x

、sio

xcy

或其他合适的材料。在一些实施例中,蚀刻停止层(esl)110可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。

65.在一些实施例中,第一介电层106可以包括非晶质的sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或相关低k值材料或由这些材料制成。第一介电层106的k值可以在1.0至5.0之间。在一些实施例中,第一介电层106可以包括具有有序孔隙的sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或相关低k值材料或由这些材料制成。此处使用的用语“有序孔隙”是指在介电材料内形成的具有既定排列且由空气填充的空孔或气隙。具有有序孔隙的第一介电层106具有低介电常数及高机械强度的特点。在一些实施例中,第一介电层106可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,第一介电层106的制作可以进行额外的退火或紫外线(ultraviolet,uv)固化的工艺或否。在一些实施例中,导电特征部件102及导电特征部件104可以包括cu、ni、co、ru、ir、al、pt、pd、au、ag、os、w、mo及相关合金。在一些实施例中,导电特征部件102及导电特征部件104可以在425摄氏温度至150摄氏温度之间通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)、无电电镀(electroless deposition,eld)、电化学镀(ecp)或其他合适的工艺形成。

66.在一些实施例中,可以形成一阻挡层112于第一介电层106与导电特征部件102之间以及第一介电层106与导电特征部件104之间。在一些实施例中,在操作步骤802中,可以通过双镶嵌、单镶嵌、半镶嵌或其他适当的工艺形成导电特征部件102及导电特征部件104于第一介电层106内。以单镶嵌工艺为一示例,依序沉积蚀刻停止层(esl)108、蚀刻停止层

(esl)110及第一介电层106,并进行蚀刻,以形成依据预定义图案的开口。然后,沉积阻挡层112于开口内,并沉积导电材料(例如,铜)于阻挡层112上。在开口内的阻挡层112上沉积导电材料可以包括通过物理气相沉积(pvd)工艺形成一种子层于阻挡层112上,然后通过电沉积工艺形成导电材料于种子层上。之后,平坦化导电材料的上表面,使导电特征部件102及导电特征部件104、阻挡层112及第一介电层106的上表面实质上为共平面。

67.如图3b及图9中的操作步骤804所示,形成一第一上盖层114于导电特征部件102及导电特征部件104的上表面。在一些实施例中,第一上盖层114可以包括sin

x

或其他合适的材料。在一些实施例中,第一上盖层114可以在450摄氏温度至150摄氏温度通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。举例来说,第一上盖层114可以在低于200摄氏温度下通过热原子层沉积(thermal ald)工艺形成。

68.如图3c及图9中的操作步骤806及808所示,形成一牺牲层116于第一介电层106及第一上盖层114上,并且移除一部分的牺牲层116,以形成一开口118于牺牲层116内而露出位于导电特征部件102上的第一上盖层114。在一些实施例中,牺牲层116可以包括非晶质态的含碳层。在一实施例中,牺牲层116为非晶质碳。开口118可以通过干式蚀刻、湿式蚀刻或其他合适的工艺形成。

69.如图3d及图9中的操作步骤810所示,形成一第二上盖层120于开口118内的第一上盖层114(其位于导电特征部件102上方)。然后,如图3e及图9中的操作步骤810所示,移除牺牲层116。在一些实施例中,第二上盖层120可以包括hfo

x

、tio

x

或其他合适的材料。在一些实施例中,第二上盖层120可以在450摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。在一些实施例中,在形成第二上盖层120于第一上盖层114上之前,可以进行一预处理工艺,以帮助在第一上盖层114上选择性沉积第二上盖层120。预处理工艺可以通过将内连接结构200与由含氢前驱物(例如,氢气、氨气、碳氢化合物或相似物或其任何组合)形成的h2等离子体接触来进行。

70.举例来说,h2等离子体可以通过降低含碳层的表面不需要的羟基数量与通过表面氢化提供含碳层的强化学改质来改变牺牲层116的表面功能。含碳层的处理表面使第二上盖层120的成核延迟。举例来说,在第二上盖层120的沉积期间,hfo

x

或tio

x

更易于与第一上盖层114(例如,sin

x

)接合,而不是与非晶质态的含碳层的处理表面接合。因此,预处理工艺可以帮助在第一上盖层114上选择性沉积第二上盖层120。

71.如图3f及图9中的操作步骤812所示,形成一第二介电层122于第一介电层106、第一上盖层114(位于导电特征部件104上方)及第二上盖层120(位于导电特征部件102上方)上。在一些实施例中,第二介电层122可以包括sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或具有有序孔隙的相关的低k值材料。在一些实施例中,第二介电层122可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,第二介电层122的制作可以进行额外的退火或紫外线固化的工艺或否。在一些实施例中,第一介电层106及第二介电层122可以由相同的材料形成。

72.如第9中的操作步骤814所示,移除一部分的第二介电层122,以形成一开口124于第二介电层122内而露出位于导电特征部件104上方的第一上盖层114。在一些实施例中,也可以移除第一上盖层114,以露出导电特征部件104的上表面,如图3g所示。

73.可以形成一衬层126于开口124的侧壁上及第二介电层122上。在一些实施例中,衬

层126可以包括hfo

x

或其他合适的材料。在一些实施例中,衬层126可以在450摄氏温度至150摄氏温度通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。在形成衬层126之前,可对第二介电层122及导电特征部件104进行一预处理工艺,如以上所述的h2等离子体处理。通过进行h2等离子体处理,对于衬层126(例如,hfo

x

),第二介电层122(例如,sio

x

、sio

xcyhz

、sio

xcy

或sic

x

)的表面与导电特征部件104(例如,cu、ni、co、ru、ir、al、pt、pd、au、ag、os、w或mo)的表面具有不同的沉积选择性。因此,如图3g所示,衬层126形成于开口124的侧壁及第二介电层122上,但未形成于导电特征部件104上(或几乎未形成于导电特征部件104上)。

74.如图3h及图9中的操作步骤816所示,形成一第一导电层128于开口124内且位于衬层126上。由于第一导电层128、衬层126及导电特征部件104共同的金属特性,衬层126的形成使第一导电层128以自对准的方式形成于衬层126及导电特征部件104上。在一些实施例中,第一导电层128可以包括ru、mo、相关合金或其他合适的材料。在一些实施例中,第一导电层128可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。然后,如图3i及图9中的操作步骤818所示,移除部分的第一导电层128,以形成一导电特征部件134于导电特征部件104上。

75.在一些实施例中,导电特征部件134可由双镶嵌、单镶嵌、半镶嵌或其他合适的工艺形成。在一些实施例中,导电特征部件134可以由半镶嵌工艺形成。在一些实施例中,图案化第二介电层122,以形成开口124,然后第一介电层128(例如,ru)填入开口124内。第一导电层128过度填充于开口124内及第二介电层122上,此意味着第一导电层128持续沉积直至第二介电层122上形成由第一导电层128构成的膜层。然后,遮蔽及蚀刻第一导电层128,以形成导电特征部件134。举例来说,一掩模可以设置于导电特征部件104上方的第一导电层128上,并露出导电特征部件102上方的第一导电层128。然后,进行一蚀刻操作步骤,以去除未被掩模遮盖的第一导电层128及衬层126,而在导电特征部件104上形成导电特征部件134。导电特征部件134可以包括位于开口124内的介层连接结构及位于介层连接结构上的导电线。在一些实施例中,介层连接结构及导电线可以由同一材料形成,如图3i所示。

76.如图3j所示,形成一第三上盖层130于导电特征部件134上,且一第三介电层132形成于第二介电层122上。然后,可以进行一平坦化操作步骤,使第三上盖层130与第三介电层132共平面。在一些实施例中,第三上盖层130可以包括sio

xcyhz

、sio

xcy

、sic

x

、sin

x

、sic

x

ny或其他合适的材料。在一些实施例中,第三上盖层130可以在450摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。在一些实施例中,第三介电层132可以包括sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或具有或未具有有序孔隙的相关的低k值材料。第三介电层132的k值可以在1.0至5.0之间。在一些实施例中,第三介电层132可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,第三介电层132的制作可以进行额外的退火或紫外线固化工艺或否。在一些实施例中,第三介电层132及第二介电层122可以由同一材料形成。

77.通过用上述操作步骤形成导电特征部件134于导电特征部件104上,可以在不使用自组装单层(self-assembled monolayer,sam)的情况下形成一自对准内连接结构。自组装单层(sam)工艺通常用于自对准图案化工艺以供内连接结构制造工艺之用,而防止导电材

料聚积于金属内连接层区域之外。然而,使用自组装单层(sam)工艺来形成自对准的内连接结构,可能发生自组装单层(sam)残留物余留于金属线上及/或在自组装单层(sam)与后续沉积前驱物(例如,形成蚀刻停止层的前驱物)之间发生不必要的反应。通过未使用自组装单层(sam)工艺的情况下,以上述操作步骤形成导电特征部件134于导在电特征部件104上,可以避免使用自组装单层(sam)工艺来形成自对准内连接结构的问题。自对准内连接结构的可靠度可以得到改善,并且内连接结构的电阻力得以降低。

78.另外,通过在选择性沉积之前,进行基底改质(例如,h2等离子体预处理),可以得到自对准内连接结构。可以防止介层连接金属间隙内的空孔,并且可以降低介层连接窗的电阻。再者,第一介电层106及第二介电层122之间不需要蚀刻停止层(esl)。换句话说,第一介电层106与第二介电层122为直接接触的。由于蚀刻停止层(esl)具有高介电常数,没有蚀刻停止层(esl)的内连接结构可以降低电容。

79.再者,第一介电层106及第二介电层122可以包括具有有序孔隙的介电材料或由其制成,这些材料具有低介电常数及高机械强度的特性。因此,可以降低第一介电层106及第二介电层122的k值,也可以降低内连接结构的电容。在发生误对准的情况下,使用具有有序孔隙的介电材料是有利的。举例来说,在一些实施例中,当开口118与导电特征部件发生误对准时,由于第一介电层106的材料为具有有序孔隙的低k值材料(其具有较高的机械强度),移除牺牲层116并不会损坏或几乎不会损坏第一介电层106。

80.图4a至图4c示出根据一些实施例的另一内接结构300的各个制造阶段的剖面示意图。图4a中的内连接结构300(其相似于内连接结构200)始于图3a至图3g所示的导电特征部件134形成之前的阶段。然而,内连接结构200的导电特征部件134的结构及制造工艺与内连接结构300不同。

81.如图4a所示,形成第一导电层128于开口124内,且形成第二导电层140于第一导电层128及衬层126上方。在一些实施例中,形成第一导电层128于开口124内之后,可对第一导电层128进行一平坦化操作步骤,例如化学机械研磨(chemical mechanical polishing,cmp)。在一些实施例中,第一导电层128可以包括ru、mo、相关合金或其他合适的材料,而第二导电层140可以包括cu、ni、co、ru、ir、al、pt、pd、au、ag、os、w、mo、相关合金或其他合适的材料。在一些实施例中,第一导电层128可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成,而第二导电层140可以在425摄氏温度至150摄氏温度之间通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)、无电电镀(eld)、电化学镀(ecp)或其他合适的工艺形成。

82.如图4b所示,移除部分的第二导电层140,以形成一导电特征部件142于导电特征部件104上。举例来说,可以设置一掩模于导电特征部件104上方的第二导电层140上,并露出位于导电特征部件102上方的第二导电层140。然后,进行蚀刻操作步骤,以去除第二导电层140及未被掩模覆盖的衬层126,并在导电特征部件104上形成导电特征部件142。导电特征部件142包括由第一导电层128形成的介层连接结构及由第二导电层140形成的导电线。然后,如图4c所示,第三上盖层130形成于导电特征部件142上,而第三介电层132形成于第二介电层122上,与上述关于图3j的说明相似。

83.图5a至图5e示出根据一些实施例的另一内连接结构400的各个制造阶段的剖面示意图。内连接结构400(其相似于内连接结构200)始于图3a至图3b所示的第一上盖层114形

成之后的阶段。在形成第一上盖层114之后,内连接结构400不包括内连接结构200的第二上盖层120。在一些实施例中,当导电特征部件102由高扩散材料(例如,cu)形成时,可能需要第一上盖层114及第二上盖层120来防止扩散,如图3a至图3b所示。然而,在一些实施例中,当导电特征部件102由低扩散材料(例如,ru)形成时,在导电特征部件102上形成第一上盖层114足以防止扩散,如图5a至图5e中所示。

84.如图5a所示,在形成第一上盖层114之后,形成第二介电层122于第一介电层106及第一上盖层114上。内连接结构400中的第二介电层122的材料及制造工艺可以相似于上述内连接结构200中的第二介电层122的材料及制造工艺。

85.然后,如图5b所示,移除一部分的第二介电层122,以形成开口124于第二介电层122内,且形成衬层126于开口124的侧壁上及第二介电层122上。内连接结构400的衬层126的材料及制造工艺可以相似于上述内连接结构200的衬层126的材料及制造工艺。

86.如图5c所示,先形成导电层128于开口124内及衬层126上。然后,如图5d所示,移除部分的第一导电层128,以形成导电特征部件134于导电特征部件104上。内连接结构400的第一导电层128及导电特征部件134的材料及工艺相似于上述内连接结构200的第一导电层128及导电特征部件134的材料及工艺。

87.如图5e所示,形成第三上盖层130于导电特征部件134上,且形成第三介电层132于第二介电层122上。内接结构400的第三上盖层130及第三介电层132的材料及制造工艺可以相似于内连接结构200的第三上盖层130及第三介电层132的材料及制造工艺。

88.图6a至图6c示出根据一些实施例的另一内连接结构500的各个制造阶段的剖面示意图。内连接结构500(其相似于内连接结构400)始于图5a至图5b所示的导电特征部件134形成之前的阶段。然而,内连接结构400的导电特征部件134的结构及制造工艺不同于内连接结构500。

89.如图6a所示,形成第一导电层128于开口124内,且形成第二导电层140于第一导电层128及衬层126之上。在一些实施例中,第一导电层128可以包括ru、mo、相关合金或其他合适的材料,而第二导电层140可以包括cu、ni、co、ru、ir、al、pt、pd、au、ag、os、w、mo、相关合金或其他合适的材料。在一些实施例中,第一导电层128可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成,而第二导电层140可以在425摄氏温度至150摄氏温度之间通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相电化学镀(pvd)、无电电镀(eld)、电化学镀(ecp)或其他合适的工艺形成。

90.如图6b所示,移除部分的第二导电层140,以形成导电特征部件142于导电特征部件104上。导电特征部件142包括由第一导电层128形成的介层连接结构及由第二导电层140形成的导电线。然后,如图6c所示,形成第三上盖层130于导电特征部件142上,且形成第三介电层132于第二介电层122上,其方式相似于上述关于图4c的说明。

91.图7a至图7d示出根据一些实施例的另一内连接结构600的各个制造阶段的剖面示意图。内连接结构600(其相似于内连接结构200)始于图3a至图3b所示的第一上盖层114形成之后的阶段。在形成第一上盖层114之后,内连接结构600未包括内连接结构200的第二上盖层120。再者,形成一第四上盖层150于导电特征部件102及导电特征部件104的上表面上,而第四上盖层150的材料可以不同于第一上盖层114的材料。在内连接结构600中,第四上盖

层150形成于导电特征部件102及引导电特征部件104的上表面上。在一些实施例中,第四上盖层150可以包括二维(two-dimensional,2d)材料。本公开中使用的用语“二维材料”是指单层材料或单层型材料,其具有层间共价键及层间凡德瓦尔斯(van der waals)键的原子级薄的结晶固体。二维材料的示例可包括石墨烯、六方氮化硼(h-bn)或过渡金属二硫族化物(transition metal dichalcogenides,mx2),其中m为过渡金属元素,x为硫族元素。一些示例性的过渡金属二硫族化物(mx2)材料可以包括,但不限于hf、te2、ws2、mos2、wse2、mose2,或其任何组合。在一些实施例中,第四上盖层150可以包括石墨烯。在一些实施例中,第四上盖层150可以在450摄氏温度至150摄氏温度之间通过原子层沉积(ald)或其他合适的工艺形成。在一些实施例中,第四上盖层150可以防止金属从导电特征部件102扩散至第二介电层122。

92.在一些实施例中,第二介电层122可以包括sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或相关的具有有序孔隙的低k值材料。在一些实施例中,第二介电层122可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,第二介电层122的制作可以进行额外的退火或紫外线固化工艺或否。在一些实施例中,第一介电层106及第二介电层122可以由同一材料形成。

93.如图7a所示,移除一部分的第二介电层122,以形成开口124于第二介电层122内,以露出位于导电特征部件104上方的第四上盖层150。形成衬层126于开口124的侧壁上及第二介电层122上。由于第四上盖层150由二维材料形成,且二维材料(例如,石墨烯)具有较低的接触电阻,因此在形成开口124时,不需要去位于除导电特征部件104上方的第四上盖层150。在一些实施例中,可以通过干式蚀刻、湿式蚀刻或其他合适的工艺形成开口124。在一些实施例中,衬层126可以包括hfo

x

或其他合适的材料。在一些实施例中,衬层126可以在450摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。

94.在形成衬层126之前,可对第二介电层122及第四上盖层150进行一预处理工艺(例如,以上所述的h2等离子体处理)。预处理工艺可通过将内连接结构600与由含氢前驱物(例如,氢气、氨气、碳氢化合物或相似物或其任何组合)形成的h2等离子体接触来进行。举例来说,h2等离子体可以通过减少石墨烯表面不需要的羟基的数量来改变第四上盖层150的表面功能,并通过表面氢化提供石墨烯的强化学改质。处理后的石墨烯表面疏水性导致了衬层126成核的延迟。举例来说,在衬层126的沉积期间,hfo

x

会比处理后的石墨烯表面更容易与第二介电层122接合。因此,预处理工艺有助于选择性沉积衬层126于第二介电层122上。通过进行h2等离子体处理,第二介电层122(例如,sio

x

、sio

xcyhz

、sio

xcy

或sic

x

)及第四上盖层150(例如,二维材料)的表面,可能具有不同的衬层126(例如,hfo

x

)的沉积选择性。因此,如图7a所示,衬层126形成于开口124的侧壁上及第二介电层122上,但未形成于第四上盖层150上。

95.如图7b所示,第一导电层128形成于开口124内及第四上盖层150与衬层126上。在一些实施例中,第一导电层128可以包括ru、mo、相关合金或其他合适的材料。在一些实施例中,第一导电层128可以在425摄氏温度及150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。然后,如图7c所示,移除部分的第一导电层128,以形成导电特征部件134于第四上盖层150及导电特征部件104上。

96.在一些实施例中,导电特征部件134可由双镶嵌、单镶嵌、半镶嵌或其他适当的工艺形成。在一些实施例中,导电特征部件134可以由半镶嵌工艺形成。在一些实施例中,图案化第二介电层122,以形成开口124,然后以第一介电层128(例如,ru)填充开口124。第一导电层128过度填充于开口124内及第二介电层122上,此意味着第一导电层128持续沉积直至第二介电层122上形成由第一导电层128构成的膜层。遮蔽及蚀刻第一导电层128,以形成导电特征部件134。导电特征部件134可以包括位于开口124内的介层连接结构及位于介层连接结构上的导电线。在一些实施例中,介层连接结构及导电线可以由同一材料形成,如图7c所示。

97.如图7d所示,形成第三上盖层130于导电特征部件134上,且形成第三介电层132于第二介电层122上。在一些实施例中,第三上盖层130可以包括sio

xcyhz

、sio

xcy

、sic

x

、sin

x

、sic

x

ny或其他合适的材料。在一些实施例中,第三上盖层130可以在450摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成。在一些实施例中,第三介电层132可以包括sio

x

、sio

xcyhz

、sio

xcy

、sic

x

或相关的具有或未具有序孔隙的低k值材料。第三介电层132的k值可以在1.0至5.0之间。在一些实施例中,第三介电层132可以在425摄氏温度至150摄氏温度之间通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)、旋涂或其他合适的工艺形成。在一些实施例中,第三介电层132的制作可以进行额外的退火或紫外线固化工艺或否。在一些实施例中,第三介电层132及第二介电层122可以由同一材料形成。

98.图8a至图8c示出根据一些实施例的另一内连接结构700的各个制造阶段的剖面示意图。内连接结构700相似于图7a至图7b所示的导电特征部件134形成之前的内连接结构600。然而,内连接结构600的导电特征部件134的结构及制造工艺不同于内连接结构700。

99.如图8a所示,形成第一导电层128于第四上盖层150上方的开口124内,且形成第二导电层140于第一导电层128及衬层126上方。在一些实施例中,第一导电层128可以包括ru、mo、相关合金或其他合适的材料,而第二导电层140可以包括cu、ni、co、ru、ir、al、pt、pd、au、ag、os、w、mo、相关合金或其他合适的材料。在一些实施例中,第一导电层128可以在低于425摄氏温度下通过化学气相沉积(cvd)、物理气相沉积(pvd)、原子层沉积(ald)或其他合适的工艺形成,而第二导电层140可以在425摄氏温度至150摄氏温度之间通过原子层沉积(ald)、化学气相沉积(cvd)、物理气相沉积(pvd)、无电电镀(eld)、电化学镀(ecp)或其他合适的工艺形成。

100.如图8b所示,移除部分的第二导电层140,以形成导电特征部件142于导电特征部件104上。导电特征部件142包括由第一导电层128构成的介层连接结构及由第二导电层140构成的导电线。然后,如图8c所示,形成第三上盖层130于导电特征部件142上,且形成第三介电层132于第二介电层122上。

101.通过用上述操作步骤形成导电特征部件134于导电特征部件104上,可以不使用自组装单层(sam)工艺而形成自对准内连接结构。通过在不使用自组装单层(sam)工艺的情况下,以上述操作步骤形成导电特征部件134于导电特征部件104上,可以避免使用sam工艺来形成自对准的内连接结构所发生的问题(例如,自组装单层(sam)残留物余留于金属线上及/或在自组装单层(sam)与后续沉积前驱物之间不必要的反应),自对准的内连接结构的可靠度可以得到改善,并且可以降低内连接结构的电阻。

102.另外,可以通过在选择性沉积之前进行基底改质(例如,h2等离子体处理),实现自对准内连接结构。等离子体处理可以提高选择性沉积的选择比,以进行自对准图案化操作步骤。再者,第一介电层106及第二介电层122之间不需要蚀刻停止层(esl)。换句话说,第一介电层106直接接触第二介电层122。由于蚀刻停止层(esl)具有高介电常数,无蚀刻停止层(esl)的内连接结构可以降低电容。

103.再者,第一介电层106及第二介电层122可以包括具有有序孔隙的介电材料或由其制成,上述材料具有低介电常数及高机械强度的特性。因此,可降低第一介电层106及第二介电层122的k值,而内连接结构也可以降低电容。

104.内连接结构600或700通过使用二维(2d)材料形成上盖层于导电特征部件之间而具有进一步的优点。二维(2d)材料,即第四上盖层150,具有很大的阻挡特性,以防止金属从导电特征部件102扩散到第二介电层122。由于二维(2d)材料也具有低电阻的特性,所以不需要移除位于导电特征部件104与第一导电层128之间的第四上盖层150。如此一来,可以进一步简化内连接结构的制作工艺。

105.一实施例为一种内连接结构。内连接结构包括:一第一介电层、一第一导电特征部件、一第二介电层、一导电层、一衬层、一第三介电层、一第二导电特征部件以及一第一上盖层。第一导电特征部件设置于第一介电层内。第二介电层形成于第一介电层上,且第二介电层与第一介电层直接接触。导电层设置于第二介电层内。衬层设置于导电层与第二介电层之间。第三介电层形成于第二介电层上。第二导电特征部件设置于第三介电层内。第一上盖层设置于二导电特征部件与第三介电层之间。

106.在一些实施例中,衬层更设置于第二导电特征部件与第二介电层之间。在一些实施例中,第一导电特征部件与导电层直接接触。在一些实施例中,导电层及第二导电特征部件包括同一材料。在一些实施例中,第二介电层包括具有有序孔隙的一介电材料。在一些实施例中,内连接结构还包括一第二上盖层,设置于第一导电特征部件与导电层之间。

107.另一实施例为一种内连接结构。内连接结构包括:一第一介电层、一第一导电特征部件、一第二介电层、一导电层、一衬层、一第一上盖层、一第三介电层、一第二导电特征部件以及一第二上盖层。第一导电特征部件设置于第一介电层内。第二介电层形成于第一介电层上。导电层设置于第二介电层内。衬层设置于导电层与第二介电层之间。第一上盖层设置于第一导电特征部件与导电层之间,且第一上盖层包括一二维材料。第三介电层形成于第二介电层上。第二导电特征部件设置于第三介电层内。第二上盖层设置于第二导电特征部件与第三介电层之间。

108.在一些实施例中,第一上盖层包括石墨烯。在一些实施例中,更设置于第二导电特征部件与第二介电层之间。在一些实施例中,导电层与第二导电特征部件包括同一材料。在一些实施例中,第二介电层包括具有有序孔隙的一介电材料。在一些实施例中,第二介电层与第一介电层直接接触。

109.又一实施例为一种内连接结构的制造方法。形成一第一导电特征部件及一第二导电特征部件于一第一介电层内。形成一第一上盖层于第一导电特征部件及第二导电特征部件的上表面上。形成一第二介电层于第一介电层及第一上盖层上。移除一部分的第二介电层,以形成一第一开口于第二介电层内而露出位于第一导电特征部件上方的第一上盖层。形成一第一导电层于第一开口内。形成一第三导电特征部件于第一导电特征部件上。

110.在一些实施例中,内连接结构的制造方法还包括:形成一第二上盖层于第二导电特征部件上方的第一上盖层上。再者,形成第二上盖层于第二导电特征部件上方的第一上盖层上包括:形成一牺牲层于第一介电层及第一上盖层上;移除一部分的牺牲层,以形成一第二开口于牺牲层内而露出位于第二导电特征部件上方的第一上盖层;形成第二上盖层于第二导电特征部件上方的第一上盖层上;以及移除牺牲层。在一些实施例中,内连接结构的制造方法还包括:移除位于第一开口内的第一上盖层。在一些实施例中,形成第一导电层于第一开口内还包括:形成一衬层于第一开口的侧壁上及第二介电层上;形成第一导电层于衬层上;以及进行一平坦化操作,以移除一部分的第一导电层。在一些实施例中,形成一第三导电特征部件于第一导电特征部件上包括:形成一第二导电层于衬层及第一导电层上;图案化第二导电层,以形成第三导电特征部件于第二介电层上;以及形成一第三介电层于第二介电层及第三导电特征部件上。在一些实施例中,内连接结构的制造方法还包括:形成一第三上盖层于第三特征导电特征部件上。再者,第一三特征导电特征部件及第二特征导电特征部件包括同一材料。

111.又一实施例为一种内连接结构的制造方法。形成一第一导电特征部件及一第二导电特征部件于第一介电层内。形成一第一上盖层于第一导电特征部件及第二导电特征部件的上表面上。形成一牺牲层于第一介电层及第一上盖层上。形成一第一开口于牺牲层内,以露出位于第二导电特征部件上方的第一上盖层。对牺牲层进行一预处理操作。形成一第二上盖层于第二导电特征部件上方所露出的第一上盖层上。移除牺牲层。形成一第二介电层于第一介电层、第一上盖层及第二上盖层上。移除一部分的第二介电层,以形成一第二开口于第二介电层内而露出位于第一导电特征部件方的第一上盖层。形成一第一导电层于第二开口内。形成一第三导电特征部件于第一导电特征部件上。

112.以上概略说明了本发明数个实施例的特征部件,使所属技术领域中技术人员对于本公开的型态可更为容易理解。任何所属技术领域中技术人员应了解到可轻易利用本公开作为其它工艺或结构的变更或设计基础,以进行相同于此处所述实施例的目的及/或获得相同的优点。任何所属技术领域中技术人员也可理解与上述等同的结构并未脱离本公开的精神及保护范围,且可于不脱离本公开的精神及范围,当可作更动、替代与润饰。

- 该技术已申请专利。仅供学习研究,如用于商业用途,请联系技术所有人。

- 技术研发人员:郑凯方 张孝慷

- 技术所有人:台湾积体电路制造股份有限公司

- 我是此专利的发明人

- 该领域下的技术专家

- 如您需求助技术专家,请点此查看客服电话进行咨询。

- 1、贺老师:氮化物陶瓷、光功能晶体材料及燃烧合成制备科学及工程应用

- 2、杨老师:工程电磁场与磁技术,无线电能传输技术

- 3、许老师:1.气动光学成像用于精确制导 2.人工智能方法用于数据处理、预测 3.故障诊断和健康管理

- 4、王老师:智能控制理论及应用;机器人控制技术

- 5、李老师:1.自旋电子学 2.铁磁共振、电磁场理论

- 如您是高校老师,可以点此联系我们加入专家库。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1

精彩留言,会给你点赞!

专利分类正在加载中....