一种碳化硅MOSFET器件及其制造方法与流程

一种碳化硅mosfet器件及其制造方法

技术领域

1.本发明涉及半导体制造领域,具体涉及一种碳化硅mosfet器件及其制造方法。

背景技术:

2.由于传统的平面型碳化硅金属氧化物半导体场效应晶体管(planar sic mosfet)存在jfet电阻,导致其损耗较大,另外,平面型碳化硅mosfet尺寸较大,影响了器件的特征导通电阻,降低了其集成度和电流导通密度。

3.因此,碳化硅沟槽结构mosfet有效得消除了jfet区的电阻,纵向的导电沟道提高了器件的集成度和电流导通密度。

技术实现要素:

4.本发明提供一种碳化硅mosfet器件及其制造方法,能够解决背景技术中的技术的问题,通过碳化硅沟槽结构mosfet有效的消除jfet电阻,纵向的导电沟道提高了器件的集成度和电流导通密度。

5.为解决上述技术问题,本发明提供一种碳化硅mosfet器件的制造方法,包括以下步骤:

6.在第一导电类型n型衬底上的第一导电类型n型外延层上通过离子注入或外延形成第二导电类型p型体区;

7.在第二导电类型p型体区上通过离子注入形成第二导电类型p型重掺杂区;

8.在第二导电类型p型重掺杂区通过离子注入形成第一导电类型n型重掺杂区;

9.通过掩膜在所述第一导电类型n型重掺杂区上的中间区域刻蚀出第一沟槽结构;

10.在第二导电类型p型体区深入到第一导电类型n型外延层内刻蚀出第二沟槽结构,所述第二沟槽结构的宽度小于所述第一沟槽结构的宽度;

11.在所述第二沟槽结构内对所述第一导电类型n型外延层进行离子注入,形成第二导电类型p型屏蔽区;

12.在所述第一沟槽结构和所述第二沟槽结构内表面形成二氧化硅氧化层;

13.在形成所述二氧化硅氧化层后,淀积多晶硅,形成多晶硅栅。

14.较佳的,在第一导电类型n型衬底上的第一导电类型n型外延层上通过离子注入或外延形成第二导电类型p型体区之前还包括以下步骤:

15.在第一导电类型n型衬底上生长第一导电类型n型外延层;

16.对第一导电类型n型衬底和第一导电类型n型外延层掺杂元素,所述第一导电类型n型衬底的掺杂浓度高于所述第一导电类型n型外延层的掺杂浓度。

17.较佳的,所述第一导电类型n型衬底上生长所述第一导电类型n型外延层102,对第一导电类型n型衬底和第一导电类型n型外延层掺杂元素,第一导电类型n型衬底的掺杂浓度高于第一导电类型n型外延层的掺杂浓度,第一导电类型n型外延层的厚度和掺杂浓度根据器件耐压的额定值确定。

18.所述第一导电类型掺杂元素可以为氮、磷,使得第一导电类型n型外延层掺杂类型为n型;也可以为硼、铝使得第一导电类型n型外延层掺杂类型为p型。第一导电类型和第二导电类型相反,当第一导电类型为n型时,第二导电类型为p型;当第一导电类型为p型时,第二导电类型为n型。

19.较佳的,在所述第一沟槽结构和所述第二沟槽结构内表面形成二氧化硅氧化层之后还包括以下步骤:

20.在多晶硅栅上生长二氧化硅;

21.对器件进行欧姆接触工艺或金属化工艺;

22.对器件表面进行钝化处理。

23.本发明还提供一种碳化硅mosfet器件,包括:

24.第一导电类型n型衬底,在所述第一导电类型n型衬底生长第一导电类型n型外延层,在所述第一导电类型n型外延层通过离子注入或外延形成第二导电类型p型体区;

25.所述第二导电类型p型体区通过离子注入形成第二导电类型p型重掺杂区;

26.所述第二导电类型p型重掺杂区通过离子注入形成第一导电类型n型重掺杂区,所述第一导电类型n型重掺杂区的长度小于所述第二导电类型p型重掺杂区的长度;

27.所述第一导电类型n型重掺杂区上的中间区域刻蚀出第一沟槽结构;

28.所述第二导电类型p型体区深入到第一导电类型n型外延层内刻蚀出第二沟槽结构,所述第二沟槽结构的宽度小于所述第一沟槽结构的宽度;

29.所述第一沟槽结构和所述第二沟槽结构内表面形成二氧化硅氧化层;

30.所述二氧化硅氧化层上淀积多晶硅,形成多晶硅栅。

31.较佳的,所述多晶硅栅上生长二氧化硅氧化物。

32.较佳的,所述mosfet器件的最上方为漏极。

33.本发明的有益效果是:

34.1.通过第一沟槽结构和第二沟槽结构形成了mosfet的t型沟槽结构,缩小了mosfet器件的尺寸,有效的消除jfet电阻,降低碳化硅mosfet器件的损耗。

35.2.通过第二导电类型p型体区上通过离子注入分别形成第二导电类型p型重掺杂区,以利于形成较低的体区欧姆接触电阻。

36.3.纵向的导电沟道提高了器件的集成度和电流导通密度。

37.4.在相等的驱动电压下,t型二氧化硅氧化层提高沟道区的载流子迁移率和导通速度。

附图说明

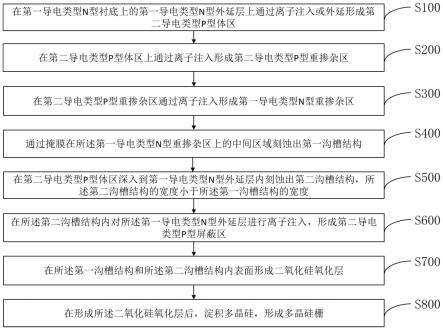

38.图1为本发明一种碳化硅mosfet器件的制造方法流程图;

39.图2为步骤s10中碳化硅mosfet器件的结构图;

40.图3为步骤s100中碳化硅mosfet器件的结构图;

41.图4为步骤s200中碳化硅mosfet器件的结构图;

42.图5为步骤s300中碳化硅mosfet器件的结构图;

43.图6为步骤s400中碳化硅mosfet器件的结构图;

44.图7为步骤s500中碳化硅mosfet器件的结构图;

45.图8为步骤s600中碳化硅mosfet器件的结构图;

46.图9为步骤s700中碳化硅mosfet器件的结构图;

47.图10为步骤s800中碳化硅mosfet器件的结构图;

48.图11为本发明一种碳化硅mosfet器件的结构图。

具体实施方式

49.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

50.实施例1

51.本实施例提供一种碳化硅mosfet器件的制造方法,如图1所示,包括以下步骤:

52.s100、在第一导电类型n型衬底101上的第一导电类型n型外延层102上通过离子注入或外延形成第二导电类型p型体区103;

53.s200、在第二导电类型p型体区103上通过离子注入形成第二导电类型p型重掺杂区104;

54.s300、在第二导电类型p型重掺杂区104通过离子注入形成第一导电类型n型重掺杂区105;

55.s400、通过掩膜在所述第一导电类型n型重掺杂区105上的中间区域刻蚀出第一沟槽结构106;

56.s500、在第二导电类型p型体区103深入到第一导电类型n型外延层102内刻蚀出第二沟槽结构107,所述第二沟槽结构107的宽度小于所述第一沟槽结构106的宽度;

57.s600、在所述第二沟槽结构内对所述第一导电类型n型外延层102进行离子注入,形成第二导电类型p型屏蔽区108;

58.s700、在所述第一沟槽结构106和所述第二沟槽结构107内表面形成二氧化硅氧化层109;

59.s800、在形成所述二氧化硅氧化层109后,淀积多晶硅,形成多晶硅栅110。

60.如图3所示,在外延层102上通过离子注入工艺或者外延工艺形成第二导电类型的体区103,这里第二导电类型为p型。离子注入工艺完成后,需要做相应的退火处理,以下不再赘述。

61.如图4所示,在第二导电类型p型体区103上通过离子注入分别形成第二导电类型p型重掺杂区104,以利于形成较低的体区欧姆接触电阻。

62.如图5所示,在第二导电类型p型重掺杂区104通过离子注入形成第二导电类型p型重掺杂区105,以利于形成较低的源区欧姆接触电阻。

63.如图6所示,通过掩膜在第二导电类型p型重掺杂区105上中心位置处刻蚀出图5所示的第一沟槽结构106。

64.如图7所示,在第二导电类型p型体区103内刻蚀出第二沟槽结构107。第二沟槽结构107的宽度要小于第一沟槽结构106的宽度。第一沟槽结构106和第二沟槽结构107形成了mosfet的t型沟槽结构。

65.如图8所示,在沟槽内对外延层102进行离子注入,形成第二导电类型p型屏蔽区108。注意p型屏蔽区108形状包括并不局限与方形,也可以为圆弧形等形状。

66.如图9所示,在第一沟槽结构106和第二沟槽结构107内表面形成二氧化硅氧化层109。

67.如图10所示,在形成二氧化硅氧化层109后,淀积多晶硅,形成多晶硅栅110。注意,沟槽这里的填充物多晶硅仅仅是示例性的,还可以为其他适合的材料,如钨等金属或者其他导电性良好的金属硅化物等。

68.作为一种优选的实施方式,在第一导电类型n型衬底101上的第一导电类型n型外延层102上通过离子注入或外延形成第二导电类型p型体区103之前还包括以下步骤:

69.s10、在第一导电类型n型衬底101上生长第一导电类型n型外延层102;

70.s20、对第一导电类型n型衬底101和第一导电类型n型外延层102掺杂元素,所述第一导电类型n型衬底101的掺杂浓度高于所述第一导电类型n型外延层102的掺杂浓度。

71.本实施例中,如图2所示,在第一导电类型n型衬底101上生长第一导电类型n型外延层102,对第一导电类型n型衬底101和第一导电类型n型外延层102掺杂元素,第一导电类型n型衬底101的掺杂浓度高于第一导电类型n型外延层102的掺杂浓度,第一导电类型n型外延层102的厚度和掺杂浓度根据器件耐压的额定值确定。

72.第一导电类型掺杂元素可以为氮、磷等,使得第一导电类型n型外延层102掺杂类型为n型;也可以为硼、铝等使得第一导电类型n型外延层102掺杂类型为p型。第一导电类型和第二导电类型相反,当第一导电类型为n型时,第二导电类型为p型;当第一导电类型为p型时,第二导电类型为n型。

73.作为一种优选的实施方式,在所述第一沟槽结构106和所述第二沟槽结构107内表面形成二氧化硅氧化层109之后还包括以下步骤:

74.s1000、在多晶硅栅110上生长二氧化硅;

75.s2000、对器件进行欧姆接触工艺或金属化工艺;

76.s3000、对器件表面进行钝化处理。

77.本实施例中,如图11所示,在多晶硅栅110上生长二氧化硅,再对mosfet器件进行欧姆接触工艺或金属化工艺,形成mosfet的源极和栅极,mosfet器件结构的最上方为漏极111,最后对mosfet器件表面进行钝化,防止mosfet器件表面的沾污,提高mosfet器件的电学特性的稳定性和可靠性。

78.实施例2

79.本实施例提供一种碳化硅mosfet器件,如图11所示,包括:

80.第一导电类型n型衬底101,在所述第一导电类型n型衬底101生长第一导电类型n型外延层102,在所述第一导电类型n型外延层102通过离子注入或外延形成第二导电类型p型体区103;

81.所述第二导电类型p型体区103通过离子注入形成第二导电类型p型重掺杂区104;

82.所述第二导电类型p型重掺杂区104通过离子注入形成第一导电类型n型重掺杂区105,所述第一导电类型n型重掺杂区105的长度小于所述第二导电类型p型重掺杂区104的长度;

83.所述第一导电类型n型重掺杂区105上的中间区域刻蚀出第一沟槽结构106;

84.所述第二导电类型p型体区103深入到第一导电类型n型外延层102内刻蚀出第二沟槽结构107,所述第二沟槽结构107的宽度小于所述第一沟槽结构106的宽度;

85.所述第一沟槽结构106和所述第二沟槽结构107内表面形成二氧化硅氧化层109;

86.所述二氧化硅氧化层109上淀积多晶硅,形成多晶硅栅110。

87.本实施例中,在第一导电类型n型衬底101上生长第一导电类型n型外延层102,对第一导电类型n型衬底101和第一导电类型n型外延层102掺杂元素,第一导电类型n型衬底101的掺杂浓度高于第一导电类型n型外延层102的掺杂浓度,第一导电类型n型外延层102的厚度和掺杂浓度根据器件耐压的额定值确定。

88.第一导电类型掺杂元素可以为氮、磷等,使得第一导电类型n型外延层102掺杂类型为n型;也可以为硼、铝等使得第一导电类型n型外延层102掺杂类型为p型。第一导电类型和第二导电类型相反,当第一导电类型为n型时,第二导电类型为p型;当第一导电类型为p型时,第二导电类型为n型。

89.作为一种优选的实施方式,所述多晶硅栅110上生长二氧化硅氧化物。

90.作为一种优选的实施方式,所述mosfet器件的最上方为漏极111。

91.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1