一种超结MOSFET及其制作方法与流程

本发明属于半导体,涉及一种超结mosfet及其制作方法。

背景技术:

1、一般功率mosfet中比导通电阻与击穿电压呈现2.5次方的关系,因此对于功率mosfet而言,高的击穿电压往往伴随着呈指数增长的比导通电阻,比如当击穿电压从50v增加到500v时,普通功率mosfet的比导通电阻将增加316倍。超结mosfet的出现让比导通电阻与击穿电压2.5次方的关系变为了1.3次方,因此相比于普通功率mosfet,在相同的导通电阻下,超结mosfet能够极大地缩小芯片面积,进而降低芯片成本。芯片面积的缩小也有利于降低器件的寄生电容。对于功率mosfet而言,低的寄生电容,特别是低的米勒电容有利于降低器件开关所需的时间,从而降低开关损耗,增加效率。此外,超结mosfet的开关时间也可以用降低米勒电容的方式来降低。

2、目前,通常采用分裂栅的方式降低超结mosfet中全电压段的米勒电容,但是采用分裂栅的方式降低全电压段的米勒电容的同时,会使得电压较大时的米勒电容极低,从而容易出现过大的dv/dt,引起应用回路中的电流过冲、rlc震荡、电磁干扰(electromagneticinterference,简称emi)等问题,且由于采用分裂栅的方式牺牲了一部分沟道电子积累层,在一定程度上导致器件导通电阻的增加。在工艺上要实现分裂栅,需要比较复杂的工艺流程,进而增加器件的制造成本。也有采用降低jfet区的掺杂浓度的方式来降低超结mosfet的米勒电容,但是降低jfet的掺杂浓度的同时会引起器件导通电阻的增加,要实现相同的导通电阻就需要更大的芯片面积,导致更大的寄生电容,进而降低器件的开关速度。此外,降低jfet区的掺杂浓度只能够降低在较低电压下的米勒电容,而对较高电压下的米勒电容无影响。

3、因此,亟需一种在不增加器件的导通电阻以及工艺难度的条件下,能够极大地优化米勒电容的超结功率mosfet。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种超结mosfet及其制作方法,用于解决现有技术中降低超级mosfet的米勒电容的同时导致导通电阻增加及工艺难度增加的问题。

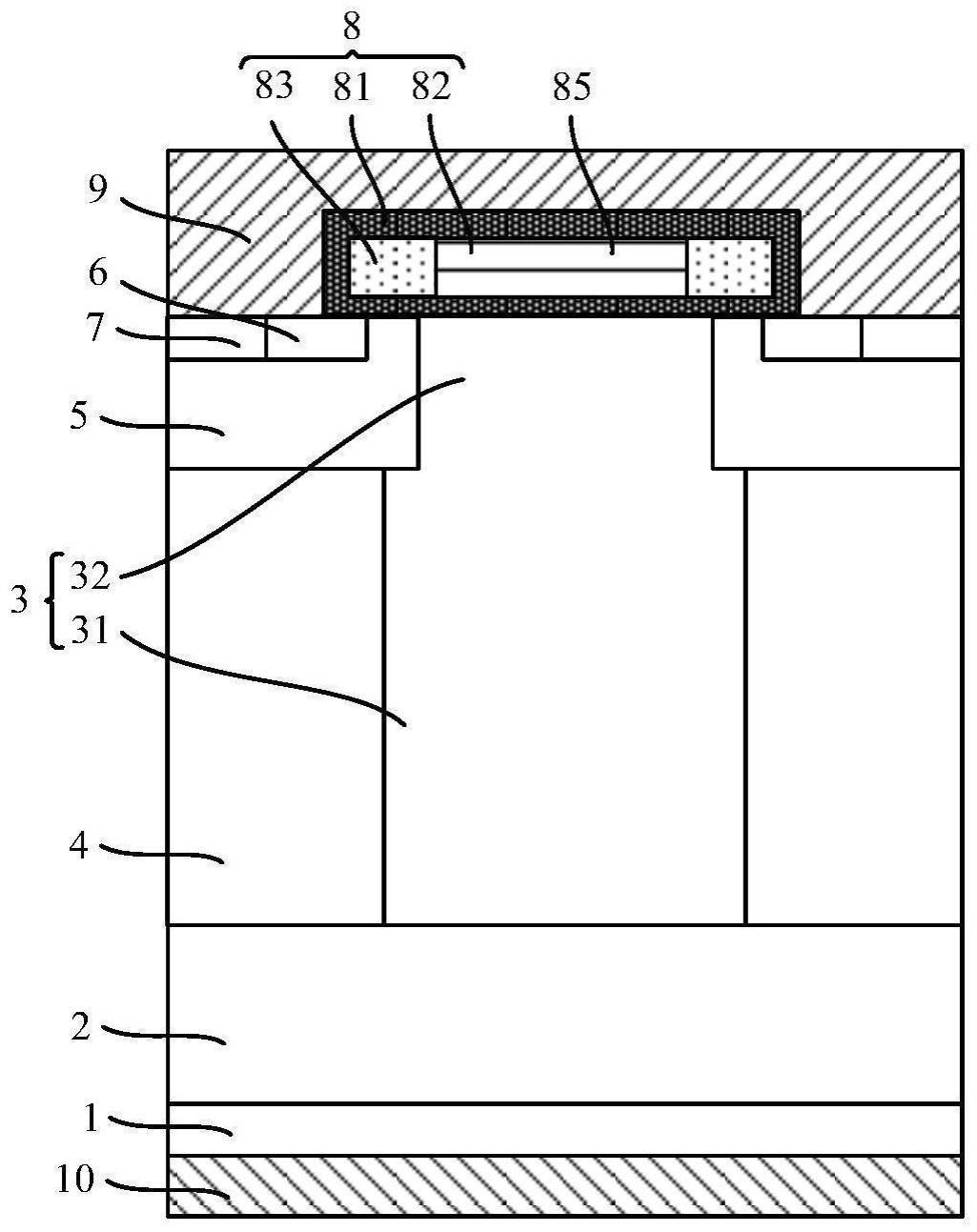

2、为实现上述目的及其他相关目的,本发明提供了一种超结mosfet,包括:

3、第一导电类型衬底;

4、第一导电类型缓冲区,位于所述衬底的上表面;

5、第一导电类型柱,设置于所述缓冲区的上表面并沿远离所述衬底的方向延伸,且所述第一导电类型柱包括第一柱区及堆叠于所述第一柱区上的第二柱区;

6、第二导电类型柱,设置于所述缓冲区的上表面且位于所述第一柱区的两侧,所述第二导电类型柱的侧壁与所述第一柱区的侧壁邻接,所述第二导电类型柱的上表面与所述第一柱区的上表面齐平;

7、第二导电类型体区,堆叠于所述第二导电类型柱上,且所述体区的上表面与所述第二柱区的上表面齐平,所述体区的侧壁与所述第二柱区的侧壁邻接;

8、邻接的第一导电类型源区及第二导电类型体接触区,位于所述体区的上表层,且所述源区和所述体接触区与所述第一导电类型柱间隔预设距离;

9、栅极结构,位于所述第一导电类型柱的上表面,至少包括栅介质层、第一栅极及位于所述第一栅极两侧的第二栅极,所述栅介质层包裹所述第一栅极与所述第二栅极,且所述第一栅极位于所述第一导电类型柱上方,所述第二栅极位于所述源区、所述第一导电类型柱、所述源区和所述第一导电类型柱之间的所述体区的上方,所述第一栅极至少包括第二导电类型掺杂区,所述第二栅极为第一导电类型;

10、源极及漏极,所述源极覆盖所述栅极结构、所述源区及所述体接触区的显露表面,所述漏极覆盖所述衬底的底面。

11、可选地,所述第二导电类型掺杂区电连接于所述第二栅极或者所述源极中的一种。

12、可选地,所述第一栅极与所述第二栅极之间还设有第一隔离介质层以隔离开所述第一栅极与所述第二栅极。

13、可选地,当所述第一栅极整体为所述第二导电类型掺杂区时,所述第二导电类型掺杂区与所述第二栅极邻接。

14、可选地,所述第二导电类型掺杂区中还包括第一浓度区及位于所述第一浓度区两侧的第二浓度区,且所述第二浓度区的掺杂浓度低于所述第一浓度区的掺杂浓度。

15、可选地,所述第一栅极中还包括第一导电类型掺杂区。

16、可选地,所述第一导电类型掺杂区位于所述第二栅极与所述第二导电类型掺杂区之间,且所述第一导电类型掺杂区的两端分别与所述第二栅极及所述第二导电类型掺杂区邻接。

17、可选地,所述第二导电类型掺杂区位于所述第一导电类型掺杂区与所述第二栅极之间,且所述第二导电类型掺杂区分别与所述第一导电类型掺杂区及所述第二栅极邻接。

18、可选地,所述第二导电类型掺杂区与所述第一导电类型掺杂区之间还设有第二隔离介质层以隔离开所述第二导电类型掺杂区与所述第一导电类型掺杂区。

19、本发明还提供了一种超结mosfet的制作方法,包括以下步骤:

20、提供一第一导电类型衬底,并于所述衬底的上表面形成第一导电类型缓冲区;

21、于所述缓冲区的上表面形成第一导电类型第一柱区及位于所述第一柱区两侧的第二导电类型柱,且所述第二导电类型柱的侧壁与所述第一柱区的侧壁邻接,所述第一柱区的上表面与所述第二导电类型柱的上表面齐平;

22、于所述第一柱区的上表面形成第一导电类型的第二柱区,所述第一柱区与所述第二柱区组成第一导电类型柱,并于所述第二柱区的两侧形成位于所述第二导电类型柱上表面并与所述第二柱区侧壁邻接的第二导电类型体区,所述体区的上表面与所述第二柱区的上表面齐平;

23、于所述体区的上表层中形成邻接的第一导电类型源区及第二导电类型体接触区,且所述源区和所述体接触区与第一导电类型柱间隔预设距离;

24、于所述第一导电类型柱的上表面形成栅极结构,所述栅极结构包括栅介质层、第一栅极及位于所述第一栅极两侧的第二栅极,所述栅介质层包裹所述第一栅极与所述第二栅极,且所述第一栅极位于所述第一导电类型柱上方,所述第二栅极位于所述源区、所述第一导电类型柱、所述源区和所述第一导电类型柱之间的所述体区的上方,所述第一栅极至少包括第二导电类型掺杂区,所述第二栅极为第一导电类型;

25、形成覆盖所述栅极结构、所述源区及所述体接触区显露表面的源极,并于所述衬底的底面形成覆盖所述衬底底面的漏极。

26、如上所述,本发明的超结mosfet及其制作方法通过重新设计所述超结mosfet的所述栅极结构,将所述栅极结构设置成至少包括所述栅介质层、所述第一栅极及位于所述第一栅极两侧的所述第二栅极,所述第一栅极至少包括第所述第二导电类型掺杂区,所述第二栅极为第一导电类型,在所述第一导电类型柱的耗尽层较窄时,通过控制所述第二导电类型掺杂区的连接方式来降低的器件的米勒电容,且当于所述第一栅极与所述第二栅极之间设置所述第一隔离介质层,降低了栅极结构的损耗,增强了所述第一栅极与所述第二栅极之间的反向击穿电压;于所述第一栅极中设置所述第一导电类型掺杂区,当所述第一导电类型掺杂区位于所述第二栅极与所述第二导电类型掺杂区之间时,通过调整所述第一导电类型掺杂区的宽度及所述第二导电类型掺杂区的连接方式来控制器件在所述第一导电类型柱的耗尽层较窄时的米勒电容,于所述第一栅极和所述第二栅极之间及所述第一导电类型掺杂区和所述第二导电类型掺杂区之间至少设置一个隔离介质层,降低了栅极结构的损耗。此外,当所述第二栅极的电压增加时,所述第一栅极下方的所述第一导电类型柱的上表面会产生感应电荷积累层,不影响器件的导通电阻,具有高度产业利用价值。

- 还没有人留言评论。精彩留言会获得点赞!