微纳真空电子器件及其制备方法与流程

本技术涉及微纳真空电子,尤其涉及一种微纳真空电子器件及其制备方法。

背景技术:

1、随着半导体向亚纳米发展,器件关键尺寸已接近材料的极限,这需要提出新的器件工作模式使得电子技术继续发展。真空电子技术是一种潜在的发展方向。使用微纳加工技术制造的真空电子器件,具备更高性能、更低工作电压,是代替半导体器件的潜在技术手段。而在现有技术中,微纳真空电子器件易出现漏电流导致电子在真空中的传导效率低,且制造难度极大,性能不稳定,成本较高。

技术实现思路

1、本技术提供了一种微纳真空电子器件及其制备方法,以解决上述现有技术中微纳真空电子器件易出现漏电流导致电子在真空中的传导效率低,且制造难度极大,性能不稳定,成本较高的问题。

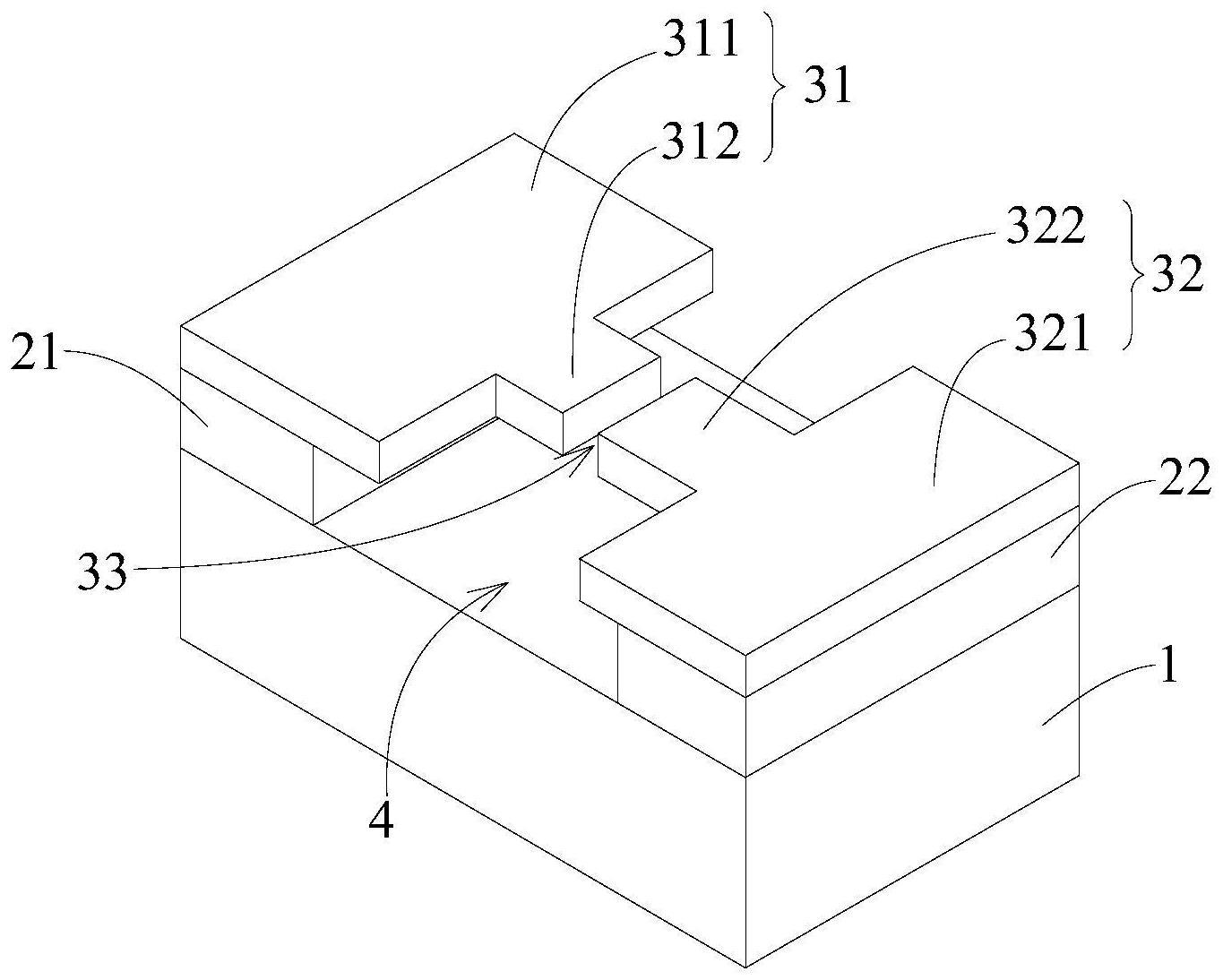

2、本技术第一方面提供了一种微纳真空电子器件,包括依次层叠设置的基底层、支撑层和电极层,所述电极层包括相对设置的第一电极和第二电极,所述第一电极的发射端和所述第二电极的接收端之间形成纳米级的电极狭缝,所述第一电极的发射端、所述第二电极的接收端和所述基底层之间形成中空区域。

3、工作时,分别对第一电极和第二电极施加负电压和正电压,第一电极作为阴极,第二电极作为阳极,当施加的电压达到阈值电压时,第一电极的发射端的电场强度达到临界值,第一电极在电场的作用下能够通过发射端发射电子至电极狭缝,第二电极能够通过接收端接收电子,使微纳真空电子器件导通,当第一电极的发射端和第二电极的接收端之间的电极狭缝为纳米级时,能够显著降低工作时施加的电压,从而降低工作时的阈值电压,使微纳真空电子器件能够工作在较低的电压环境,降低成本,且纳米级的电极狭缝中几乎不存在气体分子,能够使第一电极发射的电子在电极狭缝中呈现弹道输送,不会发生散射,能够提高电子的传导效率,从而能够提高微纳真空电子器件的通断控制效率,同时,第一电极的发射端、第二电极的接收端和基底层之间形成中空区域,使第一电极的发射端、第二电极的接收端悬置于基底层的上方,形成悬空结构,从而能够避免电子在发射过程向基底层中传导,使电子的在电极狭缝中的真空传导成为电流的主要组成部分,降低了漏电流的产生,进一步提高了电子的传导效率,提高了微纳真空电子器件的性能稳定性,且具有结构简单、容易制造、成本低的优点。

4、在一种可能的设计中,所述第一电极包括第一连接端和第一凸出端,所述第一凸出端形成为所述第一电极的发射端,所述第二电极包括第二连接端和第二凸出端,所述第二凸出端形成为所述二电极的接收端,所述支撑层包括第一支撑块和第二支撑块,所述第一连接端设置于所述第一支撑块,所述第二连接端设置于所述第二支撑块,所述第一凸出端、所述第二凸出端、所述第一支撑块、所述第二支撑块和所述基底层之间形成所述中空区域。

5、当分别对第一电极和第二电极施加负电压和正电压时,第一电极作为阴极,第一凸出端的设置能够降低第一电极的发射端面积,使第一电极的发射端的电场更易增强达到临界值,从而更易发射电子,降低了第一电极作为阴极发射电子的难度,提高了电子的传导效率,同时,第二凸出端的设置增加了第二电极可以作为阴极使用的功能,提高了微纳真空电子器件的使用情况,另外,第一支撑块和第二支撑块为第一电极和第二电极提供支撑,提高了微纳真空电极器件的结构稳定性,且增加了第一电极的发射端和第二电极的接收端与基底层之间的距离,使第一电极的发射端、第二电极的接收端悬置于基底层的上方的结构更易实现。

6、在一种可能的设计中,所述第一凸出端包括第一导通面,所述第二凸出端包括第二导通面,所述第一电极通过所述第一导通面发射电子,所述第二电极通过所述第二导通面接收电子,所述第一导通面和所述第二导通面均为平面,且所述第一导通面和所述第二导通面均与电子的发射方向垂直。

7、当第一电极和第二电极的施加电压达到阈值时,第一凸出端的第一导通面处的电场强度达到临界值,从而使电子能够通过第一导通面发射电子至电极狭缝中,第二凸出端能够通过第二导通面接收电子,使微纳真空电子器件导通,本技术的微纳真空电子器件的第一电极或第二电极通过面发射或接收电子,能够增加单位时间内发射电子的数量,从而能够提升传导电流的强度,无需制备成多个电极的阵列结构,从而降低了制备难度,更易生产制造,且第一导通面和第二导通面的面积较大,能够加快第一导通面和第二导通面传导电流时产生的焦耳热的散发,散热效果好,使第一导通面和第二导通面不易损坏,提高了微纳真空电子器件的使用寿命,提高了微纳真空电子器件的工作稳定性,降低了成本。

8、在一种可能的设计中,所述第一导通面和所述第二导通面的边缘位置处形成有弧形面。

9、弧形面的设置使第一电极或第二电极可以作为电子发射面的第一导通面和第二导通面的面积减小,使发射面的电场更易增强达到临界值,从而更易发射电子,进一步降低了发射电子的难度,使电子的传导效率进一步提高。

10、在一种可能的设计中,所述第一凸出端朝向所述第二凸出端一侧的端部形成有第一凸棱,所述第二凸出端朝向所述第一凸出端一侧的端部形成有第二凸棱,所述第一凸棱和所述第二凸棱之间形成所述电极狭缝,所述第一电极通过所述第一凸棱发射电子,所述第二电极通过所述第二凸棱接收电子。

11、第一凸棱和第二凸棱的表面曲率大,电场的强度易剧增,从而更易发射电子,进一步降低了发射电子的难度,使电子的传导效率进一步提高。

12、在一种可能的设计中,所述第一凸出端包括第一斜面,所述第一斜面与所述第一凸出端的底面的连接线形成所述第一凸棱,所述第二凸出端包括第二斜面,所述第二斜面与所述第二凸出端的底面的连接线形成所述第二凸棱。

13、第一凸棱和第二凸棱传导电流时产生的焦耳热能够传导至与第一凸棱或第二凸棱相连接的第一斜面、第一凸出端的底面、第二斜面和第二凸出端的底面,从而能够提高焦耳热的散热效率,使第一凸棱和第二凸棱的热量快速下降,使第一凸棱和第二凸棱不易损坏,提高了微纳真空电子器件的使用寿命,提高了微纳真空电子器件的工作稳定性,降低了成本。

14、在一种可能的设计中,所述第一凸出端朝向所述第二凸出端一侧的端部设置有第一导通凸起,所述第一导通凸起朝向所述第二凸出端一侧的端面形成为发射平面,所述第二凸出端朝向所述第一凸出端一侧的端部设置有第二导通凸起,所述第二导通凸起朝向所述第一凸出端一侧的端面形成为接收平面,所述发射平面与所述接收平面之间形成所述电极狭缝,所述第一电极通过所述发射平面发射电子,所述第二电极通过所述接收平面接收电子。

15、第一导通凸起和第二导通凸起的设置进一步缩短了电极狭缝的距离,降低工作时施加的电压,从而降低工作时的阈值电压,使微纳真空电子器件能够工作在更低的电压环境,且不易产生漏电流,能够进一步提高电子的传导效率。

16、在一种可能的设计中,所述电极层的厚度为50~300nm。

17、电极层的厚度为50nm~300nm时,能够满足第一电极和第二电极的使用需求,且制造难度低,不会对电极层的材料造成浪费,成本较低,能够降低微纳真空电子器件的制造难度和成本,提高微纳真空电子的合格率。

18、在一种可能的设计中,所述电极层的材质为单晶硅。

19、单晶硅体硬且脆,稳定性好,是一种比较活泼的非金属元素晶体,且随温度增加其电阻率随着温度升高和辐射强度的增大而减小,可以导电,是一种良好的半导体材料,因此可以用于微纳真空电子器件的第一电极和第二电极的制作,且易加工制造。

20、在一种可能的设计中,所述基底层为刚性结构。

21、基底层为刚性结构能够为支撑和电极层提供支撑,使第一凸出端、第二凸出端、第一支撑块、第二支撑块和基底层之间形成中空区域,第一电极的发射端、第二电极的接收端悬置于基底层的上方的结构更易实现,且提高了微纳真空电子器件的结构稳定性。

22、在一种可能的设计中,所述基底层的材质为硅片或玻璃片。

23、硅片或玻璃片具有较高的刚性能够为支撑和电极层提供支撑,且成本低、易加工、热稳定性良好,能够延长微纳真空电子器件的寿命。

24、在一种可能的设计中,所述支撑层为绝缘材料。

25、支撑层使用绝缘材料能够防止电流从第一电极的第一连接端和第二电极的第二连接端经第一支撑块和第二支撑块流向基底层,避免产生漏电流,提高电流的传导效率,提高微纳真空电子的性能稳定性。

26、在一种可能的设计中,所述支撑层的材质为氧化硅。

27、氧化硅是良好的绝缘体,质地硬且脆,能够为电极层提供良好的支撑,避免电流从电极层传导至基底层,避免产生漏电流,提高电流的传导效率,提高微纳真空电子的性能稳定性。

28、本技术第二方面提供了一种微纳真空电子器件的制备方法,所述方法包括如下步骤:

29、提供衬底,所述衬底包括依次层叠设置的基底层、支撑层和电极层。

30、该步骤中,基底层为刚性材料,如硅片、玻璃片等,为支撑层和电极层提供支撑,支撑层为绝缘材料,如氧化硅等,用于支撑电极层,电极层为厚度为50nm~300nm的单晶硅,用于导通电流。

31、在所述电极层制备硅线电极结构。

32、该步骤中,先通过光刻粗略去除部分电极层,再通过单晶硅刻蚀精细刻蚀形成电极结构,再在电极结构中制备硅线,以使电压能够施加在电极层上。

33、在所述电极结构上制备纳米级的电极狭缝,形成第一电极和第二电极。

34、该步骤中,纳米级的电极狭缝几乎不存在气体分子,能够使电子在电极狭缝中呈现弹道输送,不会发生散射,能够提高电子的传导效率。

35、去除所述第一电极的发射端、所述电极狭缝和所述第二电极的接收端与所述基底层之间的部分支撑层,使所述第一电极的发射端和所述第二电极的接收端悬置于所述基底层的上方。

36、该步骤中,可以通过湿法刻蚀支撑层,使支撑层上位于第一电极的发射端、电极狭缝和第二电极的接收端与基底层之间形成中空区域。

37、工作时,分别对第一电极和第二电极施加负电压和正电压,第一电极作为阴极,第二电极作为阳极,当施加的电压达到阈值电压时,第一电极的发射端的电场强度达到临界值,第一电极在电场的作用下能够通过发射端发射电子至电极狭缝,第二电极能够通过接收端接收电子,使微纳真空电子器件导通,当第一电极的发射端和第二电极的接收端之间的电极狭缝为纳米级时,能够显著降低工作时施加的电压,从而降低工作时的阈值电压,使微纳真空电子器件能够工作在较低的电压环境,降低成本,且纳米级的电极狭缝中几乎不存在气体分子,能够使第一电极发射的电子在电极狭缝中呈现弹道输送,不会发生散射,能够提高电子的传导效率,从而能够提高微纳真空电子器件的通断控制效率,同时,第一电极的发射端、第二电极的接收端悬置于基底层的上方,形成悬空结构,从而能够避免电子在发射过程向基底层中传导,使电子的在电极狭缝中的真空传导成为电流的主要组成部分,降低了漏电流的产生,进一步提高了电子的传导效率,提高了微纳真空电子器件的性能稳定性,且具有结构简单、容易制造、成本低的优点。

38、在一种可能的设计中,所述在所述电极结构上制备纳米级的电极狭缝,形成第一电极和第二电极,具体包括:

39、在所述支撑层远离所述基底层的一侧形成第一掩膜层,所述第一掩膜层覆盖所述硅线电极结构上用于形成所述第一电极的部分。

40、该步骤中,在支撑层远离基底层的一侧形成第一掩膜层,并刻蚀第一掩膜层,使第一掩膜层覆盖硅线电极结构上用于形成第一电极的部分,以便后续制备电极狭缝处的掩膜墙。

41、在所述支撑层远离所述基底层的一侧形成第二掩膜层,所述第二掩膜层覆盖所述第一掩膜层和所述硅线电极结构上用于形成所述第二电极和所述电极狭缝的部分。

42、该步骤中,在支撑层远离基底层的一侧形成第二掩膜层,以便后续制备电极狭缝处的掩膜墙。

43、去除覆盖在所述第一掩膜层上方的第二掩膜层和覆盖在所述硅线电极结构上用于形成所述第二电极上方的第二掩膜层,保留所述硅线电极结构上用于形成所述电极狭缝位置处的第二掩膜层。

44、该步骤中,使用干法刻蚀第二掩膜层,保留硅线电极结构上用于形成电极狭缝位置处的第二掩膜层,以便后续制备电极狭缝处的掩膜墙。

45、去除所述第一掩膜层,以使位于所述硅线电极结构上用于形成所述电极狭缝位置处的第二掩膜层形成掩膜墙。

46、该步骤中,干法刻蚀第一掩膜层,保留剩余的第二掩膜层,使位于硅线电极结构上用于形成电极狭缝位置处的第二掩膜层形成掩膜墙,以便后续电极狭缝的制备。

47、生长位于所述掩膜墙两侧的所述电极层,使所述电极层的厚度增加。

48、该步骤中,生长位于掩膜墙两侧的电极层,使电极层的厚度增加,避免去除掩膜墙时掩膜墙两侧电极层遭到损坏,且能够补偿后续制备电极狭缝时去除的电极层的厚度,使电极层的厚度满足使用需求。

49、去除部分所述电极层和全部第二掩膜层,形成电极狭缝,使所述电极层形成所述第一电极和所述第二电极。

50、该步骤中,使用干法刻蚀,均匀去除相同厚度的去除电极层和第二掩膜层,由于掩膜墙覆盖的电极层较薄,因此掩膜墙时掩膜墙所覆盖的电极层首先发生断裂,此时形成电极狭缝。

51、纳米级的电极狭缝能够降低工作时施加的电压,从而降低工作时的阈值电压,使微纳真空电子器件能够工作在较低的电压环境,降低成本,且纳米级的电极狭缝中几乎不存在气体分子,能够使第一电极发射的电子在电极狭缝中呈现弹道输送,不会发生散射,能够提高电子的传导效率,从而能够提高微纳真空电子器件的通断控制效率,且制备方法简单,成本低,能够降低微纳真空电子器件的成本。

52、在一种可能的设计中,所述去除所述第一电极的发射端、所述电极狭缝和所述第二电极的接收端与所述基底层之间的部分支撑层,具体包括:

53、使用稀释的氢氟酸刻蚀支撑层上位于所述第一电极的发射端、所述电极狭缝和所述第二电极的接收端与所述基底层之间的部分。

54、该步骤中,将形成电极狭缝的衬底放入稀释的氢氟酸中,使材质为氧化硅的支撑层与氢氟酸进行化学反应,均匀刻蚀支撑层,支撑层上位于第一电极的发射端、电极狭缝和第二电极的接收端与基底层之间的部分形成中空区域。

55、使第一电极的发射端、第二电极的接收端悬置于基底层的上方,形成悬空结构,从而能够避免电子在发射过程向基底层中传导,使电子的在电极狭缝中的真空传导成为电流的主要组成部分,降低了漏电流的产生,进一步提高了电子的传导效率,提高了微纳真空电子器件的性能稳定性,且具有结构简单、容易制造、成本低的优点。

56、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本技术。

- 还没有人留言评论。精彩留言会获得点赞!