一种沟槽肖特基结构制作方法与流程

1.本技术涉及半导体工艺技术领域,具体而言,涉及一种沟槽肖特基结构制作方法。

背景技术:

2.在半导体器件的生产过程中,特别是沟槽肖特基器件制造中,通常需要将外延层表面的多晶硅去除,并保留沟槽内的多晶硅,以实现后续的工艺。

3.目前常规的制作工艺为在进行多晶硅填充后,采用多晶硅平坦化的方式,将外延层表面的多晶硅去除。

4.然而,由于目前多晶硅平坦化一般采用干法刻蚀工艺,需要用到干法刻蚀设备,因此其工艺成本相对较高,同时其工艺流程也相对复杂。

5.综上,现有技术中在去除多晶硅时,存在成本高,工艺复杂的问题。

技术实现要素:

6.本技术的目的在于提供一种沟槽肖特基结构制作方法,以解决现有技术中在去除多晶硅时存在的成本高、工艺复杂的问题。

7.为了实现上述目的,本技术实施例采用的技术方案如下:

8.本技术实施例提供了一种沟槽肖特基结构制作方法,所述沟槽肖特基结构制作方法包括:

9.利用图像化光刻板层在外延层上刻蚀沟槽;

10.基于所述沟槽的内壁生长介质层;

11.沿所述外延层的表面沉积多晶硅,其中,所述多晶硅位于所述外延层的表面与所述沟槽内;

12.将位于所述外延层表面的多晶硅氧化,以形成氧化层;

13.基于所述氧化层刻蚀接触孔,并露出沟槽;

14.基于所述接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构。

15.可选地,将位于所述外延层表面的多晶硅氧化包括:

16.将外延层表面的所有多晶硅氧化,且沟槽内的多晶硅不氧化;或

17.将外延层表面的所有多晶硅与沟槽内预设深度的多晶硅氧化。

18.可选地,当所述光刻板层为sio2层时,所述基于所述氧化层刻蚀接触孔的步骤包括:

19.在预设区域同步刻蚀氧化层与光刻板层,以形成接触孔。

20.可选地,当所述光刻板层为非sio2层时,所述基于所述氧化层刻蚀接触孔的步骤包括:

21.在预设区域先刻蚀氧化层,再刻蚀光刻板层,以形成接触孔。

22.可选地,基于所述接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构的步骤包括:

23.基于所述接触孔沉积势垒金属;

24.对所述势垒金属进行刻蚀,以刻蚀出预设图形。

25.可选地,基于所述接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构的步骤包括:

26.基于所述势垒金属的表面沉积正面金属;

27.对所述正面金属进行刻蚀,以刻蚀出预设图形。

28.可选地,基于所述势垒金属的表面沉积正面金属的步骤包括:

29.基于所述势垒金属的表面沉积al、ti、ni以及ag中一种或多种金属。

30.可选地,基于所述沟槽的内壁生长介质层的步骤包括:

31.基于所述沟槽的内壁生长sio2层。

32.相对于现有技术,本技术具有以下有益效果:

33.本技术提供了一种沟槽肖特基结构制作方法,首先利用图像化光刻板层在外延层上刻蚀沟槽,再基于沟槽的内壁生长介质层,然后沿外延层的表面沉积多晶硅,其中,多晶硅位于外延层的表面与沟槽内,再将位于外延层表面的多晶硅氧化,以形成氧化层,然后基于氧化层刻蚀接触孔,并露出沟槽,最后基于接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构。由于本技术在沉积多晶硅后,将位于外延层表面的多晶硅氧化,使得可以将外延层表面的多晶硅转变为氧化层使用,无须沉积额外的氧化层,简化了制作工艺,同时节省了制作成本。

34.为使本技术的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

附图说明

35.为了更清楚地说明本技术实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本技术的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它相关的附图。

36.图1为现有技术中制作沟槽肖特基结构的第一步骤对应的剖面示意图。

37.图2为现有技术中制作沟槽肖特基结构的第二步骤对应的剖面示意图。

38.图3为现有技术中制作沟槽肖特基结构的第三步骤对应的剖面示意图。

39.图4为现有技术中制作沟槽肖特基结构的第四步骤对应的剖面示意图。

40.图5为现有技术中制作沟槽肖特基结构的第五步骤对应的剖面示意图。

41.图6为现有技术中制作沟槽肖特基结构的第六步骤对应的剖面示意图。

42.图7为现有技术中制作沟槽肖特基结构的第七步骤对应的剖面示意图。

43.图8为现有技术中制作沟槽肖特基结构的第八步骤对应的剖面示意图。

44.图9为现有技术中制作沟槽肖特基结构的第九步骤对应的剖面示意图。

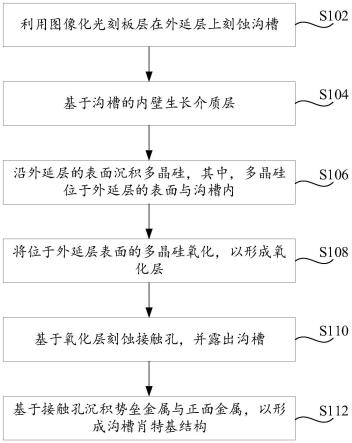

45.图10为本技术实施例提供的示例性流程示意图。

46.图11为本技术实施例提供的沟槽肖特基结构制作方法中s104对应的剖面示意图。

47.图12为本技术实施例提供的沟槽肖特基结构制作方法中s106对应的剖面示意图。

48.图13为本技术实施例提供的沟槽肖特基结构制作方法中s108对应的剖面示意图。

mechanical polish,化学机械研磨)工艺,也可以采用干法刻蚀工艺,其中,cmp工艺是集成电路制造过程中实现晶圆表面平坦化的关键工艺。与传统的纯机械或纯化学的抛光方法不同,cmp工艺是通过表面化学作用和机械研磨的技术结合来实现晶圆表面微米/纳米级不同材料的去除,从而达到晶圆表面纳米级平坦化。cmp的主要工作原理是在一定压力下及抛光液的存在下,被抛光的晶圆对抛光垫做相对运动,借助纳米磨料的机械研磨作用与各类化学试剂的化学作用之间的高度有机结合,使被抛光的晶圆表面达到高度平坦化、低表面粗糙度和低缺陷的要求。

62.而干法刻蚀是用等离子体进行薄膜刻蚀的技术。当气体以等离子体形式存在时,它具备两个特点:一方面等离子体中的这些气体化学活性比常态下时要强很多,根据被刻蚀材料的不同,选择合适的气体,就可以更快地与材料进行反应,实现刻蚀去除的目的;另一方面,还可以利用电场对等离子体进行引导和加速,使其具备一定能量,当其轰击被刻蚀物的表面时,会将被刻蚀物材料的原子击出,从而达到利用物理上的能量转移来实现刻蚀的目的。因此,干法刻蚀是晶圆片表面物理和化学两种过程平衡的结果。

63.然而,采用cmp工艺需要用到专门的研磨设备,而采用干法刻蚀工艺则需要用到干法刻蚀设备的,无论是研磨设备还算干法刻蚀设备,其价格均相对昂贵,因此沟槽肖特基产品的生产成本较高。

64.请参阅图6,继续在外延层的表面沉积介质层,该介质层可以为sio2层,也可以为氮化物层,在此不做限定。

65.继续参阅图7,需要刻蚀介质层,以形成接触孔,当然地,外延层表面的场板氧化层也随着介质层一并刻蚀掉。

66.继续参阅图8与图9,为了实现肖特基接触,继续沿外延层与介质层的表面沉积的势垒金属。势垒金属与外延层之间形成肖特基接触。同时,为了在封装使引出引脚,在势垒金属的表面继续生长正面金属,然后继续后续常规制造步骤,例如制作钝化层等步骤,形成沟槽肖特基产品,在此不再赘述。

67.常规的沟槽肖特基产品制作工艺相对成熟,且介质层厚度可以随意调整。然而,对于整个工艺而言,整个工艺相对复杂,沟槽刻蚀后去除hardmask容易产生水印,需要多晶干法刻蚀设备,需要介质层淀积设备,导致沟槽肖特基产品的生产成本较高。

68.有鉴于此,为了解决上述技术问题,本技术提供了一种沟槽肖特基结构制作方法,通过将外延层表面的多晶硅氧化再去除的方式,达到简化工艺,且降低生产成本的效果。

69.下面对本技术提供的沟槽肖特基结构制作方法进行示例性说明:

70.作为一种可选的实现方式,请参阅图10,该沟槽肖特基结构制作方法包括:

71.s102,利用图像化光刻板层在外延层上刻蚀沟槽。

72.s104,基于沟槽的内壁生长介质层。

73.s106,沿外延层的表面沉积多晶硅,其中,多晶硅位于外延层的表面与沟槽内。

74.s108,将位于外延层表面的多晶硅氧化,以形成氧化层。

75.s110,基于氧化层刻蚀接触孔,并露出沟槽。

76.s112,基于接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构。

77.其中,与现有技术相似,在沉积多晶硅时,也经过沟槽刻蚀、介质层生长以及多晶填充的工艺,在此不做赘述。与现有技术不同的是,本技术中在刻蚀沟槽后,无须去除光刻

板层,而是直接沉积多晶硅,并在后续工艺中再去除光刻板层。现有技术中,去除光刻板一般采用湿法腐蚀的工艺,因此,与现有技术相比,本技术此时减少一步湿法腐蚀工艺,进而减少了缺陷产生可能性。需要说明的是,本技术提供的介质层可以为氧化物层,也可以为氮化物。

78.当介质层为氧化物层时,其可以为sio2层。并且,在制作介质层时,实际先沿外延层的表面沉积介质层,然后对介质层进行刻蚀。以形成与沟槽的内壁相连的介质层,且该介质层的厚度较薄。

79.请参阅图11,在制作介质层后,此时沟槽内壁连接有介质层,同时外延层的表面连接有光刻板层。

80.此时沿外延层的表面沉积多晶硅,形成如图12所示的结构,此时,多晶位于沟槽内及外延层的表面。并且,外延层的表面还连接有光刻板层。

81.如图13所示,将外延层表面的多晶硅氧化,并形成氧化层,使得在后续工艺中,无须沉积额外的氧化层,简化了制作工艺,同时无须氧化层沉积设备,达到了减小生产成本的效果。

82.需要说明的是,在氧化过程中,需要控制多晶硅的氧化深度。作为一种实现方式,可以将外延层表面的所有多晶硅氧化,且沟槽内的多晶硅不氧化。作为另一种实现方式,将外延层表面的所有多晶硅与沟槽内预设深度的多晶硅氧化。例如,在氧化过程中,可以将沟槽与外延层持平的表面的500~600埃深度的多晶硅同时氧化,可根据实际需求调节。

83.换言之,本技术为了防止外延层表面的多晶硅未被氧化完全,影响后续刻蚀工艺,需要保证氧化深度大于或等于外延层表面的多晶硅厚度。同时,在去除外延层表面的多晶硅时,也可直接通过去除氧化层的方式去除,提高了多晶去除的均匀性和多晶去除深度的精确控制。

84.请参阅图14,继续基于氧化层刻蚀接触孔,并露出沟槽。此时只需对氧化层进行去除,无须用到现有技术中去除多晶硅的设备,因此工艺更加简单,成本更低。

85.需要说明的是,当光刻板层为sio2层时,由于多晶硅氧化形成的氧化物也为sio2,因此基于氧化层刻蚀接触孔的步骤包括:

86.在预设区域同步刻蚀氧化层与光刻板层,以形成接触孔。

87.而当光刻板层为非sio2层时,此时基于氧化层刻蚀接触孔的步骤包括:

88.在预设区域先刻蚀氧化层,再刻蚀光刻板层,以形成接触孔。

89.即若氧化层与光刻板层的材料相同,则在刻蚀接触孔时,可以将氧化层与光刻板层一并去除。而若氧化层与光刻板层的材料不同,则在刻蚀接触孔时,可以先刻蚀氧化层,在刻蚀光刻板层。

90.如图15与图16所示,可以基于接触孔先后沉积势垒金属与正面金属,其中,势垒金属用于肖特基基础,正面金属用于作为封装走线。

91.可选地,实际工艺中,s112包括:

92.基于接触孔沉积势垒金属;

93.对势垒金属进行刻蚀,以刻蚀出预设图形。

94.然后基于势垒金属的表面沉积正面金属;

95.对正面金属进行刻蚀,以刻蚀出预设图形。

96.并且,正面金属可以为al、ti、ni以及ag中一种或多种金属。

97.可以理解地,本技术提供的沟槽肖特基结构制作方法至少具有以下有益效果:

98.第一,由于在利用光刻板层刻蚀沟槽后,并不直接去除光刻板层,因此减少了一次湿法腐蚀工艺。

99.第二,多晶硅采用氧化工艺可以有效控制多晶保留深度和均匀性。

100.第三,多晶硅使用氧化工艺可以减少多晶表面损伤。

101.第四,多晶使用氧化工艺可以减少一次多晶硅刻蚀和介质层淀积,进而减少设备投资和生产成本,同时使制作工艺得以简化。

102.综上所述,本技术提供了一种沟槽肖特基结构制作方法,首先利用图像化光刻板层在外延层上刻蚀沟槽,再基于沟槽的内壁生长介质层,然后沿外延层的表面沉积多晶硅,其中,多晶硅位于外延层的表面与沟槽内,再将位于外延层表面的多晶硅氧化,以形成氧化层,然后基于氧化层刻蚀接触孔,并露出沟槽,最后基于接触孔沉积势垒金属与正面金属,以形成沟槽肖特基结构。由于本技术在沉积多晶硅后,将位于外延层表面的多晶硅氧化,使得可以将外延层表面的多晶硅转变为氧化层使用,无须沉积额外的氧化层,简化了制作工艺,同时节省了制作成本。

103.以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

104.对于本领域技术人员而言,显然本技术不限于上述示范性实施例的细节,而且在不背离本技术的精神或基本特征的情况下,能够以其它的具体形式实现本技术。因此,无论从哪一点来看,均应将实施例看作是示范性的,而且是非限制性的,本技术的范围由所附权利要求而不是上述说明限定,因此旨在将落在权利要求的等同要件的含义和范围内的所有变化囊括在本技术内。不应将权利要求中的任何附图标记视为限制所涉及的权利要求。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1