一种低漏电的TVS管结构及其制作方法与流程

一种低漏电的tvs管结构及其制作方法

技术领域

1.本发明属于半导体技术领域,具体涉及一种低漏电的tvs管结构及其制作方法。

背景技术:

2.tvs是一种管形式的高效能保护器件,主要用于对电路元件进行快速过电压保护。它能吸收功率高达数千瓦浪涌信号,用以防止外部瞬态静电、浪涌电流对电路元件造成损害。它的应用十分广泛,如:家用电器;电子仪器;仪表;精密设备;计算机系统;通讯设备;rs232、485及can等通讯端口;isdn的保护;i/o端口;ic电路保护;音、视频输入;交、直流电源;电机、继电器噪声的抑制等各个领域。

3.作为全球电子产品主要的生产基地,中国是tvs产品的主要消费地区。tvs广泛应用于各类消费类电子产品中,如手机、平板电脑、数码相机等,对于这些便携式低功耗设备来说,低漏电流是非常必要的。常规普通p-n结的tvs管是由n型衬底经n型外延,再掺杂硼;或由p型衬底经p型外延再掺杂磷,形成p-n结型tvs管,其p-n结存在漏电及结电容大的缺点。

技术实现要素:

4.为了解决现有技术中存在的上述问题,本发明提供了一种低漏电的tvs管结构及其制作方法。本发明要解决的技术问题通过以下技术方案实现:

5.第一方面,本发明提供的一种低漏电的tvs管结构,包括自下而上依次为n+衬底层以及n-外延层,

6.在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;

7.在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;

8.在n+衬底层的背面设置有金属层,作为tvs管的阴极。

9.可选的,p+环的扩区深度为4-6um;p+注入区的扩区深度为1-2μm。

10.第二方面,本发明提供的一种低漏电的tvs管结构的制作方法包括:

11.获取n+衬底;

12.在n+衬底生长n-外延层;

13.在n-外延层光刻出p+环区域;

14.在p+环区域注入硼之后进行退火处理,形成p+环区;

15.在p+环区的中间区域光刻出p+注入区域;

16.在p+注入区域注入硼之后进行退火处理,形成p+注入区;

17.通过光刻孔在p+注入区形成欧姆孔;

18.在欧姆孔沉积金属,以使金属与p+注入区的欧姆孔形成欧姆接触,作为tvs管的阳极;

19.在获取n+衬底背面进行金属化,作为tvs芯片的阴极。

20.可选的,p+环区域光刻时的扩区深度小于p+区光刻时的扩区深度。

21.可选的,p+环的扩区深度为4-6um;p+注入区的扩区深度为1-2μm。

22.本发明的有益效果:

23.本发明提供的一种低漏电的tvs管结构及其制作方法,制作出低漏电的tvs管结构在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;在n+衬底层的背面设置有金属层,作为tvs管的阴极。相比于常规的tvs管结构,本发明可以降低tvs芯片的反向漏电流,提高了tvs芯片的性能。以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

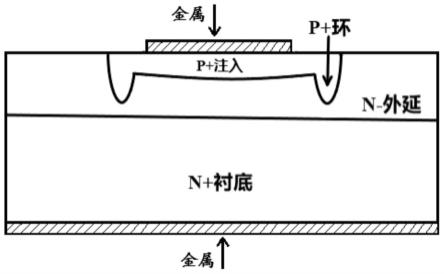

24.图1是本发明实施例提供的一种低漏电的tvs管的结构示意图;

25.图2是本发明实施例提供的一种低漏电的tvs管结构的制作方法的流程示意图;

26.图3是本发明实施例提供的形成p+环区的结构示意图;

27.图4为常规普通tvs管的结构设计图。

具体实施方式

28.下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

29.如图1所示,本发明提供的一种低漏电的tvs管结构,包括自下而上依次为n+衬底层以及n-外延层,

30.在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;

31.在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;

32.在n+衬底层的背面设置有金属层,作为tvs管的阴极。

33.其中,p+环的扩区深度为4-6um;p+注入区的扩区深度为1-2μm。

34.值得说明的是:常规tvs管的主结边缘处易产生漏电;本发明的采用tvs管结构中p+环可以增大主结处的曲率半径,同时减小主结的侧面电容,抑制电场集中,从而减小tvs管结构体内漏电的产生;而且,p+环的浓度相对于主结而言,其为淡p区,从而达到减小主结边缘表面漏电的效果。

35.本发明提供的一种低漏电的tvs管结构,在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;在n+衬底层的背面设置有金属层,作为tvs管的阴极。相比于常规的tvs管结构,本发明可以降低tvs芯片的反向漏电流,提高了tvs芯片的性能。

36.如图2所示,本发明提供的一种低漏电的tvs管结构的制作方法包括:

37.s1,获取n+衬底;

38.s2,在n+衬底生长n-外延层;

39.s3,在n-外延层光刻出p+环区域;

40.s4,在p+区域注入硼之后进行退火处理,形成p+环区;

41.如图3示,图3光刻出p+环区域的结构示意图,在图3中p+环区域位于p+注入区域外围,包围p+注入区。

42.s5,在p+环区的中间区域光刻出p+注入区域;

43.s6,在p+注入区域注入硼之后进行退火处理,形成p+注入区;

44.其中,p+环区域光刻时的扩区深度小于p+区光刻时的扩区深度。p+环的扩区深度为4-6um;p+注入区的扩区深度为1-2μm。

45.s7,通过光刻孔在p+注入区形成欧姆孔;

46.s8,在欧姆孔沉积金属,以使金属与p+注入区的欧姆孔形成欧姆接触,作为tvs管的阳极;

47.s9,在获取n+衬底背面进行金属化,作为tvs芯片的阴极。

48.本发明最终形成的低漏电的tvs管结构为图1所示,在图1中自下而上依次为n+衬底层以及n-外延层,在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;在n+衬底层的背面设置有金属层,作为tvs管的阴极。

49.本发明提供的一种低漏电的tvs管结构制作方法,制作出低漏电的tvs管结构在n-外延层中包括通过注入硼及硼退火的p+环区域以及p+注入区,p+注入区位于p+环区域之间的中间区域,并与周围的p+环区域联通;在p+注入区上沉淀有金属层,金属层与p+注入区刻蚀的欧姆孔形成欧姆接触,作为tvs管的阳极;在n+衬底层的背面设置有金属层,作为tvs管的阴极。相比于常规的tvs管结构,本发明可以降低tvs芯片的反向漏电流,提高了tvs芯片的性能。

50.将上述低漏电的tvs管结构应用于实际的tvs管芯片制作中,通过实际产品的流片进行设计及结构验证;

51.具体实现步骤为:将本发明设计的低漏电的tvs管结构应用于tvs产品的版图设计中,随后在半导体芯片的生产线上进行流片;同时对未使用该结构的相同面积的常规p-n结tvs管进行了对比流片,流片完成后对得到的硅片进行出片前测试,硅片采用五点法测试,即在硅片的上中下左右各随机检测一个管芯进行参数测试。

52.采用新结构的tvs芯片与常规结构的tvs芯片的对比如表1所示。

53.表1低漏电结构tvs芯片与常规结构tvs芯片的性能数据

[0054][0055]

常规的p-n结tvs管如图4所示,经过对常规的p-n结tvs管及本发明的低漏电的tvs管结构的芯片进行对比测试。本发明图1所示的低漏电tvs管结构设计的tvs芯片相比于采用图1所示的常规结构的tvs芯片。从表1的结构可以得出,本发明所设计的芯片在相同电压下,经统计漏电减小了80%,提高了性芯片的性能。

[0056]

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1