一种将半导体衬底主体与其上功能层进行分离的方法与流程

一种将半导体衬底主体与其上功能层进行分离的方法

1.本技术是申请日为2016年9月14日,进入中国国家阶段的日期为2018 年4月2日,国家申请号为2016800538558、发明名称为“一种将半导体衬底主体与其上功能层进行分离的方法”的发明专利申请的分案申请。

技术领域

2.本发明涉及电子器件的制造技术领域,具体涉及一种将半导体衬底主体与其上功能层进行分离的方法。

背景技术:

3.半导体材料被广泛应用于电子器件的制造,半导体材料的应用与人们的日常生活和尖端科技都息息相关。半导体材料已经从上世纪以硅、锗为代表的第一代,发展到以碳化硅、氮化镓等为代表的第三代。无论是基于第一代、第二代或第三代半导体材料的电子器件制造工艺,都离不开半导体衬底,半导体衬底的成本直接关系着衬底上制作的电子器件的成本。第一代和第二代半导体衬底大都由溶体法生长制备,第三代半导体衬底则主要由气相生长制备如化学气相沉积(cvd),金属化学气相沉积(mocvd),物理气相传输(pvt),和氢化物气相外延(hvpe),等。第三代半导体衬底的生产成本要明显高于第一代和第二代半导体衬底的生产成本。因此,降低半导体衬底的成本,特别是降低第三代半导体衬底的成本对于第三代半导体电子器件的普及应用会带来极大的好处。

4.上世纪90年代,离子切割薄膜转移技术(smart-cut)被用于制作soi (siliconon insulator)衬底,离子切割薄膜转移技术是基于离子注入方法分离衬底与衬底薄膜层的技术。soi制作工艺是首先在施主硅衬底表面制作一层微米量级厚度的二氧化硅层,然后将氢离子经高压加速打入表面已制作了氧化层的硅衬底,氢离子在高电压加速作用下,穿过二氧化硅层到达下面的硅衬底并停留在硅衬底中,产生离子损伤,离子损伤层在硅衬底表面下的深度取决于离子加速电压的高低;电压越高,离子损伤层在硅衬底表面下的深度越深。通常离子损伤层位于硅衬底下距离二氧化硅层1微米到二十几微米处,离子注入后的施主硅衬底与受主硅衬底在二氧化硅表面进行键合,键合后的两片硅衬底经过一个200℃-500℃的温度退火,退火过程中,氢离子在损伤层内聚合形成氢气分子,使原来的微损伤沿着损伤层横向扩展,造成施主硅衬底在损伤层处分离。施主硅衬底可重新利用,而分离后的受主硅衬底经热处理,表面硅原子重新分布以消除离子注入造成的损伤,在二氧化硅氧化层上有一层微米厚度的硅单晶薄膜,其后电子器件的制作就在硅单晶薄膜上进行,受主衬底只是起到支撑作用,这就是soi衬底。其后,离子切割薄膜转移技术也被用于其它半导体薄膜衬底制备,如转移gan、sic等薄膜到硅或氧化物衬底上,以降低衬底价格,与soi衬底不同的是,因gan和 sic通常转移到绝缘体上,gan、sic施主衬底上无需制作氧化层。在用离子切割薄膜转移技术制作薄膜衬底的过程中,离子注入深度,单位面积离子注入剂量,受主与施主衬底表面键合,以及键合后的退火是离子切割薄膜转移技术主要组成要素,而受主与施主衬底表面键合则是离子切割薄膜转移技术成败的关键一步。如果受主与施主衬底表面键合

不好,在退火过程中,受主与施主衬底可能产生分离,损伤层上的薄膜得不到有效支撑,则薄膜转移失败、或损坏薄膜。为了保证施主与受主衬底的键合,对衬底在键合表面的加工要求非常高,这对sic一类高硬度的半导体衬底的加工是一个很大的挑战。此外,成功分离后的薄膜表面因表面平整度和离子轰击造成的损伤,也需要热处理或表面再加工。

5.过去几年,stephen,w.bedell等用

‘

撕剥离(spalling)’法实现了硅,锗,砷化稼,氮化稼衬底上簿膜或簿膜器件的分离。撕剥离的工作原理是在半导体衬底上制作应力导入层,在应力导入层上粘连胶带,通过撕拉胶带造成衬底簿膜随应力导入层一起分离。撕剥离法需要通过精确控制应力导入层的应力来控制衬底簿膜分离的厚度,为大规模生产造成困难。另外,尽管理论上可以,撕剥离法未见成功分离硬质衬底如sic的报道。相较于撕剥离技术,本发明可通过控制离子注入深度控制分离的簿膜厚度,应力导入层中的应力无需像撕剥离技术中精确控制,为大规模生产带来便利。本发明无需在在应力导入层上粘连胶带,可制作厚应力导入层作为分离簿膜的支撑,及导电层等。此外,本发明还可分离硬质半导体衬底如碳化硅(sic)。另一可能的优点是本发明分离的簿膜材料应比撕剥离技术分离的簿膜产生较少的分离缺陷,因本发明事先引入了损伤层。

技术实现要素:

6.本发明所要解决的技术问题是现有的离子切割薄膜转移技术工艺复杂,受离子注入深度、单位面积离子注入剂量以及受主衬底和施主衬底键合强度影响很大;尤其是第三代半导体如sic,施主与受主衬底的键合没有得到很好的解决。相较于撕剥离技术,本发明更适合大规模生产,可分离硬质半导体衬底如sic,及产生较少的分离缺陷,对器件的影响小。

7.本发明解决上述技术问题的技术方案包括如下几种:

8.一种将半导体衬底主体与其上功能层进行分离的方法,包括以下步骤:

9.步骤1):在半导体衬底上表面进行离子注入,离子注入深度为0.1μ m-100μm,离子注入后在半导体衬底表面下产生一层离子损伤层;

10.步骤2):在经步骤1)处理后的半导体衬底上表面制备功能层;

11.步骤3):将半导体衬底及其上的功能层在离子损伤层处进行分离。

12.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供离子注入的半导体衬底,离子注入通过半导体衬底上表面,离子注入深度位于上表面下0.1μm-100μm,离子注入在半导体衬底表面下产生一层离子损伤层;在离子注入的半导体衬底上表面制备功能层;在所述功能层上制作至少一层应力导入层,至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力;由此能够将半导体衬底及其上的功能层在离子损伤层处进行分离。

13.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供半导体衬底,已通过半导体衬底上表面离子注入,离子注入深度位于上表面下 0.1μm-100μm,离子注入在半导体衬底表面下产生一层离子损伤层,并且半导体衬底上表面在离子注入后已制作功能层;在所述功能层上制作至少一层应力导入层,至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力;由此能够将半导体衬底及其上的功能层在离子损伤层处进行分离。

14.一种将半导体衬底主体与其上功能层进行分离的方法,包括:通过半导体衬底上表面离子注入,离子注入深度位于上表面下0.1μm

–

100μm,离子注入在半导体衬底表面下产生一层离子损伤层;在离子注入的半导体衬底上表面制备功能层;在所述功能层上制作至少一层应力导入层,至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力;由此能够将半导体衬底及其上的功能层在离子损伤层处进行分离。

15.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供半导体衬底,已通过半导体衬底上表面离子注入,离子注入深度位于上表面下0.1 μm

–

100μm,离子注入在半导体衬底表面下产生一层离子损伤层,并且半导体衬底上表面在离子注入后已制作功能层;由此能够将半导体衬底及其上的功能层通过施加至少一层应力层后在离子损伤层处进行分离,所施加的至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力。

16.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供离子注入的半导体衬底,离子注入通过半导体衬底上表面,离子注入深度位于上表面下0.1μm-100μm,离子注入在半导体衬底表面下产生一层离子损伤层;在离子注入的半导体衬底上表面制备功能层;由此能够将半导体衬底及其上的功能层通过施加至少一层应力层后在离子损伤层处进行分离,所施加的至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力。

17.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供半导体衬底,已通过半导体衬底上表面离子注入,离子注入深度位于上表面下 0.1μm-100μm,离子注入在半导体衬底表面下产生一层离子损伤层,并且半导体衬底上表面在离子注入后已制作功能层;在提供的半导体衬底功能层上进一步制作功能层;由此能够将半导体衬底及其上的功能层通过施加至少一层应力层后在离子损伤层处进行分离,所施加的至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力。

18.一种将半导体衬底主体与其上功能层进行分离的方法,包括:提供半导体衬底,已通过半导体衬底上表面离子注入,离子注入深度位于上表面下 0.1μm-100μm,离子注入在半导体衬底表面下产生一层离子损伤层,并且半导体衬底上表面在离子注入后已制作功能层;在提供的半导体衬底功能层上进一步制作功能层;在所述功能层上制作至少一层应力导入层,至少一层应力导入层中存在张应力,至少一层应力导入层在功能层中产生压应力;由此可将半导体衬底及其上的功能层在离子损伤层处进行分离。

19.本发明的有益效果是:本发明的方法在离子注入后的衬底上先进行功能层或半导体电子器件的制备,然后在离子损伤层进行分离,且本发明直接在半导体衬底原表面进行功能层或半导体电子器件的制备,避免了通常离子切割薄膜转移技术在分离面的缺陷。由于离子的注入深度决定了半导体衬底薄膜的厚度,本发明的半导体衬底具有与soi薄膜相同的作用效果,且不需要键合工艺,减少了生产工艺,降低了生产成本;现有的离子切割薄膜转移的衬底需要热处理或抛光才能制备电子器件,而本发明则是在原衬底表面进行功能层或半导体电子器件的制备,且具有相同的效果;现有的离子切割薄膜转移衬底在制备过程中的离子注入剂量需要达到或超过能够在衬底表面产生气泡的剂量,而本发明的离子注入剂量则只需保证不会在衬底表面产生气泡损伤即可。

20.在上述技术方案的基础上,本发明还可以做如下改进。

21.进一步,所述半导体衬底包括:半导体单晶片,或半导体单晶片以及在半导体单晶片上外延生长出的半导体外延层,或在氧化物单晶片上外延生长出的半导体外延层。

22.进一步,所述半导体衬底的材料为si、ge、si

x

ge

1-x

、sic、gaas、lnp、 ln

x

ga

1-x

p、ln

x

ga

1-x

as、cdte、an、gan、inn或al

x

lnyga

1-x-y

n的任一种,其中x 和y满足的条件为:0≤x≤1,0≤y≤1,0≤x+y≤1。

23.进一步,所述功能层包括:直接在半导体衬底上表面制备的半导体电子器件,或在半导体衬底上表面外延生长出的半导体外延层,或在半导体衬底上表面外延生长出的半导体外延层以及在半导体外延层上制备的半导体电子器件。

24.进一步,所述半导体外延层所含成分包括si、ge、si

x

ge

1-x

、sic、gaas、 lnp、ln

x

ga

1-x

p、ln

x

ga

1-x

as、cdte、an、gan、inn和al

x

lnyga

1-x-y

n的至少一种,其中x和y满足的条件为:0≤x≤1,0≤y≤1,0≤x+y≤1。

25.进一步,所述半导体外延层包括al

x

lnyga

1-x-y

n时,x和y可以在外延层中渐变或突变。

26.进一步,所述半导体外延层的外延方法包括化学气相沉积、等离子体增强化学气相沉积、金属有机化学气相沉积、分子束外延、氢化物气相外延、物理气相传输和液相外延。

27.进一步,在半导体衬底表面注入的离子包括由h、he、ar和ne的至少一种元素形成的离子或由该元素形成的气体产生的离子。

28.进一步,所述步骤2)还包括:在所述功能层上制作应力导入层,应力导入层中存在张应力,应力导入层在功能层中产生压应力。

29.进一步,所述应力导入层采用金属材料,所述金属材料为ni、au、cu、 pd、ag、al、sn、cr、ti、mn、co、zn、mo、w、zr、v、ir、pt和fe的至少一种。

30.进一步,所述应力导入层可以采用非金属高分子材料。

31.进一步,当所述应力导入层为金属材料时,所述应力导入层作为功能层上电子器件的欧姆接触层或肖特基接触层使用。

32.进一步,在所述应力导入层上制作刚性或柔性的支撑层。

33.进一步,在所述功能层上制作刚性或柔性的支撑层。

附图说明

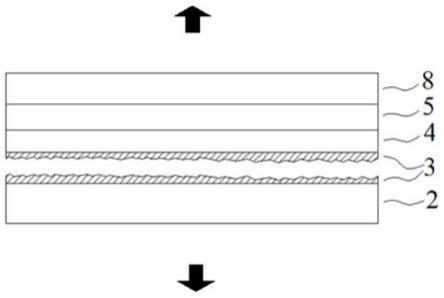

34.图1为本发明的半导体衬底结构的主视示意图;

35.图2为本发明的离子经半导体衬底上表面注入半导体衬底的示意图;

36.图3为本发明半导体衬底经离子注入后产生离子损伤层的结构示意图;

37.图4为在图3的半导体衬底表面产生外延层的结构示意图;

38.图5为一外延层的结构示意图;

39.图6为在图4的外延层上制备应力导入层的结构示意图;

40.图7为在图6的应力导入层上制备操作层的结构示意图;

41.图8为在图4的外延层上直接粘接刚性衬底并产生分离的结构示意图。

42.附图中,各标号所代表的部件列表如下:

43.1、半导体衬底层;2、半导体衬底主体层;3、离子损伤层;4、衬底薄膜层;5、半导体外延层;51、第一外延层;52、第二外延层;53、第三外延层;54、第四外延层;6、应力导入层;

7、操作层;8、刚性衬底。

具体实施方式

44.以下结合附图对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

45.图1和图2显示的是半导体衬底层1,图3是经离子注入后的半导体衬底层1,半导体衬底层被分成半导体衬底主体层2、离子损伤层3、以及位于离子损伤层3上的衬底薄膜层4。半导体衬底可以采用半导体单晶片、也可采用半导体单晶片以及在半导体单晶片上外延生长出半导体外延层,也可以采用在非半导体以及在氧化物单晶片上外延出半导体外延层,离子从半导体衬底层的表面注入。在半导体衬底层表面注入的离子包括由h、he、ar和ne 的至少一种元素形成的离子或由该元素形成的气体产生的离子。

46.实施方式一:在半导体衬底层1上表面进行离子注入,离子注入深度为 0.1μm-100μm,优选5μm、10μm、15μm和20μm;离子注入后在半导体衬底层1表面下产生一层离子损伤层3;然后可在衬底薄膜层4上直接制备功能层,本实施例的功能层为半导体电子器件,如制备mos、mosfet器件等。可以在半导体电子器件上直接粘接刚性衬底8,刚性衬底可以是半导体、氧化物晶体、金属、玻璃或陶瓷材料,并用向外的拉力将半导体衬底主体层和衬底薄膜层在离子损伤层处分离,此时,分离所需拉力与有应力导入层时所需的拉力相比要大的多。本实施例在分离前,功能层可以是在衬底薄膜层4 上未完成制备的半导体电子器件,将半导体衬底在离子损伤层处分离后,再在衬底薄膜层4上完成剩余的半导体电子器件的制作。

47.实施方式二:在半导体衬底层1上表面进行离子注入,离子注入深度为0.5μm-50μm,优选5μm、10μm、15μm和20μm;离子注入后在半导体衬底层1表面下产生一层离子损伤层3;在衬底薄膜层4的离子注入表面制备功能层,本实施例的功能层为在半导体衬底层1上表面外延生长出的半导体外延层5,也可以是在半导体衬底层1上表面外延生长出的半导体外延层5 以及在半导体外延层5上制备的半导体电子器件。半导体外延层5的外延方法包括化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、金属有机化学气相沉积(mocvd)、分子束外延(mbe)、氢化物气相外延(hvpe)、物理气相传输(pvt)和液相外延(lpe)。

48.半导体外延层5可以是单一的外延层结构,也可以是一层以上的外延结构,外延层可经由掺杂改变电导率和导电类型,如p、n型。如图5所示,半导体外延层5可以包括第一外延层51、第二外延层52、第三外延层53和第四外延层54。以制作led外延层结构为例,第一外延层为aln,第二外延层为n型gan,第三外延层为多层量子阱in

x

ga

(1-x)

n与势垒gan,第四外延层为p型gan,其中0≤x≤1,本实施例只是给出了外延层的一种应用,外延层的结构不限于此。

49.如图6所示,在半导体外延层5上制作应力导入层6,应力导入层本身受到张应力。应力导入层6由蒸镀、溅射、电镀、涂覆、旋涂方法制作;应力导入层可以采用金属材料,所述金属材料为ni、au、cu、pd、ag、al、sn、 cr、ti、mn、co、zn、mo、w、zr、v、ir、pt和fe的至少一种;应力导入层的作用是在功能层中产生压应力以利于半导体衬底主体层和衬底薄膜层的剥离。应力导入层也可以采用非金属高分子材料,所述非金属高分子材料为环氧基树脂(epoxy),环氧树脂作为应力导入层在150℃时烘干,利用功能层与应力导入层在冷却时因热澎涨系数不同产生的应力分离功能层。或环氧树脂作为应力导入层在室温干糙后,降低

温度至液氮温度分离。当应力导入层为金属材料时,可作为功能层上电子器件的欧姆接触层或肖特基(schottky)接触层使用,如在led结构外延层的p-gan上的应力导入层可作为欧姆电级使用,sic二极管n型外延层上的应力导入层可作为肖特基 (schottky)接触层使用。

50.如图7所示,在应力导入层6上制备操作层7,操作层7是为了分离时操作方便,可以采用胶带、聚合物等。操作层也可以采用刚性操作层,刚性操作层如半导体、氧化物、金属、玻璃或陶瓷材料。操作层非必需,当应力导入层足够厚时,不需要制作操作层。如图8所示,可以在功能层上直接粘接刚性衬底8,并用向外的拉力分离,图8中的箭头方向为拉力方向。

51.本实施例的半导体衬底材料采用碳化硅,以2吋(0001)晶向6h晶型碳化硅衬底为例,在碳化硅半导体衬底表面以7

°

倾斜角度注入氢离子,氢离子的注入能量为400kev,氢离子的注入剂量为5

×

10

16

cm-2

,氢离子注入后在半导体衬底下表面生成离子损伤层,如图3所示;离子注入完成后,一个适当的温度退火过程能够强化离子在损伤层内造成的损伤效果,对不同的衬底材料,退火温度不同,对si衬底而言,其退火温度需要在218℃以上,对sic衬底而言,退火温度需在650℃以上;退火过程也可以发生在制作功能层的过程中,离子注入的剂量需与注入离子的能量结合应用,无离子气泡造成的表面破坏和无薄膜层的自发分离是确保本专利技术成功实施的基本条件。经离子注入后的碳化硅半导体材料衬底置于mocvd反应器中外延生长半导体外延层(功能层),如图5所示,半导体外延层从下至上依次包括aln 缓冲层、si掺杂的n型gan层,多层量子阱in

x

ga

(1-x)

n与势垒gan、mg掺杂的p型gan层,整个外延层的厚度为4μm。然后在外延层上溅射一层10μm 厚的ni金属应力导入层,再在ni金属应力导入层上化学电镀了200μm-300 μm铜作为进一步支撑层兼应力导入层,从而使半导体衬底主体层2与衬底薄膜层4及其上功能层产生分离,分离后的半导体衬底主体层经抛光后可重复使用。

52.本实施例的半导体衬底材料采用碳化硅,以2吋(0001)晶向6h晶型碳化硅衬底为例,在碳化硅半导体衬底表面以7

°

倾斜角度注入氢离子,氢离子的注入能量为500kev,氢离子的注入剂量为7

×

10

16

cm-2

,氢离子注入后在半导体衬底层下表面生成离子损伤层,如图3所示。经离子注入后的碳化硅半导体材料衬底置于mocvd反应器中外延生长半导体外延层(功能层),如图4所示,半导体外延层从下至上依次包括aln缓冲层、si掺杂的n型 gan层,多层量子阱in

x

ga

(1-x)

n与势垒gan、mg掺杂的p型gan层,整个半导体外延层的厚度为4μm。在半导体外延层上直接粘接硅衬底,将碳化硅衬底和硅衬底分别吸附在两个真空吸盘上,在两个真空吸盘上施加向外的机械力,功能层和半导体衬底层与半导体衬底主体层在离子损伤层处分离。

53.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

54.本技术还可以如下配置:

55.项1.一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,包括以下步骤:

56.步骤1):在半导体衬底上表面进行离子注入,离子注入深度为0.1导体衬底上表面进,离子注入后在半导体衬底表面下产生一层离子损伤层;

57.步骤2):在经步骤1)处理后的半导体衬底上表面制备功能层;

58.步骤3):将半导体衬底及其上的功能层在离子损伤层处进行分离。

59.项2.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述半导体衬底包括:半导体单晶片,或半导体单晶片以及在半导体单晶片上外延生长出的半导体外延层,或在氧化物单晶片上外延生长出的半导体外延层。

60.项3.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述半导体衬底的材料为si、ge、si

x

ge

1-x

、sic、gaas、 lnp、ln

x

ga

1-x

p、ln

x

ga

1-x

as、cdte、aln、gan、inn或al

x

lnyga

1-x-y

n的任一种,其中x和y满足的条件为:0≤x≤1,0≤y≤1,0≤x+y≤1。

61.项4.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述功能层包括:直接在半导体衬底上表面制备的半导体电子器件,或在半导体衬底上表面外延生长出的半导体外延层,或在半导体衬底上表面外延生长出的半导体外延层以及在半导体外延层上制备的半导体电子器件。

62.项5.根据项4所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述半导体外延层所含成分包括si、ge、si

x

ge

1-x

、sic、 gaas、lnp、ln

x

ga

1-x

p、ln

x

ga

1-x

as、cdte、aln、gan、inn和al

x

lnyga

1-x-y

n的至少一种,其中x和y满足的条件为:0≤x≤1,0≤y≤1,0≤x+y≤1。

63.项6.根据项5所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述半导体外延层包括al

x

lnyga

1-x-y

n时,x和y可在外延层中渐变或突变。

64.项7.根据项2或4所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述半导体外延层的外延方法包括化学气相沉积、等离子体增强化学气相沉积、金属有机化学气相沉积、分子束外延、氢化物气相外延、物理气相传输和液相外延。

65.项8.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,在半导体衬底表面注入的离子包括由h、he、ar和ne的至少一种元素形成的离子或由该元素形成的气体产生的离子。

66.项9.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述步骤2)还包括:在所述功能层上制作应力导入层,应力导入层中存在张应力,应力导入层在功能层中产生压应力。

67.项10.根据项9所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述应力导入层采用金属材料,所述金属材料为ni、au、 cu、pd、ag、al、sn、cr、ti、mn、co、zn、mo、w、zr、v、ir、pt和fe 的至少一种。

68.项11.根据项9所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,所述应力导入层采用非金属高分子材料。

69.项12.根据项9或10所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,当所述应力导入层为金属材料时,所述应力导入层作为功能层上电子器件的欧姆接触层或肖特基接触层使用。

70.项13.根据项9或10所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,在所述应力导入层上制作刚性或柔性的支撑层。

71.项14.根据项1所述一种将半导体衬底主体与其上功能层进行分离的方法,其特征在于,在所述功能层上制作刚性或柔性的支撑层。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1