一种显示面板及显示装置的制作方法

1.本发明涉及显示技术领域,尤其涉及一种显示面板及显示装置。

背景技术:

2.随着液晶显示技术的不断发展,有机发光显示(organic light-emitting diode,oled)面板或者液晶显示面板等,已被大量地应用在手机、平板电脑等电子终端中,以实现轻薄化、高质量显示效果等。

3.显示面板的用于进行图像显示的显示区周围设置有非显示区,用于排布驱动芯片或制作垂直移位寄存器(vertical shift register,vsr),因为vsr器件多、结构复杂、占用空间大,因此非显示区域一般要预留出较大的空间。

4.为了适应现代窄边框设计,一般压缩非显示区的面积,需要压缩非显示区的其他部件的尺寸,容易超过目前工程极限,影响其他部件的性能,例如,对于低温多晶硅(low temperature poly-silicon,ltps)面板,需要压缩封装部分和狭缝(slit)区,容易出现封装失效或裂纹的风险。

技术实现要素:

5.本发明实施例提供了一种显示面板及显示装置,以在提高显示面板可靠性的同时,实现显示面板窄边框设计。

6.第一方面,本发明实施例提供了一种显示面板,包括:衬底;

7.驱动电路层,设置于所述衬底一侧;

8.发光元件,设置于所述驱动电路层远离所述衬底的一侧;

9.所述显示面板包括显示区和至少部分围绕所述显示区的非显示区;所述发光元件位于所述显示区;所述驱动电路层包括移位寄存电路;所述移位寄存电路位于所述非显示区;

10.至少一个挡墙;所述挡墙设置于所述非显示区且围绕所述显示区设置;

11.所述移位寄存电路包括第一电路结构和第二电路结构;在平行于所述衬底所在平面内,所述第二电路结构的投影与所述挡墙至少部分交叠;所述第一电路结构位于所述第二电路结构靠近所述显示区的一侧。

12.第二方面,本发明实施例提供了一种显示装置,包括本发明任意实施例提供的显示面板。

13.本发明中,显示面板包括衬底上依次设置的驱动电路层和发光元件;发光元件设置于显示区,驱动电路层中设置有移位寄存电路,移位寄存电路设置在非显示区,非显示区还设置有至少一个挡墙,挡墙围绕显示区设置,移位寄存电路包括第一电路结构和第二电路结构,第一电路结构设置于第二电路结构和显示区之间,并且第二电路结构在衬底上的垂直投影与挡墙至少部分交叠。本实施例将占用面积较大的移位寄存电路分为两部分,并将其中一部分,也即,第二电路结构与挡墙形成交叠区域,相对于现有技术中挡墙设置在移

位寄存器电路外侧的设计,可缩短非显示区的宽度,有利于显示屏的窄边框设计,此外,当面板需要设置多组移位寄存器,移位寄存电路占用空间更大时,本实施例将第二电路结构与挡墙投影交叠,不需要通过压缩封装等方式压缩边框宽度,有效避免显示面板封装失效或裂纹的风险,提高面板可靠性。

附图说明

14.图1为本发明实施例提供的一种显示面板的结构示意图;

15.图2为本发明实施例提供的另一种显示面板的结构示意图;

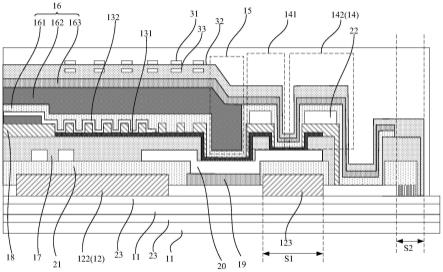

16.图3为图1中显示面板沿线端a-a’的剖面示意图;

17.图4为图2中显示面板沿线端b-b’的剖面示意图;

18.图5为本发明实施例提供的一种移位寄存电路的结构示意图;

19.图6为本发明实施例提供的另一种移位寄存电路的结构示意图;

20.图7为图1中显示面板沿线端c-c’的一种剖面示意图;

21.图8为图1中显示面板沿线端c-c’的另一种剖面示意图;

22.图9为图1中显示面板沿线端c-c’的另一种剖面示意图;

23.图10为图1中显示面板沿线端c-c’的另一种剖面示意图;

24.图11为本发明实施例提供的一种显示装置的结构示意图。

具体实施方式

25.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

26.现有技术中,为了实现客户要求的边框设计,可能会通过压缩边框的其他结构实现,这样会导致显示面板的其他性能受影响,容易超过工程极限,出现封装乃至面板失效的问题。本发明实施例通过改善移位寄存电路的设计,有效缩短窄边框设计,并且相对于具有较大使用前景的低温多晶氧化物(low temperature polycrystalline oxide,ltpo)面板,因其需要同时用到三组vsr电路,同时输入到显示面板的子像素中,相比于低温多晶硅(low temperature poly-silicon,ltps)面板,多出一组vsr电路,在不改变设计的前提下,压缩边框容易影响其他部件的性能,本发明实施例改变vsr电路设计,不需要压缩封装和slit区等,在维持客户要求的边框宽度的同时,保证显示面板性能。

27.本发明实施例提供了一种显示面板,包括:衬底;

28.驱动电路层,设置于衬底一侧;

29.发光元件,设置于驱动电路层远离衬底的一侧;

30.显示面板包括显示区和至少部分围绕显示区的非显示区;发光元件位于显示区;驱动电路层包括移位寄存电路;移位寄存电路位于非显示区;

31.至少一个挡墙;挡墙设置于非显示区且围绕显示区设置;

32.移位寄存电路包括第一电路结构和第二电路结构;在平行于衬底所在平面内,第二电路结构的投影与挡墙至少部分交叠;第一电路结构位于第二电路结构靠近显示区的一侧。

33.本发明实施例中,显示面板包括衬底上依次设置的驱动电路层和发光元件;发光元件设置于显示区,驱动电路层中设置有移位寄存电路,移位寄存电路设置在非显示区,非显示区还设置有至少一个挡墙,挡墙围绕显示区设置,移位寄存电路包括第一电路结构和第二电路结构,第一电路结构设置于第二电路结构和显示区之间,并且第二电路结构在衬底上的垂直投影与挡墙至少部分交叠。本实施例将占用面积较大的移位寄存电路分为两部分,并将其中一部分,也即,第二电路结构与挡墙形成交叠区域,相对于现有技术中挡墙设置在移位寄存器电路外侧的设计,可缩短非显示区的宽度,有利于显示屏的窄边框设计,此外,当面板需要设置多组移位寄存器,移位寄存电路占用空间更大时,本实施例将第二电路结构与挡墙投影交叠,不需要通过压缩封装等方式压缩边框宽度,有效避免显示面板封装失效或裂纹的风险,提高面板可靠性。

34.以上是本发明的核心思想,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下,所获得的所有其他实施例,都属于本发明保护的范围。

35.图1为本发明实施例提供的一种显示面板的结构示意图,图2为本发明实施例提供的另一种显示面板的结构示意图,图3为图1中显示面板沿线端a-a’的剖面示意图,图4为图2中显示面板沿线端b-b’的剖面示意图,如图1和图3所示,显示面板1包括衬底11,以及依次设置于衬底11上的驱动电路层12和发光元件13,显示面板包括显示区aa和至少部分围绕显示区aa的非显示区na。需要说明的是,为了对非显示区na的器件进行描述,图1中放大了非显示区na在整个显示面板上的比例,图1中显示区aa和非显示区na的比例不代表其在实物中的比例。发光元件13位于显示区aa中,驱动电路层12可以设置有与发光元件13一一对应的像素驱动电路(图1中未示出),像素驱动电路能够为发光元件13提供驱动电压,从而驱动发光元件13发光显示。参考图3,驱动电路层12还设置有移位寄存电路121,移位寄存电路121用于产生像素驱动电路所需要的控制信号,实现对发光元件13的扫描,移位寄存电路121设置于非显示区na,并与显示区aa的像素驱动电路电连接。

36.显示面板还包括挡墙14,挡墙14设置于非显示区na,且围绕显示区aa设置,本实施例中,可设置至少一个挡墙14,例如,如图1所示,本实施例可以设置两个挡墙14,以提高显示面板的强度和可靠性。移位寄存电路121包括第一电路结构122和第二电路结构123,也即,本实施例将移位寄存电路121分为两部分,其中一部分(第一电路结构122)设置在显示区aa和另一部分(第二电路结构123)之间,并且在平行于衬底11所在平面内,第二电路结构123与挡墙14至少部分交叠,则在平行于衬底11的平面内,第二电路结构123的设置,使得移位寄存电路121与挡墙14之间存在共享区域s1,进而整个边框的宽度减小,而现有结构中,常常在移位寄存电路的外侧设置挡墙,也即,移位寄存电路和挡墙在平行于衬底11的平面上没有共享区域。本案相对于现有结构的实际,从移位寄存电路121的设计上,有效复用非显示区na的横向空间,实现显示面板的窄边框设计,不需要压缩非显示区na中的其他结构的设计,例如,不需要缩短狭缝区s2的设置宽度,从而避免在切割或搬运显示面板时产生裂纹,提高显示面板可靠性。可选的,如图1所示,挡墙14可以包括多个挡墙段,每个挡墙14的多个挡墙段围绕显示区aa一周设置,或者,如图2所示,挡墙14为围绕显示区aa的封闭图形。此外,挡墙14在衬底上的投影还可以为围绕显示区aa曲形,本实施例对挡墙14的具体形状不进行特殊限定。

37.继续参考图3,可选的,显示面板还可以包括:封装层16;封装层16设置于发光元件13远离衬底11的一侧;封装层16包括依次远离衬底11设置的第一无机层161、第一有机层162和第二无机层163;显示面板的非显示区na设置有谷部区域15;谷部区域15内第一有机层162的厚度大于显示区aa中第一有机层162的厚度;谷部区域15围绕显示区aa设置;挡墙14围绕谷部区域15设置;在平行于衬底11所在平面内,第二电路结构123的投影与谷部区域15至少部分交叠。

38.封装层16设置于发光元件13的显示侧,用于对发光元件13以及发光元件13之下的像素驱动电路进行保护。具体的封装层16包括依次远离衬底11的第一无机层161、第一有机层162和第二无机层163,上述有机层和无机层的交叠设置,既能够有效防止水氧入侵至显示面板,又能够提高显示面板的强度。本实施例中,挡墙14可以设置一个或者多个,用于阻挡显示区aa内材料在制作过程中的外溢,并且为了进一步增至外溢情况,在非显示区na处形成凹槽,也即,谷部区域15,谷部区域15为显示面板的部分膜层挖槽形成,封装层16的第一有机层162采用喷墨打印的方式形成,因此第一有机层162在制作过程中溢流入谷部区域15,使得第一有机层162在谷部区域15的厚度,大于其在显示区aa内的厚度。谷部区域15同样围绕显示区aa设计,并且谷部区域15设置于显示区aa和挡墙14之间。在本实施例中,第二电路结构123在衬底11上的垂直投影与谷部区域15存在交叠,如图3所示,第二电路结构123和谷部区域15在平行于衬底11的平面上存在共享区域s3,本实施例中,第二电路结构123在平行于衬底11的平面内,同谷部区域15和挡墙14均存在共享区域,进一步提高了边框区域的复用率,有利于进一步降低显示面板的边框,提升用户使用体验。并且,在上述基础上,可将非显示区na内其他结构进行横向空间复用,便于非显示区空间的进一步缩减,并有利于在非显示区na设计更多的功能电路,实现更多的面板功能。

39.继续参考图3,可选的,在平行于衬底11所在平面内,第一有机层162延伸至覆盖谷部区域15,第一无机层161和第二无机层163延伸至覆盖挡墙14。

40.第一无机层161和第二无机层163均能够覆盖谷部区域15延伸至覆盖所有的挡墙14,以防止外界杂质进入面板,第一有机层162延伸至覆盖谷部区域15,并且谷部区域15能够存储溢流的有机材料,防止外溢,从而避免封装层16封装不彻底的问题。在本实施例中,因为第二电路结构123在衬底11上的垂直投影与谷部区域15至少部分交叠,则第一有机层162能够覆盖第二电路结构123,第一有机层162可有效保护第二电路结构123,能够避免第二电路结构123在磕碰状态下发生损坏,从而提高显示面板整体质量。

41.继续参考图3,可选的,显示面板还可以包括:平坦化层17,设置于驱动电路层12和发光元件13之间;发光元件13包括依次远离衬底11的阳极层131、发光层和阴极层132;像素限定层18,设置于阳极层131远离衬底11的一侧;发光层设置于像素限定层18远离衬底11的一侧;在平行于衬底11的平面内,平坦化层17的投影与谷部区域15不重叠。

42.如图3所示,显示面板的驱动电路层12的上方还依次形成有平坦化层17和像素限定层18,其中,平坦化层17设置于驱动电路层12和发光元件13之间,发光元件13包括依次远离衬底11的阳极层131、发光层(图3中未示出)和阴极层132,像素限定层18设置于阳极层131和发光层之间,用于限定发光层中发光材料的位置。上述谷部区域15可由挖取像素限定层18和平坦化层17形成,当然谷部区域15可以为仅挖取平坦化层17形成,因为平坦化层17为有机材料制成,有机材料的密封效果不够,所以将谷部区域15内的有机材料挖去,使得谷

部区域15内与封装层16的第一无机层161接触的膜层不为有机层,从而有效隔绝水氧,提升显示面板的封装效果。与之对比,谷部区域15外侧的挡墙14由平坦化层17和像素限定层18等堆叠形成,此外,还可以在像素限定层18上堆叠有机材料层22等,例如,聚苯乙烯ps,以提高挡墙14的高度,并且有机材料具有一定的韧性和抗应力开裂性能,有效对显示面板进行保护。

43.如图2和图4所示,可选的,挡墙14至少可以包括第一挡墙141和第二挡墙142;第一挡墙141位于显示区aa和第二挡墙142之间;第一挡墙141和第二挡墙142的投影覆盖至少部分覆盖第二电路结构123。

44.如图4所示,显示面板的挡墙14至少设置两个,也即,第一挡墙141和第二挡墙142。相对于图3所示的显示面板,本实施例可将第二电路结构123的位置做出一定的调整,也即,将第二电路结构123设置于第一挡墙141和第二挡墙142之间的位置,且第二电路结构123在衬底11上的垂直投影与第一挡墙141和第二挡墙142至少部分交叠,如图4所示,第一挡墙141靠近显示区aa中的边缘和第二挡墙142远离显示区aa的边缘围成的区域覆盖第二电路结构123的投影,则本实施例充分利用了第一挡墙141和第二挡墙142的空间设置上述第二电路结构123,相当于在平行于衬底11的平面内,不需要另外增加空间设置第二电路结构123,第一挡墙141和第二挡墙142形成的区域完全覆盖第二电路结构123的区域,进一步降低显示面板的边框宽度,且能够保证显示面板本身的可靠性。此外,因为形成挡墙14的膜材包含有大量的有机膜层,对第二电路结构123起到良好的保护作用,提高显示面板的抗撞性能。

45.继续参考图4,可选的,显示面板还可以包括:封装层16;封装层16位于发光元件13远离衬底11的一侧;封装层16包括依次远离衬底11设置的第一无机层161、第一有机层162和第二无机层163;在平行于衬底11所在平面内,第一有机层162延伸至覆盖第一电路结构122,第一无机层161和第二无机层163延伸至覆盖挡墙14。

46.由上述实施例可知,封装层16中的第一有机层162和第二无机层163延伸至覆盖所有的挡墙14,第一有机层162延伸至覆盖谷部区域15,则第一有机层162在衬底11上的垂直投影覆盖第一电路结构122,有利于对第一电路结构122进行保护,第一无机层161和第二无机层163在衬底11上的垂直投影覆盖第一电路结构122和第二电路结构123,能够对第一电路结构122和第二电路结构123进行保护,提高移位寄存电路121的可靠性,进而提高整个显示面板的可靠性。

47.继续参考图3和图4,在封装层16远离衬底11的一侧还以设置有触控电极31,以实现显示面板的触控功能。本实施例中触控电极31可分两层设置,实现互容式触控检测,当然,也可以如图3和图4所示,触控电极31设置于同一金属层,触控走线33设置于另一金属层,触控走线33穿过触控绝缘层32与对应触控电极31电连接。

48.继续参考图3和图4,可选的,移位寄存电路121可以包括两个移位寄存器:第一移位寄存器和第二移位寄存器;第一移位寄存器的输出端输出扫描信号至驱动电路层12中的像素驱动电路;第二移位寄存器的输出端输出发光控制信号至驱动电路层12中的像素驱动电路;第一移位寄存器和第二移位寄存器中的一个移位寄存器设置于第一电路结构122,另一个移位寄存器设置于第二电路结构123。

49.本实施例中,显示面板可以包括两个移位寄存器,例如,对于ltps面板,其需要设

置两个移位寄存器,本实施例称之为第一移位寄存器和第二移位寄存器,其中,第一移位寄存器用于产生像素驱动电路的扫描线号scan,第二移位寄存器用于产生像素驱动电路需要的发光控制信号emit。本实施例中,可将上述两个移位寄存器中一者设置于第一电路结构122,另一者设置于第二电路结构123。则相对于两个移位寄存器设置于一处,占用较大非显示区空间的方案,本实施例,将部分移位寄存电路121移动至与挡墙14复用横向空间,有利于显示面板的窄边框设计,且不需要压缩其他部件的空间。

50.继续参考图3和图4,可选的,移位寄存电路121可以包括三个移位寄存器:第三移位寄存器、第四移位寄存器和第五移位寄存器;第三移位寄存器的输出端输出p型薄膜晶体管的扫描信号至驱动电路层12中的像素驱动电路;第四移位寄存器的输出端输出n型薄膜晶体管的扫描信号至驱动电路层12中的像素驱动电路;第五移位寄存器的输出端输出发光控制信号至驱动电路层12中的像素驱动电路;第三移位寄存器、第四移位寄存器和第五移位寄存器中的一个移位寄存器设置于第二电路结构123,另两个移位寄存器设置于第一电路结构122。

51.显示面板还可以包括三个或三个以上的移位寄存器,例如,对于ltpo面板,因其像素驱动电路中同时设置有p型薄膜晶体管和n型薄膜晶体管,上述两种薄膜晶体管所需扫描信号scan的时序不同,不能应用同一个移位寄存器。本实施例中,可以包括第三移位寄存器、第四移位寄存器和第五移位寄存器,则第三移位寄存器用于输出p型薄膜晶体管的扫描信号,第四移位寄存器用于输出n型薄膜晶体管的扫描信号,第五移位寄存器用于输出发光控制信号。并且,上述三个移位寄存器中的一个移位寄存器设置于第二电路结构123,剩余的设置于第一电路结构122。同样将部分移位寄存电路121移动至与挡墙14复用横向空间,有利于显示面板的窄边框设计,且不需要压缩其他部件的空间。相对于现有的ltpo面板的压缩封装层16和狭缝区s2的设置,可靠性较强,且边框更窄。

52.图5为本发明实施例提供的一种移位寄存电路的结构示意图,可选的,移位寄存电路121至少可以包括两个移位寄存器;每个移位寄存器均包括:电位控制模块121a和输出模块121b;电位控制模块121a用于根据第一时钟信号ck、第二时钟信号xck和扫描触发信号stv,控制第一节点n2的信号与第二节点n4的信号的电平相反;输出模块121b用于在第一节点n1的信号的控制下,将第一电压信号vgh传输至移位寄存器的输出端out,或者在第二节点n4的信号的控制下,将第二电压信号vgl传输至移位寄存器的输出端out;移位寄存器的输出模块121b设置于第二电路结构123;移位寄存器的电位控制模块121a设置于第一电路结构122。

53.如图5所示,无论是形成扫描信号的移位寄存器还是形成发光控制信号的移位寄存器,无论是形成p型薄膜晶体管的扫描信号的移位寄存器,还是形成n型薄膜晶体管的扫描信号的移位寄存器,其均包括电位控制模块121a和输出模块121b。其中,电位控制模块121a能够在第一时钟信号ck、第二时钟信号xck和扫描触发信号stv的控制下,将第一电压信号vgh传输至第一节点n2,并由输出模块121b传输至输出端out,也能够在第一时钟信号ck、第二时钟信号xck和扫描触发信号stv的控制下,将第二电压信号vgl传输至第二节点n4,并由输出模块121b传输至输出端out,第一电压信号vgh可以为高电平,第二电压信号vgl可以为低电平,则输出端out输出的信号实现高低电平转换,形成扫描信号或发光控制信号。输出模块121b的输出端out输出的信号是用于控制像素驱动电路的,并且需要控制一

整行的像素驱动电路,则输出模块121b内器件要大于电位控制模块121a,以输出较大的信号。如图5所示,输出模块121b可以包括第一输出管m7和第二输出管m8,第一输出管m7和第二输出管m8的沟道宽长比较大,受外界干扰信号的影响较小,本实施例将所有移位寄存器的输出模块121b设置于第二电路结构123,电位控制模块121a设置于第一电路结构122,既能够将移位寄存电路121与挡墙14共享横向空间,降低显示面板边框,又能够将外界信号对移位寄存电路的影响降到最低,提高移位寄存电路的可靠性。

54.示例性的,如图6所示,图6为本发明实施例提供的另一种移位寄存电路的结构示意图,图6示出了用于输出扫描信号的移位寄存电路的具体结构,电位控制模块121a包括第一开关管m1、第二开关管m2、第三开关管m3、第四开关管m4、第四开关管m5和第五开关管m6,其中第五开关管m6用于接入第一电压信号vgh,第四开关管m5用于接入扫描触发信号stv,第一开关管m1、第二开关管m2和第三开关管m3形成互锁结构,从而使n2节点和n1节点的电位相互钳制,避免第一输出管m7和第二输出管m8分别输出不同的电位信号,造成信号混乱。由此可知,电位控制模块121a内开关管仅起到电位控制作用,与输出管作用不同,本实施例据此对电位控制模块121a和输出模块121b分为两部分设置,以降低外界环境对电位控制模块121a,乃至整个移位寄存电路的影响。

55.可选的,第一电路结构122和第二电路结构123通过p型薄膜晶体管的栅极层、n型薄膜晶体管的栅极层或第一电容极板电连接。第一电路结构122和第二电路结构123之间可通过驱动电路层12中的至少一层金属层建立电连接。优选的,本实施例可通过p型薄膜晶体管的栅极层、n型薄膜晶体管的栅极层或第一电容极板电连接,上述各层金属层的电阻较小,且布线简单,形成连接第一电路结构122和第二电路结构123的连接线的工艺风险小,从而提高移位寄存电路的可靠性。

56.继续参考图4,可选的,显示面板还可以包括:第一金属层19;设置于驱动电路层12远离衬底11的一侧;第一金属层19设置有阴极电源线;阴极电源线设置于第一电路结构122和第二电路结构123之间;第二金属层20,设置于第一金属层19远离衬底11的一侧;发光元件13包括依次远离衬底11设置的阳极层131、发光层和阴极层132;阴极电源线通过第二金属层20和阳极层131搭接至阴极层132;在平行于衬底11所在平面内,搭接阴极电源线的第二金属层20的投影覆盖阴极电源线;且搭接阴极电源线的第二金属层20的投影与第一电路结构122至少部分交叠,搭接阴极电源线的第二金属层20的投影与第二电路结构123至少部分交叠。

57.在驱动电路层12远离衬底11的一侧,还依次设置有第一金属层19和第二金属层20,第一金属层19可形成有阴极电源线,本实施例中,阴极电源线设置于第一电路结构122和第二电路结构123之间,如图4所示,阴极电源线与谷部区域15在衬底11所在平面上可存在交叠区域,相对于将阴极电源线设置在谷部区域15靠近显示区aa一侧的方案,本实施例中阴极电源线有效增宽,降低电阻值。

58.第二金属层20设置于第一金属层19上方,并与第一金属层19搭接,第二金属层20在衬底11上的垂直投影可覆盖阴极电源线,相当于进一步增宽阴极电源线的设置,有效降低阴极电源线的电阻值。本实施例中,发光元件13可以包括依次远离衬底11设置的阳极层131、发光层和阴极层132,使得阴极电源线依次通过第二金属层20、阳极层131与阴极层132在非显示区na搭接,实现阴极电源线为阴极层132提供阴极电源信号。

59.此外,搭接阴极电源线的第二金属层20在衬底11上的垂直投影不仅覆盖阴极电源线,还覆盖第一电路结构122的至少部分结构,并覆盖第二电路结构123的至少部分结构,由此可知,搭接阴极电源线的第二金属层20的宽度较大,使得阴极电源线在传输阴极电源信号时具有更小的电压降。并且搭接阴极电源线的第二金属层20覆盖第一电路结构122和第二电路结构123的至少部分结构时,能够对第一电路结构122和第二电路结构123进一步增强保护,提高第一电路结构122和第二电路结构123的可靠性。

60.继续参考图3和图4,可选的,显示面板还可以包括:第二有机层21;第二有机层21设置于第二金属层20和驱动电路层12之间;第二有机层21用于实现第二金属层20和移位寄存电路121之间的绝缘。

61.本实施例中第二有机层21设置于第二金属层20和驱动电路层12之间,可实现第二金属层20和驱动电路层12之间的绝缘,如图3和图4所示,第二有机层21可实现第二金属层20和移位寄存电路121之间的绝缘。此外,第二有机层21的材料柔性高于无机材料,可进一步对移位寄存电路121进行保护,提高移位寄存电路121的可靠性,从而提高显示面板的可靠性。并且,第二有机层21在一定程度上可隔绝外界信号对移位寄存电路121的干扰,提高移位寄存电路121是对显示面板扫描的精准性。

62.在上述实施例的基础上,图7为图1中显示面板沿线端c-c’的一种剖面示意图,图8为图1中显示面板沿线端c-c’的另一种剖面示意图,图9为图1中显示面板沿线端c-c’的另一种剖面示意图,图10为图1中显示面板沿线端c-c’的另一种剖面示意图,图7至图10为第二电路结构123与谷部区域15存在交叠时,即图1和图3所示的情况时,谷部区域15的剖面示意图,图7至图9示出了在谷部区域15内,三种不同的第二金属层20和阳极层131的搭接状态,第二金属层20和阳极层131之间可包括多种不同的搭接状态,其搭接状态包括但不限于图7至图9示出的结构。此外,如图10所示,在某些谷部区域15,还可以未设置第二金属层20和阳极层131相搭接的结构,仅设置阳极层131。谷部区域15可包括多种膜层设计,但是本实施例中,所有的谷部区域15中与封装层16接触的膜层均不为有机层,因为封装层16需要隔绝水氧,若封装层16下接触的膜层为有机层,容易降低封装效果。本实施例中,与封装层16接触的膜层为第二金属层20和/或阳极层131,均能够保证显示面板的封装效果良好。可选的,衬底11还设置有缓冲层23,示例性的,本实施例在形成驱动电路层12之前,依次设置衬底11、缓冲层23、衬底11、缓冲层23的四层衬底结构。

63.本发明实施例还提供一种显示装置。图11为本发明实施例提供的一种显示装置的结构示意图,如图11所示,本发明实施例提供的显示装置包括本发明任意实施例所述的显示面板1。显示装置可以为如图11中所示的手机,也可以为电脑、电视机、智能穿戴设备等,本实施例对此不作特殊限定。

64.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1