用于半导体器件的像素单元及其制作方法、微显示屏与流程

1.本技术涉及半导体装置技术领域,尤其涉及用于半导体器件的像素单元及其制作方法、微显示屏。

背景技术:

2.micro led显示技术是指以自发光的微米量级的led为发光像素单元,将其组装到驱动面板上形成高密度led阵列的显示技术。由于micro led芯片尺寸小、集成度高和自发光等特点,在显示方面与lcd、oled相比在亮度、分辨率、对比度、能耗、使用寿命、响应速度和热稳定性等方面具有更大的优势。micro led应用将从平板显示扩展到ar/vr/mr、空间显示、柔性透明显示、可穿戴/可植入光电器件、光通信/光互联、医疗探测、智能车灯等诸多领域。为此,行业内技术人员在不断优化micro led显示技术。

3.micro led显示技术应用于上述领域时,通常有全彩色显示需求。已公开中国专利cn201880019435公开了一种通过堆叠微型led的层来制造半导体器件的方法,该半导体结构如图1所示,其为集成多色led显示面板的若干像素的截面图。根据图1可知,微型led140rgb被包含在堆叠在衬底和像素驱动器的顶部上的不同的层155r、155g、155b中。在一种实施方式中,底层155r包含红色微型led 140r,中间层155g包含绿色微型led140g,并且顶层155b包含蓝色微型led 140b。因此,该专利本质上为水平布局的rgb三色方案。

4.而本领域人员都应该知晓,水平布置的像素单元,有源区发光体占像素面积的占比极大地限制着发光体的尺寸,影响发光面积,同时micro-led器件具有尺寸效应:随着尺寸减小,外量子效率(eqe)急剧下降,特别是有源区直径下降至10um及以下时,下降极为剧烈。并且,有源区尺寸缩小时,在同电流密度情况下,有源区尺寸越小,eqe越低,当有源区尺寸在20um及更小尺寸时,eqe衰减更为严重。

5.因此,现有技术中所采用的像素水平阵列式布置或本质上位水平阵列式布置的堆叠方案,发光面积及外量子效率都不是很理想。

6.因此需要寻找一种能实现多色化显示且能有效增大有源区尺寸占比的像素单元。

7.申请内容

8.本技术的目的在于提供用于半导体器件的像素单元及其制作方法、微显示屏,其能实现有源区面积占比较大的多色化显示。

9.为实现上述申请目的,本技术第一方面提出用于半导体器件的像素单元,所述像素单元包括:

10.驱动背板,所述驱动背板设有驱动电路,所述驱动电路设有至少一个阳极;

11.显示单元,所述显示单元设于所述驱动背板上,所述显示单元包括自下而上依次堆叠设置的第一器件层及第二器件层,所述第一器件层、所述第二器件层分别与所述驱动背板的相应阳极连接;

12.共阴极,所述共阴极分别与所述显示单元中的每一器件层连接,所述共阴极与外部阴极连接。

13.优选的,所述共阴极包括共阴极本体、分别与所述共阴极本体连接的第一连接部及第二连接部,所述第一连接部与所述第一器件层连接,所述第二连接部与所述第二器件层连接。

14.优选的,所述驱动背板包括的至少两个阳极均匀布设,且所述至少两个阳极均位于所述显示单元在所述驱动背板的投影范围内。

15.优选的,所述驱动背板包括至少一个顶部金属,所述顶部金属覆盖至少一个阳极;或,

16.所述驱动背板包括设于其上表面的原位反射镜,所述原位反射镜覆盖或裸露至少一个所述阳极。

17.优选的,所述第一器件层包括第一键合层、第一化合物发光层及绝缘包裹层,所述第一化合物发光层贴设于所述第一键合层远离所述驱动背板的一侧表面,所述绝缘包裹层包裹所述第一键合层及所述第一化合物发光层。

18.优选的,所述第一键合层采用导电材料制成,所述驱动背板与所述第一键合层之间设有第一绝缘层;

19.所述第一绝缘层设有至少一个第一通孔,所述第一键合层穿过所述第一通孔与相应的第一阳极连接。

20.优选地,所述共阴极嵌设于所述显示单元内部;或,

21.所述共阴极本体为围设于所述显示单元周向的金属围框。

22.优选的,所述第一键合层采用绝缘材料制成;

23.所述第一化合物发光层包括朝向所述第一键合层所在一侧设置的第一p型欧姆接触层,所述第一p型欧姆接触层包括朝向所述共阴极延伸但不接触所述共阴极的第一p型欧姆接触层延伸部;

24.所述第一器件层还包括第一电气连接结构,所述第一电气连接结构一端与相应的第一阳极连接,自由端穿过所述第一键合层并与所述第一p型欧姆接触层延伸部连接。

25.优选地,所述共阴极本体为围设于所述显示单元周向的金属围框。

26.优选的,所述第一电气连接结构的自由端不超过所述第二器件层较近的一侧表面。

27.优选的,所述第一连接部与所述第一化合物发光层连接。

28.优选的,所述第一器件层还包括第一阴极欧姆接触,所述第一阴极欧姆接触贴设于所述第一化合物发光层远离所述第一键合层的一侧表面,所述第一连接部与所述第一阴极欧姆接触连接。

29.优选的,所述第二器件层包括第二键合层、第二化合物发光层及绝缘包裹层;所述第二化合物发光层贴设于所述第二键合层远离所述第一器件层的一侧表面,所述绝缘包裹层包裹所述第一键合层及所述第一化合物发光层。

30.优选的,所述第二键合层采用透明导电材料或透明半导体材料制成;

31.所述第二器件层还包括第二电气连接结构,所述第二电气连接结构一端与相应的第二阳极连接,另一端穿过所述第一器件层与所述第二键合层连接。

32.优选的,所述第二电气连接结构包括第一金属柱,所述第一金属柱一端与相应的第二阳极连接,另一端穿过所述第一器件层与所述第二键合层连接;或,

33.所述第二电气连接结构包括第一连接层及与所述第一连接层连接的第一金属柱,所述第一连接层穿过所述第一绝缘层与相应的第二阳极连接,所述第一金属柱与所述第二键合层连接。

34.优选的,所述第二键合层采用透明绝缘材料制成;

35.所述第二化合物发光层包括朝向所述第二键合层所在一侧设置的第二p型欧姆接触层,所述第二p型欧姆接触层包括朝向所述共阴极延伸但不接触所述共阴极的第二p型欧姆接触层延伸部;

36.所述第二器件层还包括第三电气连接结构,所述第三电气连接结构一端与相应的第二阳极连接,自由端穿过所述第一器件层并与所述第二p型欧姆接触层延伸部连接。

37.优选的,所述第一化合物发光层与所述第二化合物发光层采用的化合物发光材料相同,所述第一器件层与所述第二器件层与同一阳极连接,且所述第一器件层与所述第二器件层串联或并联设置。

38.优选的,所述显示单元还包括堆叠设于所述第二器件层远离所述第一器件层一侧的第三器件层;

39.所述第三器件层与所述驱动背板的第三阳极连接;

40.所述共阴极还包括与所述共阴极本体连接的第三连接部,所述第三连接部与所述第三器件层连接。

41.优选的,所述共阴极的厚度自靠近所述驱动背板的一端向另一端递减。

42.优选的,所述像素单元还包括光学增强结构,所述光学增强结构堆叠于所述像素单元远离所述驱动背板的一侧。

43.第二方面,本技术提供如第一方面任意一项所述用于半导体器件的像素单元的制作方法,其特征在于,所述制作方法包括:

44.制作驱动背板,所述驱动背板设有驱动电路,所述驱动电路设有至少一个阳极;

45.制作显示单元及相应的共阴极,将预先准备的第一化合物半导体与所述驱动背板键合,并构造第一器件层及与所述第一器件层对应的至少一侧面的第一共阴极;将预先准备的第二化合物半导体与所述第一器件层远离所述驱动背板一侧表面键合,并构造第二器件层及与所述第二器件层周向的至少一侧面的第二共阴极,将所述第二器件层分别与所述驱动背板的对应阳极及所述第二共阴极连接,所述第二共阴极与所述第一共阴极首尾连接形成共阴极,所述共阴极与外部阴极连接。

46.优选的,所述第一化合物半导体与所述驱动背板键合形成第一键合层采用导电材料,所述将预先准备的第一化合物半导体与所述驱动背板键合,包括:

47.在所述驱动背板设有至少两个阳极的表面整面镀绝缘材料,并开设与所述至少两个阳极对应的至少两个第一通孔;

48.在镀绝缘层后的所述驱动背板表面整面镀导电材料形成镀有键合材料的驱动背板;

49.在第一化合物半导体表面整面镀导电材料形成镀有键合材料的第一化合物半导体;

50.将分别镀有键合材料的所述驱动背板与所述第一化合物半导体键合;

51.将所述第一化合物半导体的衬底去除。

52.优选的,构造第一器件层及设在所述第一器件层周向的至少一侧面的第一共阴极,包括:

53.对所述第一化合物半导体进行图形化曝光和刻蚀构造与所述驱动背板图形相对应的第一器件层并预留与剩余阳极对应的至少一个第一通孔;

54.在所述第一器件层远离所述第一键合层的一侧表面设置第一阴极欧姆接触;

55.采用半导体图形化镀膜在所述至少一个第一通孔出构造用于除第一器件层外的后续器件层的至少一个金属柱;

56.对所述第一化合物半导体进行整面包裹钝化;

57.采用半导体图形化刻蚀工艺对整面氧化硅钝化后的所述第一化合物半导体进行图形化刻蚀形成对应于剩余阳极及所述第一阴极欧姆接触的电气通孔;

58.对所形成的电气通孔进行填充形成剩余阳极的电气连接及形成第一共阴极。

59.优选的,所述第一化合物半导体与所述驱动背板键合形成第一键合层采用绝缘材料,所述将预先准备的第一化合物半导体与所述驱动背板键合,包括:

60.在所述驱动背板整面镀绝缘材料;

61.在第一化合物半导体表面制作第一p型欧姆接触层,并在所述第一p型欧姆接触层表面镀整面绝缘材料;

62.将所述驱动背板与所述第一化合物半导体键合;

63.将所述第一化合物半导体的衬底去除。

64.优选的,构造第一器件层及设在所述第一器件层周向的至少一侧面的第一共阴极,包括:

65.通过图形化刻蚀构造与所述驱动背板图形相对应的第一器件层并裸露相应的第一p型欧姆接触层延伸部;

66.采用图形化刻蚀在所述第一p型欧姆接触层延伸部构造与至少一个所述阳极对应的至少一个第二通孔;

67.对所述第一化合物半导体进行整面包裹钝化;

68.采用半导体图形化刻蚀工艺对整面氧化硅钝化后的所述第一化合物半导体进行图形化刻蚀形成对应于每一阳极的电气通道及对应于所述第一阴极欧姆接触的电气通孔;

69.对所形成的电气通孔进行填充形成对应于第一化合物发光层的第一电气连接结构、对应于第二化合物发光层的部分电气连接结构、对应于第一化合物发光层的第一共阴极。

70.优选的,完成所述第二器件层及设在所述第二器件层周向的至少一侧面的第二共阴极后,所述制作显示单元还包括:

71.将预先准备的第三化合物半导体与所述第二器件层远离所述第一器件层一侧表面键合,并构造第三器件层及设在所述第三器件层周向的至少一侧面的第三共阴极。

72.第三方面,本技术还提供一种微显示屏,其特征在于,所述微显示屏包括:

73.驱动背板,所述驱动背板包括至少两个驱动电路及相应的输入输出接口;

74.显示区域,所述显示区域设于所述驱动背板上,且所述显示区域包括至少两个如第一方面任意一项所述的显示单元及相应的共阴极,至少两个所述显示单元呈阵列式排布;

75.外围共阴极,所述外围共阴极与每一所述显示单元的共阴极电连接。

76.与现有技术相比,本技术具有如下有益效果:

77.本技术提供用于半导体器件的像素单元及其制作方法、微显示屏,像素单元包括驱动背板,驱动背板设有驱动电路,驱动电路设有至少一个阳极;显示单元,显示单元设于驱动背板上,显示单元包括自下而上依次垂直堆叠的第一器件层及第二器件层,第一器件层、第二器件层分别与驱动背板的相应阳极连接;共阴极,共阴极分别与显示单元中的每一器件层连接,共阴极与外部阴极连接;本技术提供的像素单元通过在驱动背板上依次垂直堆叠至少两层器件层的方式实现多色化显示,相较于水平堆叠实现全彩色的像素结构,本技术中像素单元所占的水平方向上的空间较小,像素密度损失较小;进一步,本技术中的显示单元中垂直堆叠的各层采用共阴极,以减小显示单元中阴极的面积占比,提高发光区域面积占比,减小尺寸效应影响,同时可提高垂直方向上器件层的堆叠数量或形成冗余电路;

78.进一步的,共阴极本体为围设于显示单元周向的金属围框;本技术通过设置金属围框,不仅实现了像素内部各器件层的共阴极,金属围框还实现了所有像素的与部阴极的连接即所有像素的共阴极,同时,该金属围栏可作为像素隔离,阻止像素间光学串扰,并具备侧壁反射镜作用;

79.进一步地,共阴极的厚度自靠近驱动背板的一端向另一端递减,形成倒扣型碗型外围阴极,作为约束型侧壁反射结构;

80.进一步,本技术提供的用于半导体器件的像素单元的制作方法,其在进行器件层构造器件层堆叠过程中,采用先构造出金属柱,然后进行钝化,然后对钝化层刻蚀构造电气通孔后在电气通孔中田中以形成电气连接,该方案相较于现有对金属层蚀刻构造电气连接的方案,降低了堆叠方案中构造电气连接工艺难度,尤其提高了干法刻蚀较为困难的金属(如铜)作为电气连接结构的可实现性。

附图说明

81.图1是背景技术中涉及的半导体器件的结构示意图;

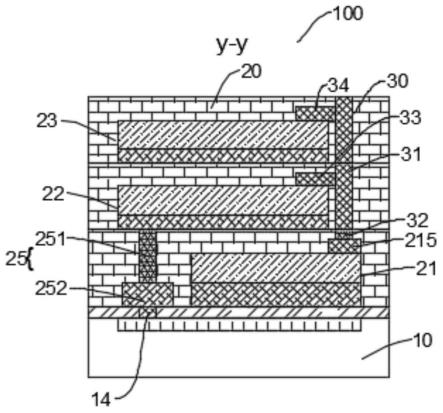

82.图2是实施例1中像素单元的俯视图;

83.图3是图2中x-x截面的剖视图;

84.图4是图2中y-y截面的剖视图;

85.图5是实施例1中驱动背板的示例性电路结构示意图;

86.图6是任意一层器件层的电路结构示意图;

87.图7、8分别为驱动背板的示例性俯视图;

88.图9是驱动背板在表面设置顶部金属的结构图;

89.图10是驱动背板在表面设置原位反射镜的结构图;

90.图11是实施例1中示例性的原位反射镜的可见光波长范围反射率数据;

91.图12是相同化合物发光层材料的至少两个器件层并联设置的电路结构示意图;

92.图13是相同化合物发光层材料的至少两个器件层串联设置的电路结构示意图;

93.图14是实施例1中具有光学增强结构的像素单元结构图示意图;

94.图15是实施例1中镀有键合材料的驱动背板;

95.图16是实施例1中构造第一器件层后的俯视图;

96.图17、18分别是图13中x-x、y-y截面的剖视图。

97.图19~21是实施例1中构造电气连接通道后的俯视图、图16的x-x、图16的y-y截面的剖视图;

98.图22、23分别是实施例1中完成第一器件层电气连接后的x-x、y-y截面的剖视图;

99.图24是实施例1中采用硅作为键合材料的可见光透射率数据;

100.图25、26是实施例2中x-x、y-y截面的剖视图;

101.图27是实施例2中像素单元碗型共阴极的剖视图;

102.图28、29是实施例3中像素单元的俯视图、y

3-y3截面的剖视图;

103.图30、31分别是实施例3中完成首层堆叠、二层堆叠的剖视图;

104.图32是微显示屏的立体结构示意图。

105.附图标记:

106.100-像素单元,10-驱动背板,11-顶部金属,12-原位反射镜,13-第一阳极,14-第二阳极,15-第三阳极,20-显示单元,21-第一器件层,211-第一键合层,212-第一化合物发光层,214-第一绝缘层,215-第一阴极欧姆接触,216-第一p型欧姆接触层,2161-第一p型欧姆接触层延伸部,22-第二器件层,221-第二键合层,222-第二化合物发光层,223-第二阴极欧姆接触,224-第二p型欧姆接触层,2241-第二p型欧姆接触层延伸部。23-第三器件层,231-第三键合层,232-第三化合物发光层,233-第三阴极欧姆接触,234-第三p型欧姆接触,24-绝缘包裹层,25-第二电气连接结构,251-第一金属柱,252-第一连接层,26-第四电气连接结构;27-第一电气连接结构,28-第三电气连接结构,29-第五电气连接结构,30-共阴极,31-共阴极本体,32-第一连接部,33-第二连接部,34-第三连接部,第一共阴极35,第二共阴极36,第三共阴极37,40-光学增强结构,200-半导体器件,300-整面驱动背板,400-显示区域,500-外围共阴极,600-外部io接口。

具体实施方式

107.为使本技术的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

108.在本技术的描述中,需要理解的是,术语“上”、“下”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

109.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本

申请中的具体含义。

110.如背景技术所述,现有的micro-led半导体器件通常采用水平堆叠的方式实现全彩色,而水平堆叠带来的问题是水平方向占用空间大,发光面积占比小等问题,严重影响器件的小尺寸化发展。为此,本实施例提供一种用于半导体器件的像素单元及其制作方法、微显示屏,能有效解决上述问题。

111.实施例1

112.如图2~4所示,本实施例提供一种用于半导体器件的像素单元100,该像素单元包括驱动背板10、显示单元20及共阴极30。该像素单元100用于微显示屏、不可见光的探测器等半导体器件。

113.说明:图3、图4分别是图2(俯视图)中相垂直的两个剖视图,后续结构图也均为当前结构下的俯视图或者相应的剖视图,涉及的x-x截面图为俯视图中水平方向的剖面图,y-y截面图为俯视图中竖直方向的剖面图。

114.其中,驱动背板10设有驱动电路,驱动电路设有至少一个阳极,示例性的,驱动电路电路图如图5所示。需要说明的是,本实施例中的电路图为简单的示意图,均为有源驱动。该像素单元内部的电路可包含主动式、被动式或半被动式的控制电路。示例性的,如下图6为任一层器件层的电路图。显示单元20设于驱动背板10上,且显示单元20包括自下而上依次垂直堆叠的第一器件层21、第二器件层22,第一器件层21、第二器件层22分别与驱动背板10的相应阳极连接。故,本实施例提供的像素单元100为垂直堆叠像素(vertical stack pixel,后续简称vsp)。共阴极30嵌设于显示单元20内,且共阴极30分别与显示单元20中的每一器件层连接,共阴极30与外部阴极连接。优选地,本实施例中的共阴极30为柱状结构或板状结构中的一种。

115.当然,本实施例在垂直方向上堆叠的器件层数量包括但不限于两层,可以是三层、四层甚至更多,且所有器件层所采用的化合物发光层材料可以为相同或不同。当每一器件层所采用的化合物发光层不同时可实现多色彩显示如全彩显示,当两层或两层以上的器件层采用相同的化合物发光层时可实现光照强度的增强或形成冗余结构,当然,两种方案可以共存于同一显示单元20中,本实施例对此不作限制。

116.为了便于说明,本实施例以显示单元20包括第一器件层21、第二器件层22及第三器件层23,且第一器件层21发出红光(r)、第二器件层22发出绿光(g),第三器件层23发出蓝光(b),即实现r、g、b全彩像素。示例性的,第一器件层21采用红光ingan化合物外延,第二器件层22采用绿光ingan化合物外延,第三器件层23采用蓝光ingan化合物外延。

117.具体的,驱动背板10可以是膜晶体管(tft)、低温多晶硅(ltps)、cmos集成电路、高迁移率晶体管(hemt)中的一种,为了便于描述,本实施例以cmos集成电路为例作进一步阐述,但并不以此为限。进一步地,驱动背板10包括的至少两个阳极(阳极通孔)均匀布设,且至少两个阳极均位于显示单元20在驱动背板10的投影范围内。至少两个阳极均匀布设,在三个器件层的实施方式中,可能的布设方式有分布于同一直线上或呈品字型分布等,预设数量的阳极可以是设于驱动背板10的边缘、顶角、中部或中心,如附图7、8所示。本实施例对于驱动背板10设置的阳极通孔的数量不做限制,且通过阳极通孔数量的增加可实现更多层的vsp堆叠或者形成冗余电路。需要说明的是,如图8所示,可以在驱动背板10上设置阴极(阴极通孔),以实现共阴极30与驱动电路连接。

118.更进一步的,驱动背板10包括至少一个顶部金属11,顶部金属11覆盖至少一个阳极,如图9所示。当然,驱动背板10也可以不设置顶部金属11,本实施例对此不做限制。

119.或者,如图10所示,驱动背板10包括设于其上表面的原位反射镜12,原位反射镜12一一对应且覆盖或裸露至少一个阳极。该原位反射镜12可以是金属,铝、金、银等;也可以是布拉格反射层,该布拉格反射层由两种及以上不同折射率的薄膜堆叠而成,如氧化硅与氧化钛的叠层,氧化硅与氧化铝,氧化硅与氮化硅等;也可以是是金属与介电质堆叠的odr全反射镜,如银和氧化硅、铝和氧化铝、金和氧化硅等其中的至少一种组合,如以金属铝250nm与氧化硅150nm(目标波长620nm,1/4为150nm)的叠层在部分可见光波长范围反射率数据如图11所示。

120.原位反射镜12可以是圆形、三角形、四边形,五边形、六边形、八边形等多边形结构,也可以是规避开触点的组合多边形,该多边形可以内切于像素边界,也可以较边界内缩一定长度。

121.进一步如图2~4所示,本实施例中的共阴极30包括共阴极本体31、分别与共阴极本体31连接的第一连接部32、第二连接部33及第三连接部34,第一连接部32与第一器件层21连接,第二连接部33与第二器件层22连接,第三连接部33与第三器件层23连接。

122.具体地,第一器件层21包括第一键合层211、第一化合物发光层212及绝缘包裹层24,第一化合物发光层212贴设于第一键合层211远离驱动背板10的一侧表面,绝缘包裹层24包裹第一键合层211及第一化合物发光层212。

123.优选的,绝缘包裹层24可以是氧化硅、氮化硅、氧化铝等无机介电质材料或者su8、聚酰亚胺等有机介电质材料等,本实施例对此不做限制。

124.第一键合层211采用导电材料或绝缘材料,本实施例中,第一键合层211采用导电材料制成。驱动背板10与第一键合层211之间设有第一绝缘层214,第一绝缘层214设有至少一个第一通孔,第一键合层214穿过第一通孔与相应的第一阳极13连接,以避免在像素堆叠底部出现短接的情况。第一键合层211采用的导电材料可以是ito、zno、gap、gaas、gan等化合物材料,也可以是au、al、cu等金属材料,或者si等半导体材料、sub、bcb等有机介电材料。以及,第一键合层211并不具有透光要求,故采用透明或不透明导电材料均可,此处不作限制。采用的第一绝缘层211可以为sio2膜,且sio2膜厚度为100

±

5nm。

125.在此基础上,第一化合物发光层212通过第一化合物半导体与驱动背板10键合并去掉衬底获得。

126.本实施例中,在第一化合物半导体在p contact面形成p型欧姆接触,其p型欧姆接触材料可以是ito等透明导电材料,也可以是au、zn、be等金属材料的叠层或者合金。p contact面通过蒸镀、溅射等方式进行ito镀膜,且作为一种优选,ito膜厚500nm,通过n2环境下500℃高温退火形成欧姆接触。当然,该化合物表面p contact镀膜接触层厚度和形成接触的条件可根据需求调整变化。

127.示例性的,若衬底为n-gaas,红光为algainp体系,结构如下表1所示:

128.表1

129.layer namematerialp contactp-gaasmqwalgainp

n contactn-algainpetch stopn-algainpsubstraten-gaas

130.若是ingan体系,结构图可以如下表2或表3所示,并且这两种同时可以作为蓝光、绿光等波长化合物结构。

131.表2

132.layer namematerialp contactp-gaasmqwingan&gann contactganetch stopaln&gansubstratesi

133.表3

134.layer namematerialp contactp-ganmqwingan&gann contactganetch stopingansubstrategan

135.进一步,第一连接部32与第一化合物发光层212连接。在一种优选的实施方式中,第一器件层21还包括第一阴极欧姆接触215,第一阴极欧姆接触215贴设于第一化合物发光层212远离第一键合层211的一侧表面,第一连接部32与第一阴极欧姆接触215连接,并通过第一阴极欧姆接触215与第一化合物发光层212电连接。更进一步的,本实施例中的第一连接部32垂直设置,共阴极本体31垂直设置。

136.如图4所示,本实施例中的共阴极30自该第一化合物发光层212表面向上垂直设置,后续的第二连接部33、第三连接部34均为水平设置。

137.继续参照图3、4所示,第二器件层22包括第二键合层221、第二化合物发光层222及绝缘包裹层24;第二化合物发光层222贴设于第二键合221层远离第一器件层21的一侧表面,绝缘包裹层24包裹第二键合层221及第二化合物发光层222。

138.第二键合层221可采用导电材料或绝缘材料,但为了使第一器件层21的红光透过,第二键合层221应采用透明材料。示例性的,本实施例中的第二键合层221采用透明导电材料或透明半导体材料制成。

139.在此基础上,第二器件层22还包括用于与驱动背板10上相应的第二阳极14实现电气连接的第二电气连接结构25,第二电气连接结构25一端与驱动背板10上裸露的相应第二阳极14连接,另一端穿过第一器件层22与第二键合层221连接。

140.更进一步地,第二电气连接结构25的实现方式有多种。在一种实现方式中,第二电气连接结构25包括第一金属柱251,第一金属柱251一端与相应的第二阳极14连接,另一端穿过第一器件层21与第二键合层221连接。在另一种实现方式中,第二电气连接结构25包括第一连接层252及与第一连接层252连接的第一金属柱251,第一连接层252穿过第一绝缘层

214与相应的第二阳极14连接,第一金属柱251与第二键合层221连接。其中的第一连接层252可以是在采用刻蚀进行器件构造时留下的覆盖在第二阳极14上的键合材料形成,也可以是在采用刻蚀进行器件构造形成裸露的第二阳极14通孔后通过半导体图形化镀膜工艺制作提前制作形成。

141.如前所述,当第一化合物发光层212与第二化合物发光层222采用的化合物发光材料相同时,第一器件层21与第二器件层22与同一阳极连接,且第一器件层21与第二器件层22串联或并联设置。可见,当n(n≥2)层化合物vsp堆叠,当至少两层器件层采用的化合物发光材料相同,这两层器件层作为垂直方向的冗余结构,可以实现性能增强以及作为冗余进行像素良率保障,且该至少两层器件层采取像素内共阳、共阴电气连接。

142.示例性的,在全彩微显示屏用的像素单元中,相同化合物发光层的两层器件层并联时,驱动电路如图11所示,当相同化合物发光层的两层器件层串联时,驱动电路如图12所示。

143.需要说明的是,本实施例中的第二电气连接结构25与第一器件层21为非接触状态,故第一器件层21与第二器件层22在驱动背板10上的投影存在一定的重叠及错开部分,错开部分用于第二电气连接结构25及共阴极30在垂直方向上的布置。

144.在优选的实施方式中,第二器件层22还包括第二阴极欧姆接触,第二阴极欧姆接触贴设于第二化合物发光层222远离第二键合层221的一侧表面,第二连接部33与第二阴极欧姆接触连接。进一步优选的,第二连接部33水平设置。

145.与第一器件层21相类似的,在设定第二化合物发光层222的前提下,第二器件层22的绝缘包裹层24与第一器件层21的绝缘包裹24的材料一致,对此本实施例不作具体描述。

146.与第一器件层21及第二器件层22相类似的,第三器件层23堆叠设于第二器件层22远离第一器件层21的一侧。第三器件层23与驱动背板10的第三阳极连接,共阴极30还包括与共阴极本体31连接的第三连接部34,第三连接部34与第三器件层23连接。

147.具体的,第三器件层23同样包括第三键合层231、第三化合物发光层232、绝缘包裹层24、第四电气连接结构26及第三阴极欧姆接触。以及,第三键合层231采用透明导电材料(如ito)制作,第四电气连接结构26一端与第三键合层231连接,另一端穿过第一器件层21及第二器件层22与驱动背板10的第三阳极15连接。优选的,共阴极30包括的第三连接部34通过第三阴极欧姆接触233与共阴极本体31连接,从而实现第一器件层21、第二器件层22及第三器件层23的共阴极30。

148.可以理解的是,本实施例中的第四电气连接结构26与第一器件层21、第二器件层22均为非接触状态,故第三器件层23与第二器件层22、第一器件层21在驱动背板10上的投影存分别在一定的重叠及错开部分,错开部分用于第三阴极欧姆接触25、第四电气连接结构26及共阴极30在垂直方向上的布置,且错开部分的面积占比较小。

149.因此,本实施例中的共阴极30嵌设在显示单元20中,为实现与相邻像素单元100之间的共阴极30,在显示单元20的顶层设置导电膜,通过相邻像素单元100之间导电膜的连接外部阴极共极,以减小显示单元20中阴极的面积占比,提高发光区域面积占比。

150.作为一种优选,像素单元100还包括光学增强结构40,光学增强结构40堆叠于像素单元100远离驱动背板10的一侧。具体地,如图14所示,通过vsp堆叠多个器件层后继续通过vsp堆叠光学增强结构40,如偏振镜、透镜等,透镜可以是有机材料,如su8、聚酰亚胺等,可

以是无机材料,如氧化硅、氧化铝等。

151.因此,本实施例提供的用于半导体器件的像素单元通过在驱动背板上依次垂直堆叠至少两层器件层的方式实现多色化显示,相较于水平堆叠实现全彩色的像素结构,本技术中像素单元所占的水平方向上的空间较小,像素密度损失较小;进一步,本技术中的显示单元中垂直堆叠的各层采用共阴极,以减小显示单元中阴极的面积占比,提高发光区域面积占比,减小尺寸效应影响,同时可提高垂直方向上器件层的堆叠数量或形成冗余电路。

152.对应于本实施例中的用于半导体器件的像素单元,本实施例还提供一种用于半导体器件的像素单元制作方法,该制作方法包括如下步骤:

153.s1、准备驱动背板10,驱动背板10设有驱动电路,驱动电路设有至少一个阳极。与前述的像素单元100相对应的,本实施例中的驱动背板10为cmos背板。

154.s2、制作显示单元20及相应的共阴极30,将预先准备的第一化合物半导体与驱动背板10键合,并构造第一器件层21及与第一器件层21对应的第一共阴极31;将预先准备的第二化合物半导体与第一器件层21远离驱动背板10一侧表面键合,并构造第二器件层22及相应的第二共阴极35,将第二器件层22分别与驱动背板10的对应阳极及第二共阴极35连接,第二共阴极35与第一共阴极34首尾连接形成共阴极30,共阴极30与外部阴极连接。

155.本实施例中,第一化合物半导体与驱动背板10键合形成第一键合层采用导电材料,如ito。化合物半导体通常为晶圆或者从晶圆上切割下的合适大小区域,以晶圆为例,该化合物晶圆是指由两种或两种以上元素以确定的原子配比形成的化合物,并具有确定的禁带宽度和能带结构等半导体性质。包括晶态无机化合物(如iii-v族、ii-vi族化合物半导体)、有机化合物(如有机半导体)和氧化物半导体等,其衬底材料可以是gaas、gan、si、sic、sapphire等,然后在化合物表面制备形成电气接触的层,且在后续vsp堆叠化合物时,可以任意组合。

156.在此基础上,步骤s2具体包括:

157.s21、在驱动背板10设有至少两个阳极的表面整面镀绝缘材料(如sio2)形成第一绝缘层214,并开设与至少两个阳极对应的至少两个第一通孔;

158.s22、在镀绝缘层后的驱动背板10表面整面镀导电材料ito形成镀有键合材料的驱动背板10,整面ito镀膜360

±

10nm。当然,在步骤s22之前,在优选实施方案中,还可以在驱动背板10表面设置原位反射镜12或者与阳极通孔一一对应的顶部金属11。示例性的实施方式为,经过高温ito退火或者在镀膜过程中加热优化ito的光电特性,然后通过cmp工艺将ito凹凸不平表面进行平坦化处理,要求表面粗糙度在0.1~5nm区间,如图15所示。

159.s23、在第一化合物半导体表面整面镀导电材料形成镀有键合材料的第一化合物半导体;具体的,在第一化合物半导体p面整面ni(5nm)au(10nm)叠层,通过高温退火形成欧姆接触从而形成p接触层,对p接触层表面蒸镀、溅射等方式进行ito镀膜,ito膜厚500

±

10nm。之后,在n2环境下500℃高温退火形成欧姆接触优以化ito的光电特性,然后通过化学机械抛光(cmp)工艺将ito凹凸不平表面进行平坦化处理,要求表面粗糙度在0.1~5nm区间。当然,该化合物表面p contact镀膜接触层厚度和形成接触的条件可根据需求调整变化,本实施例对此不做限制。

160.s24、将分别镀有键合材料的驱动背板10与第一化合物半导体键合。

161.s25、将第一化合物半导体的衬底去除,完成第一化合物半导体与驱动背板10的键

合,如图16~18所示。

162.具体的,本实施例通过清洗或表面激活将ito表面进行处理。在一种实施方式中,通过ar等离子体处理后通过氨水浸泡进行表面活化,然后将驱动背板10与第一化合物半导体进行键合,键合后将化合物衬底去除,通过刻蚀方法将化合物n contact露出,该键合可以是无对准键合,也可以是对准键合,当目标化合物为从晶圆中切割而成的部分区域时,可以采用扇出式封装类型进行键合。如,当第一层化合物半导体是是algainp四元化合物,键合后通过氨水、双氧水的混合液去除衬底,并利用盐酸腐蚀裸露出ncontact层。

163.在完成构造第一器件层21及设在第一器件层21周向的至少一侧面的第一共阴极30,具体包括:s26、对第一化合物半导体进行图形化曝光和刻蚀构造与驱动背板10图形相对应的第一器件层21并预留与剩余阳极对应的至少一个第一通孔,第一器件层21包括第一键合层211及第一化合物发光层212。

164.s27、在第一器件层21远离第一键合层的一侧表面设置第一阴极欧姆接触215。具体的,第一阴极欧姆接触215可以是au、ge、ni等金属的叠层或者合金材质。

165.需要说明的是,在进行化合物vsp堆叠时,上述步骤s26、s27的先后顺序并不作限制,可以是先进行第一器件层21构造或先进行第一阴极欧姆接触215构造。

166.具体的,如图16所示,下方半圆填充区为第一阴极欧姆接触215,通过图形化刻蚀工艺裸露处后续两层堆叠的阳极(第二阳极14、第三阳极15),且阳极的裸露可以直接裸露到驱动背板10或者导电的键合材料上,为了便于描述,本实施例以阳极的裸露至驱动背板10为例作进一步描述。

167.s28、采用半导体图形化镀膜在至少一个第一通孔处构造用于除第一器件层21外的后续器件层的至少一个第一金属柱251。

168.s29、对第一化合物发光层212进行整面包裹钝化;包裹钝化所采用的绝缘材料可以是氧化硅、氮化硅、氧化铝等无机介电质材料或者su8、聚酰亚胺等有机介电质材料。如,通过su8等有机硅的旋涂完成钝化。

169.s210、采用半导体图形化刻蚀工艺对整面氧化硅钝化后的第一化合物发光层212进行图形化刻蚀形成对应于剩余阳极及第一阴极欧姆接触215的电气通孔;其中的剩余阳极作为后续堆叠层的阳极(第二阳极14、第三阳极15)。具体如图19~21所示。

170.s211、对所形成的电气通孔进行填充形成剩余阳极的电气连接及形成第一共阴极34,该第一共阴极35包括部分,具体如图22、23所示。

171.步骤s211具体包括:

172.采用金属蒸镀、溅射、电镀、化镀等方式整面填充金属al、ti、w、au、ni或cu的膜层单质、合金或者叠层,然后采用cmp方式将被金属包裹的氧化硅露出,完成第一阴极欧姆接触215的电气通孔的填充和后续器件层的电气连接(即第二电气连接结构25及第四电气连接结构26等)。

173.需要说明的是,上述步骤s28~s211借鉴了集成电路领域的大马士革镶嵌工艺进行电气连接结构的构造,相较于现有对金属层蚀刻构造电气连接的方案,降低了堆叠方案中构造电气连接工艺难度,尤其提高了干法刻蚀较为困难的金属(如铜)作为电气连接结构的可实现性。

174.在步骤s211完成第一器件层21的构造后,按照类似的方法继续构造第二器件层

22、三器件层23,如图2~4所示。

175.具体地,首层堆叠可以选择不透光的材料,如au、cu等,但从第n(n≥2)层堆叠开始,使用的键合薄膜需要对n-1层的化合物进行匹配,保证n-1层化合物半导体发出光的波长能够透过,同时也可以可对n-1层化合物的光进行筛选,选取特定波段的光透过;以及可以第n层的键合材料可以对n或n+1层有光学增强功能,如偏振、反射等。第n层的键合层必须是透明的,可以是导电的,如ito、zno、gap、gaas、gan等化合物材料,也可以是不导电的,包括sio2、ti2o3、si3n4、al2o3、aln等介电质材料的单层或叠对,或者su8、bcb等有机材料,或者在超薄厚度时可透光的材料,如ag、si等,其厚度在20nm以内时具备一定的透射率。在一种实施例中,采用20nm si,其部分可见光透射率数据如24图所示。

176.具体地,第二化合物发光层为绿光ingan材料,阴极欧姆接触材料可以是cr、al、ti、ni等的一种或多种。第三化合物发光层为ingan蓝光外延,器件制备及电气连接后剖面图分别对应俯视图x轴和y轴如图2~4所示。

177.进一步优选的,第n(n≥2)层的键合薄膜包含氧化硅、氧化钛的叠层,可以对n-1层的光进行筛选。如n-1层为红光,出光范围为600~650nm,通过n层键合薄膜进行光筛,可以将透过的光控制在620~630nm波长。或,第n(n≥2)层的键合薄膜包含氧化硅、氧化铝的叠层,可以对n层的光进行反射,如n层为绿光,采用ito键合时,对525nm波长的反射率不足20%。或通过引入150nm氧化铝和180nm氧化硅,对525nm波长的反射率可以超过30%。

178.实施例2

179.如图25、26所示,本实施例提供另一用于半导体器件的像素单元100,该像素单元100与实施例1中的像素单元100结构相似,区别在于:本实施例中的共阴极本体31为围设于显示单元20周向的金属围框。金属围框的材质可以为铝等金属。

180.在该区别下,连接每一器件层(21,22,23)与共阴极本体31的第一连接部32、第二连接部33及第三连接部33位于当前器件层所在上表面所在平面的任一方向,故,第一连接部32、第二连接部33及第三连接部34在驱动背板10上的投影重叠或不重叠均可。

181.作为一种优选,金属围框的每一侧面均为相邻两个像素单元100共用,从而进一步减小共阴极30在像素单元中的面积占比,提高发光区域面积占比。

182.进一步的,共阴极30的厚度自靠近驱动背板10的一端向另一端递减。

183.具体地,金属围框逐层随化合物半导体集成收缩增大,形成倒扣型碗型外围阴极,作为约束型侧壁反射结构,如图27所示。

184.因此,本实施例中的共阴极本体31为金属围框,如此不仅能实现单个像素的阴极互联,甚至能实现基于该像素单元的半导体器件整体的共阴极30。进一步,该金属围框可作为像素隔离,阻止像素间的光学串扰,并具备侧壁反射镜的作用。

185.本实施例中像素单元的制作方法与实施例1中的制作方法基本相同,区别仅在于制备共阴极30时,本实施例采用类大马士革工艺时需要在像素外围进行金属蚀刻与填充最终形成金属围框及对应于每一层的连接部,相关工艺过程参照实施例1中的描述,此处不再具体展开。

186.实施例3

187.本实施例提供又一种用于半导体器件的像素单元,如图28、29所示,其结构基本与实施例1中的像素单元结构具有一定的相似性,区别在于:

188.(1)第一键合层211采用绝缘材料制成,第二键合层221、第三键合层231分别采用透明绝缘材料制成,示例性的,第一键合层211、第二键合层221、第三键合层231均为sio

2-sio2键合层。

189.第一化合物发光层212包括朝向第一键合层211所在一侧设置的第一p型欧姆接触层216,第一p型欧姆接触层216包括朝向共阴极30延伸但不接触共阴极30的第一p型欧姆接触层延伸部2161。第一器件层21还包括第一电气连接结构27,第一电气连接结构27一端与相应的第一阳极13连接,自由端穿过第一键合层211并与第一p型欧姆接触层延伸部2161连接。作为一种优选,第一电气连接结构27的自由端不超过第二器件层22较近的一侧表面,且作为一种优选,第一电气连接结构27的自由端与第二器件层22较近的一侧表面连接,由此实现显示单元20内部的自支撑,提高像素单元100自身的结构强度。

190.第二化合物发光层222包括朝向第二键合层221所在一侧设置的第二p型欧姆接触层224,第二p型欧姆接触层224包括朝向共阴极30延伸但不接触共阴极30的第二p型欧姆接触层延伸部2241。

191.第二器件层22还包括第三电气连接结构28,第三电气连接结构28一端与相应的第二阳极14连接,自由端穿过第一器件层21并与第二p型欧姆接触层延伸部2241连接。

192.第三器件层23还包括第五电气连接结构29及第三p型欧姆接触234,第五电气连接结构29一端与相应的第三阳极15连接,期自由端穿过第一器件层21、第二器件层22并与第三p型欧姆接触层延伸部2341连接。

193.(2)共阴极本体31为围设于显示单元20周向的金属围框。

194.因此,本实施例中的像素单元,各键合层采用绝缘材料,故各电气连接结构需要穿过当前及下方的键合层,才能与驱动背板10的相应阳极分别连接,且每一层均独立地与金属围框连接实现外围共阴极30。本实施例中的像素单元相较于实施例1或实施例2,不仅同样通过共阴极30实现有源区面积占比的增大,且本实施例中的所有器件层的化合物发光层面积相等,在驱动背板10上的投影重合,不存在为避让内部电气连接结构而造成的面积损失或错位设置,进一步提高了水平方向空间利用率及像素密集度,且当多层同时发光时能有效提高单个像素的光强度。

195.相应的制作方法,较实施例1的差别在于:

196.(1)因为第一化合物半导体与驱动背板10键合形成第一键合层211采用绝缘材料,故将预先准备的第一化合物半导体与驱动背板10键合,包括:

197.在驱动背板10整面镀绝缘材料(如sio2);在第一化合物半导体表面制作第一p型欧姆接触层216,并在第一p型欧姆接触层216表面镀整面绝缘材料(如sio2);将驱动背板10与第一化合物半导体键合;将第一化合物半导体的衬底去除。

198.(2)构造第一器件层21及设在第一器件层21周向的至少一侧面的第一共阴极30,包括:

199.通过图形化刻蚀构造与驱动背板10图形相对应的第一器件层21并裸露相应的第一p型欧姆接触层延伸部2161;采用图形化刻蚀在第一p型欧姆接触层延伸部2161构造与至少一个阳极对应的至少一个第二通孔;对第一化合物半导体进行整面包裹钝化;采用半导体图形化刻蚀工艺对整面氧化硅钝化后的第一化合物半导体进行图形化刻蚀形成对应于每一阳极的电气通道及对应于第一阴极欧姆接触215的电气通孔;对所形成的电气通孔进

行填充形成对应于第一化合物发光层212的第一电气连接结构27、对应于第二化合物发光层222的部分电气连接结构、对应于第一化合物发光层212的第一共阴极30,此处的第一共阴极30为部分金属围栏结构。在此基础上,重复构造第二器件层22及第三器件层23,具体结构参照图30、31所示。

200.实施例4

201.本实施例4提供一种微显示屏200,如图32所示,该微显示屏200包括:

202.整面驱动背板300,整面驱动背板300包括至少两个驱动电路及输入输出接口;

203.显示区域400,显示区域设于整面驱动背板300上,且显示区域400包括至少两个如实施例1~3中的显示单元20及相应的共阴极30,至少两个显示单元20呈阵列式排布;

204.外围共阴极500,外围共阴极500与每一显示单元20的共阴极30分别电连接,以使整个微显示屏200共阴极。需要说明的是,外围共阴极500为围设于显示区域400外围的金属围框结构。

205.外部io接口600,位于整面驱动背板300的任意位置。

206.本实施例中的微显示屏的具体结构及相应的技术效果,请参照实施例1~3中的相关描述,本实施例中将不作进一步的详细描述。

207.上述所有可选技术方案,可以采用任意结合形成本技术的可选实施例,即可将任意多个实施例进行组合,从而获得应对不同应用场景的需求,均在本技术的保护范围内,在此不再一一赘述。

208.需要说明的是,以上所述仅为本技术的较佳实施例,并不用以限制本技术,凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1