一种半导体结构的制备方法以及半导体结构与流程

1.本公开涉及集成电路制造领域,尤其涉及一种半导体结构的制备方法以及半导体结构。

背景技术:

2.近几年半导体行业发展迅速,在技术上我们越来越追求纳米器件,芯片生产中特征尺寸不断缩小,整个技术仍然继续朝着关键尺寸进一步微细化方向发展,各电子器件之间的间距越来越小,这对各电子器件正常运行的挑战也就会越来越大。保证细小的电子器件能正常运行并保持着高密度分布,是制程成败的决定性因素之一。因此消除或者降低高深宽比图案变形的问题对dram的生产起着极其重要的作用,其中光刻分辨率和图形转化次数是影响高深宽图案变形的重要元素。首先越小尺寸的光刻技术需要用到越小波长的光源,因为光线间的衍射和干涉会造成曝光过度或者曝光不足的现象从而导致得不到目标图形,而波长小的极紫外线却又需要高昂的技术成本;而多次图形转化会增加异物进入图形或者图形损坏造成最后图形的粘连或者缺失的风险,进而影响产品良率。因此,急需开发更加安全有效,防止高深宽比图案出现变形现象的加工技术。

技术实现要素:

3.有鉴于此,本公开实施例提供一种半导体结构的制备方法以及半导体结构。

4.根据本公开实施例的第一方面,提供了一种半导体结构的制备方法,包括:

5.提供衬底;

6.在所述衬底上形成由牺牲层和支撑层依次层叠形成的叠层结构;所述叠层结构包括靠近所述衬底一侧的第一牺牲层,所述第一牺牲层的材料包括高致密度材料。

7.在一些实施例中,所述高致密度材料为多晶硅。

8.在一些实施例中,还包括:

9.在所述叠层结构上形成依次层叠的第一掩膜层、第一缓冲层、第二掩膜层和第二缓冲层;

10.图案化所述第二缓冲层和所述第二掩膜层,以形成第一图案;

11.在所述第一图案的侧壁形成第一掩膜图案,所述第一掩膜图案沿第一方向延伸;

12.去除所述第二缓冲层和所述第二掩膜层;

13.在所述第一缓冲层上形成依次层叠的第三掩膜层、第三缓冲层、第四掩膜层和第四缓冲层;所述第三掩膜层覆盖所述第一缓冲层,并且填充满所述第一掩膜图案之间的空隙;

14.图案化所述第四缓冲层和所述第四掩膜层,以形成第二图案;

15.在所述第二图案的侧壁形成第二掩膜图案,所述第二掩膜图案沿第二方向延伸,所述第二方向与所述第一方向斜交;

16.去除所述第四缓冲层和所述第四掩膜层。

17.在一些实施例中,所述第一掩膜图案和所述第二掩膜图案交叉排布,以形成呈阵列排布的孔洞;所述孔洞沿第一方向的尺寸和沿第二方向的尺寸范围为30nm~40nm。

18.在一些实施例中,还包括:

19.在形成依次层叠的第一掩膜层、第一缓冲层、第二掩膜层和第二缓冲层之前,在所述叠层结构上形成目标掩膜层,所述第一掩膜层位于所述目标掩膜层上;

20.在去除所述第四缓冲层和所述第四掩膜层之后,还包括:

21.基于所述第二掩膜图案去除暴露出的所述第三缓冲层和所述第三掩膜层;

22.基于所述第一掩膜图案和所述第二掩膜图案,图案化所述第一掩膜层和所述第一缓冲层;

23.去除所述第一掩膜图案、所述第二掩膜图案、保留的所述第三缓冲层和保留的所述第三掩膜层;

24.基于图案化后的所述第一掩膜层和所述第一缓冲层,图案化所述目标掩膜层。

25.在一些实施例中,还包括:

26.基于图案化后的所述目标掩膜层,刻蚀所述叠层结构,形成第一通孔;

27.在所述第一通孔的侧壁形成第三牺牲层。

28.在一些实施例中,所述第三牺牲层的材料包括氧化硅。

29.在一些实施例中,还包括:

30.在形成第三牺牲层后,在所述第三牺牲层的侧壁和所述第一通孔的底面形成电极层。

31.在一些实施例中,所述叠层结构还包括位于所述第一牺牲层上的依次层叠的第一支撑层、第二牺牲层和第二支撑层;

32.在形成电极层后,所述方法还包括:去除部分第二支撑层,以形成第一开口;

33.基于所述第一开口,去除所述第二牺牲层以及所述第一支撑层和所述第二支撑层之间的部分第三牺牲层,保留剩余的所述第二支撑层与所述电极层之间的第三牺牲层。

34.在一些实施例中,所述第一牺牲层的材料和所述第二牺牲层的材料具有高刻蚀选择比。

35.在一些实施例中,还包括:

36.在去除所述第二牺牲层以及所述第一支撑层和所述第二支撑层之间的部分第三牺牲层后,去除部分第一支撑层,以形成第二开口;

37.基于所述第二开口,去除所述第一牺牲层。

38.在一些实施例中,利用碱性溶液刻蚀去除所述第一牺牲层。

39.在一些实施例中,还包括:

40.在去除所述第一牺牲层后,部分去除剩余的所述第三牺牲层,保留剩余的所述第一支撑层与所述电极层之间的第三牺牲层。

41.在一些实施例中,利用hf和nh4f混合溶液,或者hf和nh3混合气体去除所述第二牺牲层和部分第三牺牲层。

42.根据本公开实施例的第二方面,提供了一种半导体结构,包括:

43.衬底;

44.位于所述衬底上的第一支撑层,以及位于所述第一支撑层上的第二支撑层;

45.电容孔,贯穿所述第一支撑层和所述第二支撑层;

46.电极层,覆盖所述电容孔的侧壁和底面;

47.第三牺牲层,位于所述第一支撑层和所述第二支撑层的一侧与所述电极层之间。

48.本公开实施例中,通过设置叠层结构中位于下层的第一牺牲层的材料为高致密度材料,使得叠层结构具有更好的性能,一方面,在刻蚀第一牺牲层上面的结构,例如第二牺牲层或支撑层时,因为第一牺牲层为高致密度材料,如此与第二牺牲层或支撑层具有高刻蚀选择比,这样即使刻蚀溶液或气体刻蚀到第一牺牲层处,也能够有效预防刻蚀溶液或气体对第一牺牲层的破坏,不至于刻蚀穿第一牺牲层,另一方面,提高了叠层结构的牢固性,避免造成叠层结构的坍塌。

附图说明

49.为了更清楚地说明本公开实施例或传统技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

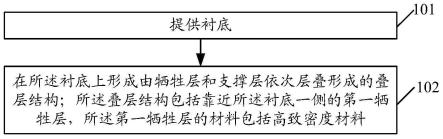

50.图1为本公开实施例提供的半导体结构的制备方法的流程示意图;

51.图2a至图2w为本公开实施例提供的半导体结构在制备过程中的结构示意图;

52.图3为本公开实施例提供的半导体结构的结构示意图。

53.附图标记说明:

54.10-衬底;11-字线;12-电容接触插塞;

55.20-叠层结构;21-第一牺牲层;22-第一支撑层;23-第二牺牲层;24-第二支撑层;25-第三牺牲层;201-第一通孔;250-第三牺牲层预层;251-第三牺牲层的第一部分;252-第三牺牲层的第二部分;

56.30-第三支撑层;

57.40-目标掩膜层;41-第一目标掩膜层;42-第二目标掩膜层;401-第一图案化目标掩膜层;402-第二图案化目标掩膜层;410-第一目标掩膜层开口;420-第二目标掩膜层开口;

58.51-第一掩膜层;52-第一缓冲层;53-第二掩膜层;54-第二缓冲层;55-第三掩膜层;56-第三缓冲层;57-第四掩膜层;58-第四缓冲层;501-第一图案;502-第二图案;503-第三图案;510-第一掩膜图案;520-第二掩膜图案;530-孔洞;

59.61-第一光刻胶层;62-第二光刻胶层;

60.70-电极层;700-电极层预层;701-电容孔;

61.801-第一开口;802-第二开口。

具体实施方式

62.下面将参照附图更详细地描述本公开公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开,而不应被这里阐述的具体实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能够将本公开公开的范围完整的传达给本领域的技术人员。

63.在下文的描述中,给出了大量具体的细节以便提供对本公开更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本公开可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本公开发生混淆,对于本领域公知的一些技术特征未进行描述;即,这里不描述实际实施例的全部特征,不详细描述公知的功能和结构。

64.在附图中,为了清楚,层、区、元件的尺寸以及其相对尺寸可能被夸大。自始至终相同附图标记表示相同的元件。

65.应当明白,当元件或层被称为“在

……

上”、“与

……

相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在

……

上”、“与

……

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本公开教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。而当讨论的第二元件、部件、区、层或部分时,并不表明本公开必然存在第一元件、部件、区、层或部分。

66.空间关系术语例如“在

……

下”、“在

……

下面”、“下面的”、“在

……

之下”、“在

……

之上”、“上面的”等,在这里可为了方便描述而被使用从而描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,然后,描述为“在其它元件下面”或“在其之下”或“在其下”元件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在

……

下面”和“在

……

下”可包括上和下两个取向。器件可以另外地取向(旋转90度或其它取向)并且在此使用的空间描述语相应地被解释。

67.在此使用的术语的目的仅在于描述具体实施例并且不作为本公开的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

68.为了彻底理解本公开,将在下列的描述中提出详细的步骤以及详细的结构,以便阐释本公开的技术方案。本公开的较佳实施例详细描述如下,然而除了这些详细描述外,本公开还可以具有其他实施方式。

69.芯片生产中特征尺寸不断缩小,图形化工艺越来越复杂,需要堆叠更多的薄膜,利用不同薄膜间的蚀刻选择比来实现图形转换达到更小尺寸的目的。

70.在一些实施例中,有一种利用hf溶液去除sicn之间的氧化硅的方法,但可能由于沉积的氮化钛晶向特性不同,hf溶液会渗透氮化钛,刻蚀到下层的氧化硅,在刻蚀支撑层sicn的时候,可能刻蚀穿氧化硅甚至刻蚀到底部的氮化硅,甚至引起图形坍塌。

71.基于此,本公开实施例提供了一种半导体结构的制备方法,具体请参见附图1,如图所示,所述方法包括以下步骤:

72.步骤101:提供衬底;

73.步骤102:在所述衬底上形成由牺牲层和支撑层依次层叠形成的叠层结构;所述叠层结构包括靠近所述衬底一侧的第一牺牲层,所述第一牺牲层的材料包括高致密度材料。

74.下面结合具体实施例对本公开实施例提供的半导体结构的制备方法再作进一步详细的说明。

75.图2a至图2w为本公开实施例提供的半导体结构在制备过程中的结构示意图。需要解释的是,图2d至图2o中未显示出位于目标掩膜层以下的结构。

76.首先,参见图2a,执行步骤101,提供衬底10。

77.所述衬底10可以为硅衬底、锗衬底、硅锗衬底、碳化硅衬底、soi(绝缘体上硅,silicon on insulator)衬底或goi(绝缘体上锗,germanium on insulator)衬底等,还可以为包括其他元素半导体或化合物半导体的衬底,例如玻璃衬底或iii-v族化合物衬底(例如氮化镓衬底或砷化镓衬底等),还可以为叠层结构,例如si/sige等,还可以其他外延结构,例如sgoi(绝缘体上锗硅)等。

78.在一实施例中,继续参见图2a,在所述衬底10内形成字线11和电容接触插塞12,所述电容接触插塞12与后续形成的电极层电连接。需要解释的是,除字线和电容接触插塞,在衬底内还形成有其他器件结构,但本公开实施例中未进行图示。

79.接着,参见图2b,执行步骤102,在所述衬底10上形成由牺牲层和支撑层依次层叠形成的叠层结构20;所述叠层结构20包括靠近所述衬底10一侧的第一牺牲层21,所述第一牺牲层21的材料包括高致密度材料,可以使得叠层结构具有更好的性能,一方面,在刻蚀第一牺牲层上面的结构,例如第二牺牲层或支撑层时,因为第一牺牲层为高致密度材料,如此与第二牺牲层或支撑层具有高刻蚀选择比,这样即使刻蚀溶液或气体刻蚀到第一牺牲层处,也能够有效预防刻蚀溶液或气体对第一牺牲层的破坏,不至于刻蚀穿第一牺牲层,另一方面,提高了叠层结构的牢固性,避免造成叠层结构的坍塌。

80.在一实施例中,所述高致密度材料为多晶硅。需要解释的是,所述第一牺牲层的材料也可以为其他高致密度材料。

81.所述叠层结构20还包括位于所述第一牺牲层21上的依次层叠的第一支撑层22、第二牺牲层23和第二支撑层24。

82.所述第一支撑层22和所述第二支撑层24的材料包括但不限于sicn,所述第二牺牲层23的材料包括但不限于硼磷硅玻璃(bpsg)。

83.继续参见图2b,在所述叠层结构20上形成第三支撑层30。所述第三支撑层30的材料包括但不限于sicn。

84.在实际操作中,所述第一牺牲层21、所述第一支撑层22、所述第二牺牲层23、第二支撑层24和所述第三支撑层30可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

85.接着,参见图2c至图2l,所述方法还包括:在所述叠层结构20上形成依次层叠的第一掩膜层51、第一缓冲层52、第二掩膜层53和第二缓冲层54;

86.图案化所述第二缓冲层54和所述第二掩膜层53,以形成第一图案501;

87.在所述第一图案501的侧壁形成第一掩膜图案510,所述第一掩膜图案510沿第一方向延伸;

88.去除所述第二缓冲层54和所述第二掩膜层53;

89.在所述第一缓冲层52上形成依次层叠的第三掩膜层55、第三缓冲层56、第四掩膜层57和第四缓冲层58;所述第三掩膜层55覆盖所述第一缓冲层52,并且填充满所述第一掩膜图案510之间的空隙;

90.图案化所述第四缓冲层58和所述第四掩膜层57,以形成第二图案502;

91.在所述第二图案502的侧壁形成第二掩膜图案520,所述第二掩膜图案520沿第二方向延伸,所述第二方向与所述第一方向斜交;

92.去除所述第四缓冲层58和所述第四掩膜层57。

93.具体地,先参见图2c,在所述叠层结构20上形成依次层叠的第一掩膜层51、第一缓冲层52、第二掩膜层53和第二缓冲层54。

94.在实际操作中,第一掩膜层51、第一缓冲层52、第二掩膜层53和第二缓冲层54可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

95.在一实施例中,继续参见图2c,在形成依次层叠的第一掩膜层51、第一缓冲层52、第二掩膜层53和第二缓冲层54之前,在所述叠层结构20上形成目标掩膜层40,所述第一掩膜层51位于所述目标掩膜层40上。具体的,在所述第三支撑层30上形成目标掩膜层40。

96.在实际操作中,所述目标掩膜层40可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

97.继续参见图2c,所述方法还包括:在所述第二缓冲层54上形成第一光刻胶层61。

98.在实际操作中,所述第一光刻胶层61可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

99.接着,参见图2d至图2e,图案化所述第二缓冲层54和所述第二掩膜层53,以形成第一图案501。

100.具体地,先参见图2d,图案化所述第一光刻胶层61,以在所述第一光刻胶层61上显示出要刻蚀的第一图案的图形。

101.接着,参见图2e,根据图案化后的第一光刻胶层,图案化所述第二缓冲层54和所述第二掩膜层53,以形成第一图案501。并在形成第一图案501后,去除第一光刻胶层61。

102.接着,参见图2f,在所述第一图案501的侧壁形成第一掩膜图案510,所述第一掩膜图案510沿第一方向延伸。

103.具体地,可以先形成第一掩膜图案预层(图中未显示),所述第一掩膜图案预层覆盖所述一图案501的侧壁和顶部,且覆盖被第一图案501暴露出的第一缓冲层52的表面。

104.接着,参见图2f,去除第一掩膜图案预层位于所述第一图案501的顶部和第一缓冲层52表面的部分,保留位于所述第一图案501侧壁的部分,以形成第一掩膜图案510。

105.接着,参见图2g,去除所述第二缓冲层54和所述第二掩膜层53,只保留第一掩膜图案510。图2g的(2)图为第一掩膜图案的俯视图,如图2g的(2)图所示,所述第一掩膜图案510呈长条状,且沿第一方向延伸。

106.接着,参见图2h,在所述第一缓冲层52上形成依次层叠的第三掩膜层55、第三缓冲

层56、第四掩膜层57和第四缓冲层58;所述第三掩膜层55覆盖所述第一缓冲层52,并且填充满所述第一掩膜图案510之间的空隙。

107.在实际操作中,第三掩膜层55、第三缓冲层56、第四掩膜层57和第四缓冲层58可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

108.继续参见图2h,所述方法还包括:在所述第四缓冲层58上形成第二光刻胶层62。

109.在实际操作中,所述第二光刻胶层62可以使用一种或多种薄膜沉积工艺形成;具体地,所述沉积工艺包括但不限于化学气相沉积(cvd)工艺、等离子体增强化学气相沉积(pecvd)工艺、原子层沉积(ald)工艺或其组合。

110.接着,参见图2i和图2j,图案化所述第四缓冲层58和所述第四掩膜层57,以形成第二图案502。

111.具体地,先参见图2i,图案化所述第二光刻胶层62,以在所述第二光刻胶层62上显示出要刻蚀的第二图案的图形。

112.接着,参见图2j,根据图案化后的第二光刻胶层,图案化所述第四缓冲层58和所述第四掩膜层57,以形成第二图案502。并在形成第二图案502后,去除第二光刻胶层62。

113.接着,参见图2k,在所述第二图案502的侧壁形成第二掩膜图案520,所述第二掩膜图案520沿第二方向延伸,所述第二方向与所述第一方向斜交。

114.具体地,可以先形成第二掩膜图案预层(图中未显示),所述第二掩膜图案预层覆盖所述二图案502的侧壁和顶部,且覆盖被第二图案502暴露出的第三缓冲层56的表面。

115.接着,参见图2k,去除第二掩膜图案预层位于所述第二图案502的顶部和第三缓冲层56表面的部分,保留位于所述第二图案502侧壁的部分,以形成第二掩膜图案520。

116.接着,参见图2l,去除所述第四缓冲层58和所述第四掩膜层57,只保留第二掩膜图案520。图2l中的(2)图为第一掩膜图案和第二掩膜图案的俯视图,如图2l中的(2)图所示,所述第二掩膜图案520呈长条状,且沿第二方向延伸,且所述第二方向与所述第一方向斜交。

117.在一实施例中,第一方向和第二方向的夹角范围为55

°

~65

°

。具体地,第一方向和第二方向之间的夹角可以为55

°

、60

°

、65

°

等等。

118.在一实施例中,所述第一掩膜图案和所述第二掩膜图案可以使用特征尺寸最小为38nm的arf-wet光刻工艺技术刻蚀形成,但不仅限于这种光刻工艺技术。

119.在一实施例中,如图2l中的(2)图所示,所述第一掩膜图案510和所述第二掩膜图案520交叉排布,以形成呈阵列排布的孔洞530;所述孔洞530沿第一方向的尺寸和沿第二方向的尺寸范围为30nm~40nm。

120.在原先的半导体结构的制备过程中,所述第一掩膜图案和所述第二掩膜图案的宽度为20nm~30nm,而在本公开实施例中,减小了所述第一掩膜图案和所述第二掩膜图案的宽度,变为10nm~15nm,因此,孔洞沿第一方向的尺寸和沿第二方向的尺寸由原先的15nm~25nm变为本公开实施例中的30nm~40nm。通过减小第一掩膜图案和第二掩膜图案的宽度,来增加孔洞的尺寸。

121.在一些实施例中,利用两次间接自对准双重图形(self-aligned double patterning,sadp)技术形成设计的器件图形,但是刻蚀后的副产物如果进入了回刻蚀图形

中或者破坏了回刻蚀图形,极易给后续电容器件的成型造成一些电容器件短接的问题,特征尺寸的减小也加大了异物处理的难度,而多次的图形转化更是加大了这种风险。因此本公开实施例中,通过增大孔洞的尺寸,来增大特征尺寸,进而减少造成电容器件短接的问题。

122.在一实施例中,上述实施例中的第一掩膜层51、第二掩膜层53、第三掩膜层55和第四掩膜层57可以包括但不仅限于旋涂掩膜层(soh,spin-on hard mask)。旋涂掩膜层可以包括非晶碳层或非晶硅层。第一缓冲层52、第二缓冲层54、第三缓冲层56和第四缓冲层58可以包括但不仅限于氮化硅层或氧化物层,氧化物层可以包括正硅酸乙酯形成的氧化硅层。所述第一掩膜图案510和所述第二掩膜图案520的材料可以包括但不限于氧化物材料。

123.接着,参见图2m至图2o,在去除所述第四缓冲层58和所述第四掩膜层57之后,所述方法还包括:基于所述第二掩膜图案520去除暴露出的所述第三缓冲层56和所述第三掩膜层55;

124.基于所述第一掩膜图案510和所述第二掩膜图案520,图案化所述第一掩膜层51和所述第一缓冲层52,以形成第三图案503;

125.去除所述第一掩膜图案510、所述第二掩膜图案520、保留的所述第三缓冲层56和保留的所述第三掩膜层55;

126.基于图案化后的所述第一掩膜层51和所述第一缓冲层52,图案化所述目标掩膜层40。

127.具体地,先以第二掩膜图案520为掩膜刻蚀暴露出的所述第三缓冲层56和所述第三掩膜层55,并且,在此过程中,不会去除第一掩膜图案510。然后基于所述第一掩膜图案510、所述第二掩膜图案520、保留的所述第三缓冲层56和保留的所述第三掩膜层55为掩膜,刻蚀所述第一掩膜层51和所述第一缓冲层52。然后,去除所述第一掩膜图案510、所述第二掩膜图案520、保留的所述第三缓冲层56和保留的所述第三掩膜层55。然后,以保留的第一掩膜层51和第一缓冲层52为掩膜,刻蚀目标掩膜层40,以图案化所述目标掩膜层40。

128.参见图2m,所述目标掩膜层40包括第一目标掩膜层41和第二目标掩膜层42。在一实施例中,所述第一目标掩膜层41包括但不限于多晶硅层,所述第二目标掩膜层42包括但不限于氧化物层。例如,第二目标掩膜层42包括正硅酸乙酯形成的氧化硅层。

129.在一实施例中,所述基于图案化后的所述第一掩膜层51和所述第一缓冲层52,图案化所述目标掩膜层40,包括:

130.基于图案化后的所述第一掩膜层51和所述第一缓冲层52,图案化所述第二目标掩膜层42,以得到第二图案化目标掩膜层402;

131.去除图案化后的所述第一掩膜层51和所述第一缓冲层52;

132.基于第二图案化目标掩膜层402,图案化所述第一目标掩膜层41,以得到第一图案化目标掩膜层401;

133.去除第二图案化目标掩膜层402。

134.具体地,先参见图2m和图2n,以图案化后的所述第一掩膜层51和所述第一缓冲层52为掩膜刻蚀第二目标掩膜层42,以得到第二图案化目标掩膜层402。参见图2n中的(2)图,所述第二图案化目标掩膜层402上形成有尺寸一致且分布均匀的第二目标掩膜层开口420,第二目标掩膜层开口420可以呈阵列排布。例如,第二图案化目标掩膜层402内可以形成有

多个呈阵列排布的圆形或椭圆形开口,各开口沿同一方向的宽度均相同。然后,去除图案化后的所述第一掩膜层51和所述第一缓冲层52。然后,参见图2o,以第二图案化目标掩膜层402为掩膜,刻蚀第一目标掩膜层41,以得到第一图案化目标掩膜层401;并去除第二图案化目标掩膜层402。参见图2o中的(2)图,所述第一图案化目标掩膜层401上形成有尺寸一致且分布均匀的第一目标掩膜层开口410,第一目标掩膜层开口410可以呈阵列排布。例如,第一图案化目标掩膜层401内可以形成有多个呈阵列排布的圆形或椭圆形开口,各开口沿同一方向的宽度均相同。

135.接着,参见图2p至图2r,所述半导体结构的制备方法还包括:基于图案化后的所述目标掩膜层40,刻蚀所述叠层结构20,形成第一通孔201;在所述第一通孔201的侧壁形成第三牺牲层25。

136.具体地,先参见图2p,基于图案化后的所述目标掩膜层40,刻蚀所述叠层结构20,形成第一通孔201。更具体的,在刻蚀叠层结构20的过程中,同时将第三支撑层30进行刻蚀,以使所述第一通孔201贯穿所述第三支撑层30和所述叠层结构20。这里,所述第一通孔的孔径不宜过大,以防后续作为补偿的第三牺牲层的厚度过厚,在刻蚀去除第三牺牲层后,剩余的支撑层的厚度不够,而造成图形的坍塌。

137.接着,参见图2q,在所述第一通孔201的侧壁和底面,以及所述第三支撑层30的表面形成第三牺牲层预层250。

138.接着,参见图2r,刻蚀去除所述第一通孔201的底面和所述第三支撑层30表面的第三牺牲层预层250,以在所述第一通孔201的侧壁形成第三牺牲层25。

139.在一实施例中,所述第三牺牲层25的材料包括氧化硅。

140.所述第三牺牲层25可以通过低温氧化硅化学气相沉积工艺形成。

141.所述第三牺牲层25的厚度可以由第一通孔201的孔径和后续用于形成电极层的电极孔的孔径的差值决定。这里,用第三牺牲层来补偿第一通孔扩大的孔径,且有了侧壁处的第三牺牲层的保护,后续在刻蚀去除第一牺牲层的过程中,能更好的保护半导体结构的形貌,避免器件发生坍塌。

142.接着,参见图2s至图2t,所述半导体结构的制备方法还包括:在形成第三牺牲层25后,在所述第三牺牲层25的侧壁和所述第一通孔201的底面形成电极层70。

143.具体地,先参见图2s,在所述第三牺牲层25的侧壁和所述第一通孔201的底面,以及所述第三支撑层30的表面形成电极层预层700。

144.接着,参见图2t,刻蚀去除所述第三支撑层30表面的电极层预层700,以在所述第三牺牲层25的侧壁和所述第一通孔201的底面形成电极层70。

145.所述电极层70的材料包括但不限于氮化钛。

146.接着,参见图2u,在形成电极层70后,所述方法还包括:去除部分第二支撑层24,以形成第一开口801;

147.基于所述第一开口801,去除所述第二牺牲层23以及所述第一支撑层22和所述第二支撑层24之间的部分第三牺牲层25,保留剩余的所述第二支撑层24与所述电极层70之间的第三牺牲层。

148.在一实施例中,具体地,可以利用hf和nh4f混合溶液,或者hf和nh3混合气体去除所述第二牺牲层23和部分第三牺牲层25。

149.具体地,在去除部分第二支撑层24时,同时去除部分第三支撑层30以及部分电极层70。剩余的所述第二支撑层24和剩余的所述第三支撑层30与所述电极层70之间保留的第三牺牲层为第三牺牲层的第一部分251。

150.接着,参见图2v,在去除所述第二牺牲层23以及所述第一支撑层22和所述第二支撑层24之间的部分第三牺牲层25后,去除部分第一支撑层22,以形成第二开口802;基于所述第二开口802,去除所述第一牺牲层21。

151.具体地,可以利用碱性溶液刻蚀去除所述第一牺牲层21。所述碱性溶液包括但不限于tmah、naoh、koh或nh4oh。

152.在一实施例中,所述第一牺牲层21的材料和所述第二牺牲层23的材料具有高刻蚀选择比。

153.接着,参见图2w,所述方法还包括:在去除所述第一牺牲层21后,部分去除剩余的所述第三牺牲层25,保留剩余的所述第一支撑层22与所述电极层70之间的第三牺牲层。

154.实际操作中,可以利用hf和nh4f混合溶液,或者hf和nh3混合气体去除部分第三牺牲层。

155.剩余的所述第一支撑层22与所述电极层70之间保留的第三牺牲层为第三牺牲层的第二部分252。

156.所述第三牺牲层的第一部分和第二部分可以作为支撑层使用,保证了半导体结构的稳固性。

157.本公开实施例还提供了一种半导体结构,图3为本公开实施例提供的半导体结构的结构示意图。

158.如图3所示,所述半导体结构,包括:衬底10;位于所述衬底10上的第一支撑层22,以及位于所述第一支撑层22上的第二支撑层24;电容孔701,贯穿所述第一支撑层22和所述第二支撑层24;电极层70,覆盖所述电容孔701的侧壁和底面;第三牺牲层25,位于所述第一支撑层22和所述第二支撑层24的一侧与所述电极层70之间。

159.所述衬底10可以为硅衬底、锗衬底、硅锗衬底、碳化硅衬底、soi(绝缘体上硅,silicon on insulator)衬底或goi(绝缘体上锗,germanium on insulator)衬底等,还可以为包括其他元素半导体或化合物半导体的衬底,例如玻璃衬底或iii-v族化合物衬底(例如氮化镓衬底或砷化镓衬底等),还可以为叠层结构,例如si/sige等,还可以其他外延结构,例如sgoi(绝缘体上锗硅)等。

160.在一实施例中,所述衬底10内形成有字线11和电容接触插塞12,电容接触插塞12与电极层70电连接。需要解释的是,除字线和电容接触插塞,衬底内还形成有其他器件结构,但本公开实施例中未进行图示。

161.在一实施例中,所述半导体结构还包括:第三支撑层30,位于所述第二支撑层24上。

162.在一实施例中,所述第三牺牲层还包括位于所述第三支撑层30与所述电极层70之间的部分。

163.所述第三牺牲层位于所述第二支撑层24和所述第三支撑层30与所述电极层70之间的部分为第三牺牲层的第一部分251,所述第三牺牲层位于所述第一支撑层22与所述电极层70之间的部分为第三牺牲层的第二部分252。所述第三牺牲层的第一部分和第二部分

可以作为支撑层使用,保证了半导体结构的稳固性。

164.在一实施例中,所述第一支撑层22、所述第二支撑层24和所述第三支撑层30的材料包括但不限于sicn。所述第三牺牲层25的材料包括氧化硅。所述电极层70的材料包括但不限于氮化钛。

165.以上所述,仅为本公开的较佳实施例而已,并非用于限定本公开的保护范围,凡在本公开的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1