一种SOI晶圆及制造方法与流程

一种soi晶圆及制造方法

技术领域

1.本发明涉及半导体技术领域,具体涉及一种soi晶圆及制造方法。

背景技术:

2.soi(silicon-on-insulator)即绝缘衬底上硅,是一种具有“硅-绝缘层-硅”层状结构的新型衬底材料,是通过在顶层硅晶圆与底层硅晶圆之间填充一层氧化物作为绝缘层,利用绝缘层实现顶层硅晶圆上的器件与底层硅晶圆之间的隔离。

3.现有制造soi晶圆的方法如下:

4.分别在顶层硅晶圆及底层硅晶圆表面形成氧化层——分别对顶层硅晶圆的键合面及底层硅晶圆的键合面进行plasma等离子体注入——将顶层硅晶圆的键合面与底层硅晶圆的键合面键合连接——对顶层硅晶圆表面进行减薄至标准规格厚度。

5.采用上述方法制造soi晶圆时,由于制造过程中高能量等离子体的注入令soi晶圆内部产生较大的应力,会造成soi晶圆减薄后产生较大的弯曲度,根据统计测量,该弯曲度可达-90μm左右(根据统计主要分布在-80μm~105μm),不利于后续工艺。

技术实现要素:

6.本发明首先公开一种soi晶圆的制造方法,可有效改善soi晶圆的弯曲度,具体采用如下技术方案来实现:

7.一种soi晶圆的制造方法,包括:

8.提供第一硅晶圆和第二硅晶圆;

9.分别在所述第一硅晶圆的键合面和所述第二硅晶圆的键合面形成键合面氧化层;

10.分别对所述第一硅晶圆的键合面及所述第二硅晶圆的键合面进行等离子体注入;

11.将所述等离子体注入后的所述第一硅晶圆的键合面与所述第二硅晶圆的键合面键合;

12.所述键合后,对所述第一硅晶圆的非键合面进行第一次减薄;

13.所述第一次减薄后,在所述第二硅晶圆的非键合面形成介质层。

14.进一步,所述介质层为二氧化硅层。

15.进一步,所述介质层的厚度为

16.进一步,所述介质层形成后,对所述第一硅晶圆的非键合面进行第二次减薄,所述第二次减薄采用酸性腐蚀液进行减薄。

17.进一步,所述第二次减薄后,对所述第一硅晶圆的非键合面进行第三次减薄,所述第三次减薄采用化学机械减薄方式进行减薄。

18.进一步,所述第一硅晶圆的非键合面和所述第二硅晶圆的非键合面各自形成非键合面氧化层,所述介质层形成于所述第二硅晶圆的非键合面氧化层表面。

19.本发明还公开一种soi晶圆,包括依次层叠的介质层、第二硅晶圆、第一氧化层、第一硅晶圆,所述soi晶圆采用上述制造方法制造而成。

20.进一步,所述第二硅晶圆与所述介质层之间形成有第二氧化层。

21.进一步,所述介质层的厚度大于所述第二氧化层的厚度。

22.进一步,所述介质层为二氧化硅层;所述介质层的厚度为

23.本发明在第二硅晶圆的非键合面上形成一介质层,该介质层是在第一硅晶圆与第二硅晶圆键合后并且对第一硅晶圆的非键合面第一次减薄后所形成,利用该介质层来抵消第一硅晶圆与第二硅晶圆键合导致的内应力,对于改善soi晶圆的弯曲度效果显著。

附图说明

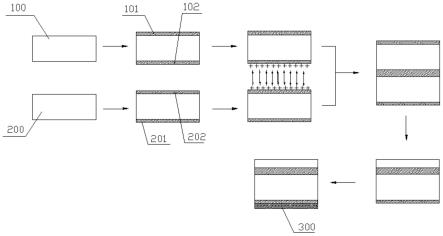

24.图1为采用本发明实施例中制造方法制造soi晶圆的过程示意图;

25.图2为本发明实施例中公开的soi晶圆的结构示意图;

26.图3为第二硅晶圆非键合面上介质层厚度对soi晶圆弯曲度的影响曲线。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。

28.本实施例首先公开一种soi晶圆的制造方法,结合图1所展示的形成soi晶圆的制造过程,对本实施例的制造方法介绍如下:

29.本实施例中的soi晶圆的制造方法包括如下步骤:

30.s1:提供第一硅晶圆100和第二硅晶圆200;

31.s2:分别在第一硅晶圆100的键合面和第二硅晶圆的键合面形成键合面氧化层;

32.s3:分别对第一硅晶圆100的键合面及第二硅晶圆200的键合面进行plasma等离子体注入;

33.s4:将plasma等离子体注入后的第一硅晶圆100的键合面与第二硅晶圆200的键合面键合;

34.s5:按照s4完成键合后,对第一硅晶圆100的非键合面进行第一次减薄;

35.s6:按照s5完成第一次减薄后,在第二硅晶圆200的非键合面形成介质层300。

36.作为上述制造方法的进一步说明,第一硅晶圆100对应于背景技术中提及的作为器件结构层的顶层硅晶圆,第二硅晶圆200对应于背景技术中提及的底层硅晶圆。第一硅晶圆100的键合面是指如图1所示的第一硅晶圆100的底面,第一硅晶圆100的非键合是指图1所示第一硅晶圆100的顶面;第二硅晶圆200的键合面是指图1中第二硅晶圆200的顶面,第二硅晶圆200的非键合面是指图1中第二硅晶圆200的底面。

37.在上述步骤s2中,通常第一硅晶圆100与第二硅晶圆200一同被放入热氧化炉管中,通过热氧化方式在第一硅晶圆100的两面以及第二硅晶圆200的两面各自形成氧化层,即第一硅晶圆100的非键合面形成非键合面氧化层101,第一硅晶圆100的键合面形成键合面氧化层102;第二硅晶圆200的非键合面形成非键合面氧化层201,第二硅晶圆200的键合面形成键合面氧化层202。当然,若不采用热氧化方式形成步骤s2中的键合面氧化层,也可以采用其他方式至少在第一硅晶圆100的键合面形成一层键合面氧化层,在第二硅晶圆200的键合面形成一层键合面氧化层,本实施例中采用常压炉管热氧化生长二氧化硅方式形成键合面氧化层,主要基于热氧化方式所形成的氧化层致密性高且成本较低。

38.在上述步骤s5中,本实施例对第一硅晶圆100的非键合面进行第一次减薄采用taiko减薄工艺,第一次减薄后第一硅晶圆100的剩余厚度约为41.5μm。

39.s5步骤执行完毕后,soi晶圆内部的应力较大导致soi晶圆弯曲度增大,为消除键合过程中的张应力导致的形变,本实施例于步骤s6中在第二硅晶圆200的非键合面形成介质层300,介质层300形成对soi晶圆产生压应力,两种应力互相补偿可以改善soi晶圆的弯曲度。

40.鉴于本实施例在步骤s2中形成的键合面氧化层采用热氧化方式,第二硅晶圆200的非键合面上形成有非键合面氧化层201,介质层300形成于第二硅晶圆200的非键合面氧化层201表面上。

41.介质层300材料可为二氧化硅或氮化硅(si3n4)。优选地,本实施例中的介质层300为二氧化硅层;该介质层300是通过teos(正硅酸乙酯)作为硅源通过cvd沉积所形成,主要是因为二氧化硅的介电常数较低,且其静电吸附力比si3n4更强,避免所形成的介质层300与第二硅晶圆200的非键合面氧化层201分层掉落。

42.介质层300的厚度变化与对soi晶圆弯曲度(bow)的改善如图3所示,由此可见介质层300沉积越厚,对soi晶圆的弯曲度改善效果越明显,根据现有soi晶圆对弯曲度的工艺标准,将介质层300厚度控制在完全可以满足检验标准。

43.上述制造方法中,步骤s6执行完毕形成介质层300后,还包括步骤s7和步骤s8,即:

44.s7:对第一硅晶圆100的非键合面进行第二次减薄,第二次减薄采用化学减薄方式,用酸性腐蚀液刻蚀方式进行减薄。

45.s8:对第一硅晶圆100的非键合面进行第三次减薄,第三次减薄采用化学机械抛光(cmp工艺)方式进行减薄。

46.第三次减薄后,第一硅晶圆100的剩余厚度为23~27μm,该厚度的第一硅晶圆100作为器件结构层通常适用于大功率开关器件、高速bipolar电路、mems器件的制造。

47.本发明制造方法中对于介质层300的形成选择在s5步骤后进行,是因为通过介质层300的沉积对soi晶圆的弯曲度改善效果对于薄片更加显著。发明人发现,如果为了改善soi晶圆的弯曲度而将介质层300的形成步骤放在步骤s2与s3之间,则由于键合前介质层300的存在会导致第二硅晶圆200弯曲度增大,会使得第一硅晶圆100与第二硅晶圆200键合时,第二硅晶圆200的边缘极易形成键合空洞,该键合空洞会导致soi晶圆的报废率显著增加,据统计,可以造成高达40%的报废率。因此,本实施例中选择在步骤s5之后形成介质层300,不会影响键合前第二硅晶圆200的弯曲度,第一硅晶圆100和第二硅晶圆200键合前能保持较好的平整度,键合后形成的soi晶圆边缘空洞率低。

48.soi晶圆通过步骤s6形成介质层300之后,还分别通过步骤s7进行第二次减薄(酸腐蚀方式)、通过步骤s8进行第三次减薄(cmp工艺),三次减薄作业才达到标准厚度要求。若本发明的介质层300选择在步骤s8之后形成,则介质层300的沉积过程会对soi晶圆已经抛光的正面造成划伤的风险。若介质层300的形成选择在步骤s7与步骤s8之间进行,在形成介质层300的过程中也会对soi晶圆的正面造成污染,因此,本发明选择介质层300的形成介于步骤s5和步骤s7之间进行,既能优化soi晶圆的弯曲度,又避免了soi晶圆表面被划伤和污染的问题。

49.利用本发明上述制造方法制造soi晶圆,与背景技术中提及的现有方法(以下简称“方法一”)以及将介质层300调整到步骤s2与s3之间形成的方法(以下简称“方法二”)制造soi晶圆进行bow值、产品良率测试对比,比较结果见表1。

50.表1:本发明制造方法、方法一、方法二制造的soi晶圆对比结果

51.统计值方法一方法二本发明方法bow(弯曲度)-89.3μm-34.2μm-34.6μm产品良率——60%95%

52.为验证本发明所给出的制造方法对soi晶圆弯曲度的改善效果,分别利用方法一和方法二进行soi晶圆的制造与本发明制造方法来进行对比,将三种制造方法制造而成的soi晶圆各自进行同等数量soi晶圆的弯曲度测量,上述表1中给出的bow值为同等数量soi晶圆弯曲度测量结果的平均值。表1中还对方法二和本发明方法制造的soi晶圆进行同等数量晶圆的键合空洞检验,采用相同的空洞检验标准,剔除不符合空洞检验标准的soi晶圆,统计被抽检soi晶圆数量中符合空洞检验标准的soi晶圆,计算两种方法得到的产品良率。

53.对表1中给出的bow改善效果分析:方法一没有采用降低soi晶圆内部键合应力的措施,而方法二和本发明方法都采用了在soi晶圆的第二硅晶圆200非键合面沉积介质层300来补偿内部键合应力,由表1中给出的三种制造方法统计的bow数值可以看出,方法二和本发明方法得到的soi晶圆弯曲度明显低于方法一,本发明方法中制成的soi晶圆的bow值低于方法一bow值的61.25%,证实了本发明的制造方法具有低应力特性。

54.对表1中给出的产品良率改善效果分析:方法一中的第一硅晶圆100与第二硅晶圆200键合前比较厚,并且第二硅晶圆200非键合面并未在键合前额外沉积介质层300,不会导致第二硅晶圆200在键合前产生形变弯曲,因此,第一硅晶圆100的键合面与第二硅晶圆200键合面都相对平整,键合空洞较少,因键合空洞缺陷造成的产品良率低的问题并不突出,因此本实施例仅对方法二和本发明方法所制造的soi晶圆进行了产品良率的统计比较。方法二中在键合前的第二硅晶圆200的非键合面形成介质层300,介质层300的形成会改变键合前第二硅晶圆200的弯曲度,当第一硅晶圆100与第二硅晶圆200键合时,弯曲的第二硅晶圆200边缘极易形成键合空洞,该键合空洞容易超出现有工艺对空洞的检验标准,由此导致soi晶圆的报废率显著增加,按方法二制造soi晶圆因键合空洞造成的报废率高达40%(对应的产品良率只有60%左右)。而本发明方法中形成在第二硅晶圆200非键合面上的介质层300是在键合后形成,不会影响键合前第二硅晶圆200的弯曲度,第一硅晶圆100和第二硅晶圆200键合前能保持较好的平整度,键合后形成的soi晶圆边缘空洞率低,因键合空洞造成的报废率仅在5%左右(对应的产品良率高达95%左右)。由此可见,本发明的制造方法在改善弯曲度的基础上还显著降低了键合空洞率,令soi晶圆的良率大幅度提升。

55.本实施例还公开一种采用上述soi晶圆的制造方法制造而成的soi晶圆,如图2所示,自下而上包括依次层叠的介质层300、第二氧化层、第二硅晶圆200、第一氧化层、第一硅晶圆100。其中第一氧化层包括上述给出的制造方法中提及的键合面氧化层102和键合面氧化层202,第二氧化层对应于上述制造方法中提及的非键合面氧化层201。

56.上述方案中的soi晶圆,介质层300为二氧化硅层,是通过正硅酸乙酯作为硅源利用cvd工艺沉积所形成,可以起到降低应力改善soi晶圆弯曲度的作用,介质层300的厚度大于第二氧化层的厚度,介质层300的厚度控制在能够满足现有工艺中对弯曲度值的检验标准。

57.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1