一种在硅上形成锗器件的方法与流程

1.本发明属于半导体器件制造技术领域,其具体涉及一种在硅上形成锗器件的方法。

背景技术:

2.图像传感器被越来越多地应用至汽车工业、工程机械、农业及生命科学等领域中。相较于可见光感测图像传感器而言,短波红外(swir,short-wavelength infrared)图像传感器在夜视、雾天等低视觉环境下具有更好的穿透性和更高的灵敏度。

3.目前现有的一种短波红外cmos图像传感器是基于砷化铟镓材料制成,其结构自下而上依次包括cmos读出集成电路、连接使用的金属凸点(bumps,例如铟凸点)、与该金属凸点相连的砷化铟镓阵列、磷化铟衬底和防反射层。由于采用了金属凸点的键合工艺,导致像素间距较大、传感器的厚度较厚,不利于实现器件的小型化。并且晶圆尺寸有限、产量低、化合物匮乏等原因,砷化铟镓的制造成本较高。在制造过程中需要芯片对芯片/芯片对晶圆键合,以及由于以磷化铟为基底,砷化铟镓外延生长制作的cmos图像传感器降低了对可见光的吸收,所以制造工艺复杂且昂贵导致量产难度提高。再者,砷化铟镓与硅在化学上不相容,这导致了基于砷化铟镓的图像传感器在制造工艺上难以与现有的硅cmos制造工艺相兼容。

4.另一种现有的传感器就是基于硅衬底制作的图像传感器。但是硅传感器的光谱响应被限制在波长1μm以内,其在近红外光谱中有着较低的光吸收效率。而锗传感器则在0.4μm~1.6μm范围内有着较好的光响应。由此产生了不少关于硅基锗(ge-on-si)短波红外图像传感器的研究。

5.外延生长法是一种现有的制作硅基锗的方法,即直接在硅衬底上生长锗层。但是由于硅和锗之间晶格失配度(lattice mismatch)为4.2%,而失配能的累积会在二者界面之间产生失配位错(misfit dislocation)和穿透位错(threading dislocation)等缺陷。为了抑制失配位错和穿透位错这类缺陷,则需要提高其制造工艺的复杂度(例如,采用狭窄孔径的选择性生长)。

技术实现要素:

6.基于现有技术中存在的技术问题,本发明提供一种在硅上形成锗器件的方法,本发明方法解决了现有技术中外延生长法制作硅基锗会产生位错且工艺复杂度较高的缺陷的技术问题,提供一种工艺简单、没有晶格失配的在硅上形成锗器件的方法。

7.依据本发明的技术方案,提供一种在硅上形成锗器件的方法,其在锗供体晶圆的正面形成隔离结构和pin光电二极管;进行氢离子注入以在pin光电二极管下方的锗供体晶圆中形成氢注入层,在pin光电二极管层上形成第一互连层,继而在硅电路晶圆上形成第二互连层,通过第一互连层和第二互连层的键合来在硅上形成锗器件。

8.其中,在pin光电二极管层上形成第一互连层之后,进一步包括提供一硅电路晶

圆,在硅电路晶圆上形成包括用于控制和读取pin光电二极管的电路和至少一个第二互连层;进行第一互连层和第二互连层的初次键合以连接锗供体晶圆和硅电路晶圆;通过切割和剥离所述氢注入层处使pin光电二极管层和第一互连层与锗供体晶圆分离;退火以完成第一互连层和第二互连层的最终键合。

9.具体地,一种在硅上形成锗器件的方法包括以下步骤:

10.s1:提供一锗供体晶圆;

11.s2:在锗供体晶圆的正面形成隔离结构,所述隔离结构用于限定pin光电二极管的阵列区域;

12.s3:在所述阵列区域中形成pin光电二极管;

13.s4:对锗供体晶圆的正面进行氢离子注入以在pin光电二极管下方的锗供体晶圆中形成氢注入层,pin光电二极管与介于所述氢注入层和pin光电二极管之间的锗层共同构成pin光电二极管层;

14.s5:在pin光电二极管层上形成第一互连层并在第一互连层上形成第一对准标记,其中第一互连层包括沟道和过孔;

15.s6:提供一硅电路晶圆,所述硅电路晶圆包括:用于控制和读取pin光电二极管的电路和至少一个第二互连层,其中第二互连层包括沟道和过孔,第二互连层上形成有第二对准标记,其中第二互连层形成于硅电路晶圆中;

16.s7:将第一对准标记对准于第二对准标记,进行第一互连层和第二互连层的初次键合以连接锗供体晶圆和硅电路晶圆;

17.s8:对步骤s7所形成的结构退火;

18.s9:通过切割和剥离所述氢注入层处使pin光电二极管层和第一互连层与锗供体晶圆分离;

19.s10:对步骤s9所形成的结构退火以完成第一互连层和第二互连层的最终键合。

20.优选地,步骤s2进一步包括:

21.s21:在锗供体晶圆的正面形成隔离沟道,相邻所述隔离沟道限定pin光电二极管的阵列区域;

22.s22:填充所述隔离沟道以使所述隔离沟道充满可流动电介质材料(flowable dielectric material),所述可流动电介质材料可流动电介质材料可以包括可流动氧化硅或氮化硅介质材料,例如可通过使用旋涂式介质材料(spin-on dielectric,sod)形成可流动介质膜。旋涂式介质材料诸如硅酸盐、硅氧烷、甲基倍半硅氧烷(msq)、氢倍半硅氧烷(hsq)、msq/hsq、全氢硅氮烷(tcps)或全氢聚硅氮烷(psz)、聚酰亚胺。除此之外,还可以通过使用低温等离子体化学汽相沉积形成可流动介电膜。可流动电介质材料能够填充窄而深的间隙并且防止sti(浅沟槽隔离)结构中的空隙和不连续性。

23.优选地,步骤s3进一步包括:

24.s31:在所述阵列区域中,在锗供体晶圆的正面形成第一掩模,未被第一掩模覆盖的区域为第一开放区域;对第一开放区域进行第一导电类型离子注入以在与第一开放区域相对应的锗供体晶圆的正面中形成第一导电类型掺杂区域,去除第一掩模并退火;

25.s32:在锗供体晶圆的正面形成第二掩模,未被第二掩模覆盖的区域为第二开放区域;对第二开放区域进行第二导电类型离子注入以在与第二开放区域相对应的锗供体晶圆

的正面中形成第二导电类型掺杂区域,去除第二掩模并退火,其中第一开放区域和第二开放区域完全不重叠,第一导电类型掺杂区域、第二导电类型掺杂区域以及介于第一导电类型掺杂区域和第二导电类型掺杂区域之间的本征区域共同构成pin(p型-本征-n型)光电二极管。

26.优选地,步骤s4中:

27.氢离子注入的剂量为1

×

10

15

atoms/cm2~1

×

10

18

atoms/cm2;优选地,氢离子注入的剂量至少为1

×

10

16

atoms/cm2;

28.和/或,氢离子注入的能量范围为1kev

–

1mev;

29.和/或,氢离子注入的执行温度范围为室温至600℃;优选地,氢离子注入的执行温度范围为室温至400℃;

30.和/或,氢注入层的深度精度为

±

0.03μm~

±

0.05μm。

31.优选地,步骤s3和步骤s4之间进一步包括:通过pecvd(等离子体增强化学气相沉积)在锗供体晶圆的正面形成注入保护层,所述注入保护层为二氧化硅层;

32.步骤s4中进一步包括:完成氢离子注入后去除所述注入保护层。

33.优选地,通过pecvd形成10nm~90nm的二氧化硅作为所述注入保护层,通过稀释hf或者缓冲氧化物刻蚀去除二氧化硅。

34.优选地,步骤s5中包括以下步骤:

35.s51:通过pvd在第一互连层的沟道和过孔的侧壁填充阻挡金属;

36.s52:通过pvd在第一互连层的沟道和过孔的侧壁形成铜种子;

37.s53:通过ecd在第一互连层的沟道和过孔中形成铜。

38.本发明的积极进步效果在于:通过引入互连层和氢离子注入,方便了硅电路晶圆和锗层的结合,并且在锗层中所形成气泡层又使得pin层的转移变得容易。且本发明的工艺步骤简单,不会造成像锗外延可能导致产生的晶格失配。

附图说明

39.图1-图8为本发明一实施例的在硅上形成锗器件的方法的工艺流程图。

40.图9a-图9c分别表示本发明一实施例的第二对准标记、第一对准标记和第一、第二对准标记相对准的图案。

具体实施方式

41.下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

42.本发明提供一种在硅上形成锗器件的方法,其在锗供体晶圆的正面形成隔离结构和pin光电二极管;进行氢离子注入以在pin光电二极管下方的锗供体晶圆中形成氢注入层,在pin光电二极管层上形成第一互连层,继而在硅电路晶圆上形成第二互连层,通过第一互连层和第二互连层的键合来在硅上形成锗器件。

43.进一步地,在pin光电二极管层上形成第一互连层之后,进一步包括提供一硅电路晶圆,在硅电路晶圆上形成包括用于控制和读取pin光电二极管的电路和至少一个第二互连层;进行第一互连层和第二互连层的初次键合以连接锗供体晶圆和硅电路晶圆;通过切

割和剥离所述氢注入层处使pin光电二极管层和第一互连层与锗供体晶圆分离;退火以完成第一互连层和第二互连层的最终键合。该方法工艺简单且避免了锗外延可能导致产生的晶格失配。

44.具体地,一种在硅上形成锗器件的方法,其包括以下步骤:

45.s1:提供一锗供体晶圆;

46.s2:在锗供体晶圆的正面形成隔离结构,所述隔离结构用于限定pin光电二极管的阵列区域;

47.s3:在所述阵列区域中形成pin光电二极管;

48.s4:对锗供体晶圆的正面进行氢离子注入以在pin光电二极管下方的锗供体晶圆中形成氢注入层,pin光电二极管与介于所述氢注入层和pin光电二极管之间的锗层共同构成pin光电二极管层;

49.s5:在pin光电二极管层上形成第一互连层并在第一互连层上形成第一对准标记,其中第一互连层包括沟道和过孔;

50.s6:提供一硅电路晶圆,所述硅电路晶圆包括:用于控制和读取pin光电二极管的电路和至少一个第二互连层,其中第二互连层包括沟道和过孔,第二互连层上形成有第二对准标记,其中第二互连层形成于硅电路晶圆中;

51.s7:将第一对准标记对准于第二对准标记,进行第一互连层和第二互连层的初次键合以连接锗供体晶圆和硅电路晶圆;

52.s8:对步骤s7所形成的结构退火;

53.s9:通过切割和剥离所述氢注入层处使pin光电二极管层和第一互连层与锗供体晶圆分离;

54.s10:对步骤s9所形成的结构退火以完成第一互连层和第二互连层的最终键合。

55.优选地,步骤s2进一步包括:

56.s21:在锗供体晶圆的正面形成隔离沟道,相邻所述隔离沟道限定pin光电二极管的阵列区域;

57.s22:填充所述隔离沟道以使所述隔离沟道充满可流动电介质材料(flowable dielectric material),所述可流动电介质材料可流动电介质材料可以包括可流动氧化硅或氮化硅介质材料,例如可通过使用旋涂式介质材料(spin-on dielectric,sod)形成可流动介质膜。旋涂式介质材料诸如硅酸盐、硅氧烷、甲基倍半硅氧烷(msq)、氢倍半硅氧烷(hsq)、msq/hsq、全氢硅氮烷(tcps)或全氢聚硅氮烷(psz)、聚酰亚胺。除此之外,还可以通过使用低温等离子体化学汽相沉积形成可流动介电膜。可流动电介质材料能够填充窄而深的间隙并且防止sti(浅沟槽隔离)结构中的空隙和不连续性。

58.优选地,步骤s3进一步包括:

59.s31:在所述阵列区域中,在锗供体晶圆的正面形成第一掩模,未被第一掩模覆盖的区域为第一开放区域;对第一开放区域进行第一导电类型离子注入以在与第一开放区域相对应的锗供体晶圆的正面中形成第一导电类型掺杂区域,去除第一掩模并退火;

60.s32:在锗供体晶圆的正面形成第二掩模,未被第二掩模覆盖的区域为第二开放区域;对第二开放区域进行第二导电类型离子注入以在与第二开放区域相对应的锗供体晶圆的正面中形成第二导电类型掺杂区域,去除第二掩模并退火,其中第一开放区域和第二开

放区域完全不重叠,第一导电类型掺杂区域、第二导电类型掺杂区域以及介于第一导电类型掺杂区域和第二导电类型掺杂区域之间的本征区域共同构成pin(p型-本征-n型)光电二极管。

61.优选地,步骤s4中:

62.氢离子注入的剂量为1

×

10

15

atoms/cm2~1

×

10

18

atoms/cm2;优选地,氢离子注入的剂量至少为1

×

10

16

atoms/cm2;

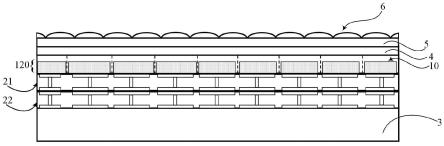

63.和/或,氢离子注入的能量范围为1kev

–

1mev;

64.和/或,氢离子注入的执行温度范围为室温至600℃;优选地,氢离子注入的执行温度范围为室温至400℃;

65.和/或,氢注入层的深度精度为

±

0.03μm~

±

0.05μm。

66.优选地,步骤s3和步骤s4之间进一步包括:通过pecvd(等离子体增强化学气相沉积)在锗供体晶圆的正面形成注入保护层,所述注入保护层为二氧化硅层;

67.步骤s4中进一步包括:完成氢离子注入后去除所述注入保护层。

68.优选地,通过pecvd形成10nm~90nm的二氧化硅作为所述注入保护层,通过稀释hf或者缓冲氧化物刻蚀去除二氧化硅。

69.优选地,步骤s5中包括以下步骤:

70.s51:通过pvd在第一互连层的沟道和过孔的侧壁填充阻挡金属;

71.s52:通过pvd在第一互连层的沟道和过孔的侧壁形成铜种子;

72.s53:通过ecd在第一互连层的沟道和过孔中形成铜。

73.优选地,步骤s6中包括以下步骤:

74.s61:通过pvd在第二互连层的沟道和过孔的侧壁填充阻挡金属;

75.s62:通过pvd在第二互连层的沟道和过孔的侧壁形成铜种子;

76.s63:通过ecd在第二互连层的沟道和过孔中形成铜。如果有多余的铜超出硅层或者锗层,那么需要去除这些超出表面的铜。阻挡金属例如钛/氮化钛(ti/tin)或钽/氮化钽(ta/tan),用于阻止铜扩散进电介质中。

77.优选地,步骤s7中包括:

78.s71:清洁第一互连层的待键合表面和第二互连层的待键合表面;

79.s72:将第一对准标记对准于第二对准标记,使得第一互连层的待键合表面和第二互连层的待键合表面相贴合;

80.s73:对锗供体晶圆和/或硅电路晶圆施加压力以完成第一互连层和第二互连层的初次键合。

81.优选地,步骤s8中退火温度为100℃~200℃,

82.和/或,步骤s10中退火温度为小于等于310℃。

83.优选地,步骤s9中通过能量源脉冲来剥离所述氢注入层处,能量源为热源、冷源或机械力源。

84.优选地,步骤s9中被剥离的表面的粗糙度小于60nm。被剥离的表面包括锗供体晶圆的自氢注入层处被剥离的表面以及pin光电二极管层的自氢注入层处被剥离的表面。

85.优选地,步骤s10之后进一步包括:抛光pin光电二极管层的被剥离的表面。

86.优选地,步骤s10之后进一步包括:

87.s11:在pin光电二极管层上形成减反射层,用于增强光的传播并且减少表面反射。

88.优选地,步骤s11之后进一步包括:在所述减反射层上形成滤波层(用于选择性地使得特定波长的光透过)和棱镜层,其用于改善光的聚焦并将其引导至相应的像素点,由此减少光串扰以及噪声。

89.下面参考图1-图9c,以cmos(互补型金属氧化物半导体)图像传感器为例,介绍本发明一实施例的在硅上形成锗器件的方法。

90.参考图1,首先提供一锗供体晶圆101,并在锗供体晶圆的正面形成隔离结构11,所述隔离结构用于限定pin光电二极管的阵列区域。具体来说,在锗供体晶圆的正面形成隔离沟道,相邻所述隔离沟道限定pin光电二极管的阵列区域,之后再填充所述隔离沟道以使所述隔离沟道充满可流动电介质材料,例如聚酰亚胺。可流动电介质材料能够填充窄而深的间隙并且防止sti结构中的空隙和不连续性。

91.接着参考图2,在所述阵列区域中形成pin光电二极管12。形成pin光电二极管的具体手段为:在所述阵列区域中,在锗供体晶圆的正面形成第一掩模,未被第一掩模覆盖的区域为第一开放区域;对第一开放区域进行第一导电类型离子注入(例如p+注入)以在与第一开放区域相对应的锗供体晶圆的正面中形成第一导电类型掺杂区域(n型掺杂区域),去除第一掩模并退火;接着在锗供体晶圆的正面形成第二掩模,未被第二掩模覆盖的区域为第二开放区域;对第二开放区域进行第二导电类型离子注入(例如b+注入)以在与第二开放区域相对应的锗供体晶圆的正面中形成第二导电类型掺杂区域(p型掺杂区域),去除第二掩模并退火,其中第一开放区域和第二开放区域完全不重叠,第一导电类型掺杂区域、第二导电类型掺杂区域以及介于第一导电类型掺杂区域和第二导电类型掺杂区域之间的本征区域共同构成pin光电二极管。每次完成离子注入之后都需要退火,以激活掺杂元素。

92.之后通过pecvd形成例如10nm~90nm的二氧化硅作为所述注入保护层,以在之后的氢离子注入中保护锗供体晶圆。

93.接下来,参考图3,对锗供体晶圆的正面进行氢离子注入以在pin光电二极管12下方的锗供体晶圆中形成氢注入层13,pin光电二极管12与介于所述氢注入层13和pin光电二极管12之间的锗层10共同构成pin光电二极管层,以120表示。

94.其中,氢离子注入的剂量为5

×

10

16

atoms/cm2,注入能量为150kev,注入温度为室温,氢注入层的深度精度在

±

0.05μm。注入至锗供体晶圆的氢离子会捕获电子以形成氢气,由此氢注入层13也可以理解为气泡层(blistering layer)气泡层中有氢气形成的微气泡。完成氢离子注入后,通过稀释hf或者缓冲氧化物刻蚀去除二氧化硅。

95.下面分别参考图4和图5,在pin光电二极管层120上形成第一互连层21并在第一互连层21上形成第一对准标记,其中第一互连层包括沟道和过孔。以及提供一硅电路晶圆3,所述硅电路晶圆3包括:用于控制和读取pin光电二极管的电路(图中未示出)和至少一个第二互连层22,其中第二互连层22包括沟道和过孔,第二互连层上形成有第二对准标记。在这一实施例中,第二互连层形成于硅电路晶圆3中。

96.本实施例中,由于第一互连层和第二互连层采用了相同的设计,所以下面仅描述第一互连层的形成方式。第一互连层具有“工”字形截面,其包括沟道和过孔,沟道位于“工”字的两端,而过孔则连接两端沟道。当然,除了“工”字型结构之外,本领域技术人员还可以采用其他构造的互连层形式。具体来说,首先通过pvd在第一互连层的沟道和过孔的侧壁填

充阻挡金属,例如钛/氮化钛。接着通过pvd在第一互连层的沟道和过孔的侧壁形成铜种子(cu seeds),在阻挡金属的保护下,铜不会扩散进电介质中。随后通过ecd在第一互连层的沟道和过孔中形成铜。

97.接着参考图6,将第一对准标记对准于第二对准标记,进行第一互连层和第二互连层的初次键合以连接锗供体晶圆和硅电路晶圆。其中,第一对准标记和第二对准标记的形成通过现有手段实现,图9a-图9c分别示出了一种典型的对准标记的形式和对准的情况,例如图9b表示第一对准标记,图9a表示第二对准标记,而图9c则示出了第一对准标记和第二对准标记相对准的情况。本领域技术人员还可以采用其他形式的对准标记。

98.在一较佳实施例中,清洁第一互连层和第二互连层的待键合表面。

99.将对准标记对准之后,对锗供体晶圆和/或硅电路晶圆施加压力以完成第一互连层和第二互连层的初次键合。压力的大小需要被控制,以确保注入氢离子后形成的微气泡不会导致破裂,以及氢气不扩散或者溢出漏气。接着对图6所示结构退火,例如在100~200℃下退火。

100.参考图7,通过剥离所述氢注入层13处使pin光电二极管层120和第一互连层21与锗供体晶圆1分离,之后退火以完成第一互连层21和第二互连层22的最终键合。具体来说,通过能量源脉冲来剥离所述氢注入层处,能量源为热源、冷源或机械力源,且被剥离的表面的粗糙度小于60nm,之后抛光pin光电二极管层的被剥离的表面。之后通过在小于等于310℃的条件下退火来完成最终键合。

101.之后参考图8,在pin光电二极管层120上形成减反射层4,以及在所述减反射层4上形成滤波层5和棱镜层6,由此完成锗器件的制作。其中,减反射层4能够增强光的传播并且减少表面反射,滤波层5则是用于选择性地使得特定波长的光透过,而棱镜层6则用于改善光的聚焦并将其引导至相应的像素点,由此减少光串扰以及噪声并由此改善cmos图像传感器的填充因子,提高光的吸收。

102.即使在可见光波长下(0.4μm

–

0.75μm),锗的光吸收率也比硅高,并且波长吸收延伸至1.6μm,其性能与砷化铟镓相当。本发明所述的基于锗的短波红外cmos图像传感器可捕获来自可见光和更远波长(直到1.6μm波长)的图像。利用本发明所公开的方法,将优质锗层从单晶锗供体晶圆转移到硅目标晶圆,与在硅目标晶圆上直接外延生长锗相比,具有更高的质量和更少的缺陷。

103.虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这些仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1