一种界面相变存储材料、相变存储器及其制备方法

1.本发明属于微电子技术领域,特别涉及一种界面相变存储材料、相变存储器及其制备方法。

背景技术:

2.随着大数据时代的到来,人工智能、云计算和5g技术的迅速兴起,加快了信息数据的产出,导致数据呈现爆炸式的增长。人们对于海量数据的存储和处理能力要求不断提高。相变存储器作为新型非易失性存储技术拥有数据容量大、读写速度快、操作功耗低以及微缩性好等优势,有望填补动态随机存储器与闪存存储架构的性能空白成为下一代信息存储技术。

3.以硫系化合物为核心存储介质的相变存储器,通过相变存储介质高低阻态的变化实现数据的存储。硫系化合物存储介质具有晶态和非晶态两种材料结构,这两者之间因为原子排布的不同展现出巨大的阻值差异。晶态时表现出低电阻值,此时材料具有高反射率,非晶态时表现出高电阻值,材料具有低反射率。ge2sb2te5(gst)是研究最多,技术最为成熟并被广泛应用的相变存储材料。但同时它如下的缺点也限制了它的进一步发展:转换速度慢、功耗高、电阻漂移系数大,这导致它难以应用在低功耗以及高密度存储中。单一的gst材料已经不能满足相变存储器的发展需求,人们开始寻找新型相变材料替代gst材料。

4.常见的相变材料有ge-sb-te体系、sb-te二元体系以及ge-te体系。研究人员通常会寻找合适的元素将其掺入上述相变材料体系中。但掺杂方式在工艺的可靠性、纳米尺度下元素掺杂的均匀性及多次循环操作后产生的分相等问题上面临着一系列挑战。因此,近些年来人们将眼光更多投入到转换速度更快、功耗更低的基于sb2te

3-gete超晶格材料的界面相变存储器当中,不过有研究表明该超晶格结构的稳定性严重依赖于gete晶态材料,而gete材料层对结构的形变敏感,稳定性较差,ge原子在热效应作用下通常发生明显的层间原子扩散,造成材料中局部原子配比失衡导致器件失效(janne kalikka et al.nature communicatio n.10.1038/ncomms11983)。另外,已公开专利中提出的多层相变材料具有相对复杂的制备工艺,薄膜的形成需要经历化学气相沉积和物理气相沉积等多种生长方式,制造成本将会大大增加(专利:二维材料改良的超晶格相变薄膜、相变存储器及制备方法,cn110556476a)。

技术实现要素:

5.本发明所要解决的技术问题是提供一种界面相变存储材料、相变存储器及其制备方法,以克服现有技术中相变存储材料功耗高、电阻漂移系数大等缺陷。

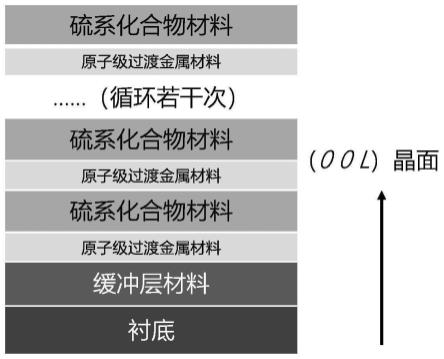

6.本发明提供一种界面相变存储材料,其特征在于,包括范德华结构缓冲层以及过渡金属层与相变材料层交替堆叠组成的超晶格相变存储层,所述超晶格相变存储层位于所述德华结构缓冲层上。

7.优选地,所述范德华结构缓冲层厚度为5~10nm,材料为具有范德华及六方结构的

二维硫系化合物,这种结构的材料具备垂直于衬底的面外高度(0 0l)结构取向。

8.优选地,所述二维硫系化合物包括sb2te3、bi2te3中的一种或几种。

9.优选地,所述超晶格相变存储层厚度为40~100nm。

10.优选地,所述过渡金属层厚度为0.5~2nm,材料为过渡金属元素。

11.优选地,所述过渡金属元素包括ti、mo、w、zr、hf、v、nb、pt、ta中的一种或几种。

12.优选地,所述相变材料层厚度为3~10nm,材料为硫系化合物。

13.优选地,所述硫系化合物材料包括sb2te3、sb2te、bi2te3中的一种或几种。

14.优选地,所述超晶格相变存储层用于提供界面相变存储材料的可生长面外高度(0 0 l)结构取向。

15.优选地,所述界面相变存储材料具有面外高度(0 0 l)结构取向。

16.优选地,所述界面相变存储材料以薄膜形式存在。

17.本发明还提供一种界面相变存储材料的制备方法,包括:

18.提供一衬底,在所述衬底上生长范德华结构缓冲层,在所述范德华结构缓冲层上交替生长过渡金属层和相变材料层,得到界面相变存储材料。

19.优选地,所述衬底包括单晶硅、碳化硅、氮化镓、聚酰亚胺、聚对苯二甲酸乙二醇酯及蓝宝石衬底中的一种或几种。

20.优选地,生长的方式包括:原子层沉积、化学气相沉积、磁控溅射、脉冲激光沉积或分子束外延法。

21.优选地,所述交替生长过渡金属层和相变材料层采用磁控溅射,所述磁控溅射的工艺参数为:在氩气环境中通过交替溅射相应靶材,靶材纯度大于99.99%,本底真空度小于2

×

10-5

pa,溅射腔温度为200~350℃,氩气流量为10~50sccm,溅射气压为0.1~0.6pa。

22.优选地,交替生长过渡金属层和相变材料层5~20个周期。

23.本发明还提供一种相变存储器,其特征在于,包括底电极层、上述界面相变存储材料、顶电极层,所述底电极层位于所述界面相变存储材料的下方,所述顶电极层位于所述界面相变存储材料的上方。

24.优选地,所述顶电极层厚度为50~300nm,材料包括tin、w、al、ti、au、pt、tisin、c种的一种或几种。

25.本发明还提供一种相变存储器的制备方法,包括:

26.提供带有底电极层的基片,在基片上生长上述范德华结构缓冲层,在所述缓冲层上生长上述超晶格相变存储层,在所述晶格相变存储层上生长顶电极层。

27.优选地,所述生长的方式包括原子层沉积、化学气相沉积、磁控溅射、脉冲激光沉积或分子束外延法。

28.本发明还提供一种相变存储器的应用。

29.本发明相变存储材料具有特定晶面生长取向,在电脉冲作用下能够发生非晶态-晶态的转换。随着结构中非晶态与晶态比例的不同形成不同阻态的中间体,且这些中间体在常温下能够稳定存在。

30.有益效果

31.本发明界面相变存储材料中过渡金属x与相变材料中的te原子结合形成x-te化合物,构建了一种原子级厚度的界面层,该界面层有利于相变材料的层状堆叠,提升其结晶速

度和器件操作的稳定性。基于界面相变存储材料制备的相变存储器件在电压脉冲下发生非晶态与晶态转换时,x-te化合物界面层不会被破坏,有效限制相变材料晶粒纵向生长,细化了晶粒。器件复位过程中由于非晶态和晶态的比例不同,存在多个不同阻值的中间态,这些中间电阻态能够稳定存在且没有明显的电阻漂移。基于该界面效应调控的相变存储器件具有高速低功耗、高密度存储、低电阻漂移的优势。有望应用于神经形态器件及高密度存储领域。

附图说明

32.图1为本发明相变存储材料的结构示意图。

33.图2为本发明相变存储材料的制备方法流程示意图((a)~(e))。

34.图3为本发明相变存储器件的制备方法流程示意图((a)~(c))。

35.图4为实施例1中相变存储薄膜的x射线衍射图谱。

36.图5为实施例2中基于界面效应调控的相变存储器在不同电学脉冲作用下,器件单元电阻随电压脉冲变化曲线(r-v曲线)。

37.图6为对比例1中基于sb2te3材料的相变存储器在不同电学脉冲作用下,器件单元电阻随电压脉冲变化曲线(r-v曲线)。

38.图7为实施例2中基于界面效应调控的相变存储器的器件单元循环擦写疲劳特性曲线。

39.图8为实施例2中基于界面效应调控的相变存储器多种中间态电阻值随时间变化的关系(r-t)。

具体实施方式

40.下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本技术所附权利要求书所限定的范围。

41.实施例1

42.一种界面调控的多层结构薄膜,结构包括:

43.范德华缓冲层(102);

44.相变存储材料层:由过渡金属mo(103)与sb2te3(104)合金交替沉积8个周期组成。

45.制备方法:

46.如图2(a)所示,提供一衬底(101),本实例所用衬底为硅片,将硅片置于丙酮、酒精溶液依次在超声波作用下清洗10min;去离子水冲洗30s后n2吹干,再将衬底放置在80℃的烘箱中烘20min。

47.如图2(b)所示,采用磁控溅射法在硅片上沉积一层厚度为5nm厚的sb2te3缓冲层(102)。

48.如图2(c-d)所示,在缓冲层(102)上采用磁控溅射法交替沉积mo(103)与sb2te3(104)8个周期,其中mo层厚度为sb2te3层厚度为5nm。

49.在该实例中,mo靶材及sb2te3靶材纯度大于99.99%。氩气纯度超过99.999%。溅射

条件为:溅射腔温度300℃,本底真空优于2

×

10-5

pa,mo靶的溅射功率为30w,sb2te3靶溅射功率为30w,氩气流量25sccm,溅射气压0.55pa。

50.在该实例中,薄膜沉积完成后,关闭加热台,样品置于反应腔中冷却至室温,防止薄膜氧化。

51.如图4所示,通过薄膜x射线衍射结果可以发现薄膜具有高度(0 0l)结构取向。在相变存储器中采用该薄膜能够更快的完成开关操作。过渡金属mo与相变材料中的te原子结合形成mo-te化合物,构建了一层原子级的界面层,有助于sb2te3晶体的快速层状堆叠,提升其结晶速度和效率。

52.实施例2

53.如图3所示,一种相变存储单元,其结构包括:

54.带有底电极基片(201);

55.sb2te3缓冲层(202);

56.原子级厚度的mo与sb2te3组成的多层结构薄膜(203);

57.顶电极层(204)。

58.制备方法如下:

59.使用提供带有底电极的基片(201),将硅片置于丙酮、酒精溶液依次在超声波作用下清洗10min去除表面的油污粉尘;再用去离子水冲洗进行二次清洁,最后烘干基片。

60.在基片上生长5nm厚sb2te3缓冲层(202)及6个周期的mo-sb2te3多层结构薄膜(203),其中mo层厚sb2te3层厚5nm。

61.上述薄膜采用磁控溅射法制备,溅射条件与实例1中相同,不再过多赘述。

62.冷却至室温后,通过溅射方法生长顶电极(204),本实例中采用的顶电极为tin,厚度为50nm。

63.顶电极溅射条件:采用tin合金靶,纯度大于99.999%,溅射功率60w、本底真空度2

×

10-5

pa,溅射气压0.55pa。

64.对沉积完成的基片进行涂布光刻胶,该涂胶方式可以为旋涂、滚涂或刮涂。

65.完成涂胶后,对基片进行烘干处理。烘干条件为:温度80℃,时间20min。

66.采用紫外曝光及显影操作图形化相变存储单元,并将基片置于加热板上120℃后烘10min。

67.结合图3所示,采用干法刻蚀工艺去除多余的顶电极及相变薄膜,得到分立的器件单元。

68.刻蚀分为两步,第一步刻蚀掉多余tin顶电极层(图3b),刻蚀条件为:本底真空度1

×

10-5

pa、刻蚀功率200w、刻蚀时间4min。第二步刻蚀相变材料层(图3c),刻蚀条件为:本底真空度1

×

10-5

pa、刻蚀功率200w、刻蚀时间90s。该种刻蚀方法具有刻蚀速度快、刻蚀形貌好、刻蚀损伤小和适用范围广的优点。

69.基片刻蚀完以后去除光刻胶阻挡层,基片置于丙酮溶液5min溶解光刻胶,再使用酒精溶液浸泡5min除去基片上的丙酮残液。最后用去离子水清洗干净后放置烘箱中烘干。

70.刻蚀结束后,未被光刻胶覆盖区域将会形成深孔,可对其沟道中生长sio2进行填充(205),将多余的sio2进行刻蚀或抛光处理,如图3(d)所示。

71.将制备好的相变存储器件通过探针或导线连接到电学测试系统中,加载电学脉冲

信号能够诱导mo与sb2te3相变材料发生非晶态-晶态的可逆转换,从而测试相变存储器件的读写、疲劳、以及各中间电阻态稳定性,研究该结构下相变存储器件的性能。

72.如图5所示,基于界面效应调控的相变存储器电阻-电压关系图。为确保数据的可靠性,每个脉冲宽度下的结果都是经过多次测量取得平均值。将高阻态视为器件的复位(reset)状态,低阻态视为的置位(set)状态,在电压脉冲的作用下器件可以快速的完成set过程,器件电阻出现数量级的减小,reset过程则是电阻态逐步升高的过程,存在多个中间电阻态。随着施加脉冲宽度的减小,器件所需的reset电压变得更高,6ns时需要近6.7v。本发明提供的相变材料制备的器件具有高速低功耗的优点。

73.如图7所示,基于界面效应调控的相变存储器的疲劳特性曲线,通过对器件存储单元施加电脉冲完成r-v窗口,设置合适的擦脉冲和写脉冲宽度得到器件的疲劳特性,本发明中的相变存储器在高低两个电阻态之间稳定操作超过4

×

105次。

74.如图8所示,基于界面效应调控的相变存储器的电阻漂移特性。在r-v测试过程中当器件处于reset状态时暂停脉冲的施加,于室温下测量电阻阻值随时间的变化特性,本发明中制备的相变存储器件具有低的漂移系数,多个(8个)中间态都可稳定存在,提高了器件的稳定性。在不增加工艺复杂度和成本的基础上,在一个单元中存储多比特数据,有助于提高相变存储器的存储密度,有望于应用于多级存储及神经形态器件当中。

75.对比例1

76.一种相变存储单元,其结构与实施例2相同,由底电极基片、相变材料层、顶电极构成。其中的相变材料层为sb2te3。

77.采用与实施例2中相同的制备方法:300℃条件下,利用磁控溅射法在底电极基片上沉积40nm厚的sb2te3。顶电极层为50nm厚的tin。

78.对制备好的器件进行电学性能测试。测试结果如图6所示。相较于本发明所提供的相变存储材料,sb2te3在重置(reset)过程中所需的电压更高,功耗也更高。且以sb2te3作为相变材料的器件普遍存在稳定性较差、相变过程中容易形成较大晶粒造成器件失效的问题。

79.上述实例仅示例说明本发明的原理及应用,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实例进行修改或改变。相关技术领域人员在未脱离本发明所揭示的精神及技术思想下完成的修饰及改变,仍应有本权利的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1