电子装置的制作方法

1.本案是为一种电压调节模块,尤指一种可减少厚度的电压调节模块。

背景技术:

2.请参阅图1a及图1b,其中图1a为第一种现有电子装置的结构示意图,图1b为图1a所示的电压调节模块的结构示意图。如图1a及图1b所示,现有电子装置1包含中央处理器(central processing unit;cpu)11、电压调节模块(voltage regulator module;vrm)12、系统板13。电压调节模块12用以转换所接收的输入电压为调节电压,并提供给中央处理器11,且电压调节模块12与中央处理器11设置于系统板13的相对表面上,即电压调节模块12设置于系统板13的底面上,中央处理器11设置于系统板13的顶面上,进而使电子装置1形成垂直供电结构,如此一来,可减小电压调节模块12的输出电压端与中央处理器11的供电输入端之间的传输距离,减小能量传输路径上的线阻,进而提升负载动态切换的性能。此外,电压调节模块12更具有印刷电路板15及磁性组件16。磁性组件16可为电感,且设置于印刷电路板15上,此外,在印刷电路板15和磁性组件16之间的空隙里可设置开关电路,使得开关电路与磁性组件16实际上为上下叠放关系,借此减少电压调节模块1在水平方向上的占用面积。

3.然由于目前对于系统板13的功率密度要求越来越高,且对于系统板1的厚度要求也越来越薄,因此留给电压调节模块12的厚度尺寸也越来越小,例如需小于5mm,甚至小于或等于3mm,如此一来,现有电子装置1内的电压调节模块12的开关电路和磁性组件16上下叠放的技术便因为厚度的限制而不符合需求。

4.因此,实有必要发展一种电压调节模块及其适用的电压调节装置,以解决先前技术所面临的问题。

技术实现要素:

5.本案的目的为提供一种电压调节模块及其适用的电压调节装置,其是可达到减少厚度尺寸的功效。

6.为达上述目的,本案的一实施态样为提供第一种电压调节模块,包含:印刷电路板组件,包含印刷电路板以及2n个开关电路,印刷电路板的内部具有至少一导电结构,印刷电路板具有第一方向和第二方向;以及磁性组件,包含上磁盖,下磁盖以及2n个边柱,2n个边柱位于上磁盖及下磁盖之间,2n个边柱分别穿过对应的导电结构,并与上磁盖、下磁盖以及导电结构相互配合形成2n个电感,其中2n个边柱上的直流磁通方向相同,且n为正整数;其中,每一开关电路与磁性组件中对应的电感电连接,每2个开关电路并联电连接,且沿第二方向排放并构成开关电路组合,n个开关电路组合和磁性组件沿第一方向放置。

7.为达上述目的,本案的另一实施态样为提供第二种电压调节装置,包含:多个如第一种所述的电压调节模块,其中该多个电压调节模块并联连接,且该多个电压调节模块错相控制。

附图说明

8.图1a为第一种现有电子装置的结构示意图;

9.图1b为图1a所示的电压调节模块的结构示意图;

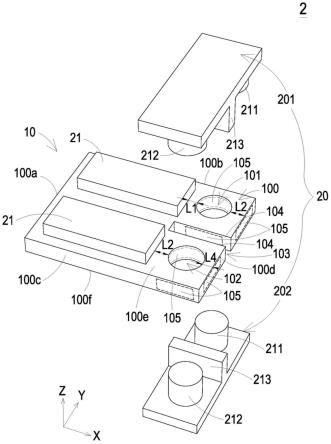

10.图2为本案第一较佳实施例的电压调节模块的爆炸结构示意图;

11.图3a为图2所示的电压调节模块所构成的第一实施例的等效电路图;

12.图3b为图2所示的电压调节模块所构成的第二实施例的等效电路图;

13.图4为图2所示的磁性组件组接扣合时的结构示意图;

14.图5为图3a-图3b所示的2个电感上的电流的流动方向示意图;

15.图6为本案第二较佳实施例的电压调节模块的爆炸结构示意图;

16.图7a为本案第三较佳实施例的电压调节模块的部分结构示意图;

17.图7b为本案第四较佳实施例的电压调节模块的部分结构示意图;

18.图8为本案第五较佳实施例的电压调节模块的部分结构示意图;

19.图9为本案第六较佳实施例的电压调节模块的爆炸结构示意图;

20.图10为图9所示的电压调节模块的等效电路图;

21.图11为图10所示的4个电感上电流流动时的方向示意图;

22.图12为本案第七较佳实施例的电压调节模块的爆炸结构示意图;

23.图13为本案较佳实施例的电压调节装置的结构示意图。

具体实施方式

24.体现本案特征与优点的一些典型实施例将在后段的说明中详细叙述。应理解的是本案能够在不同的态样上具有各种的变化,其皆不脱离本案的范围,且其中的说明及图式在本质上是当作说明之用,而非用于限制本案。

25.请参阅图2、图3a及图3b,其中图2为本案第一较佳实施例的电压调节模块的爆炸结构示意图,其中方向x定义为第一方向,方向y定义为第二方向,方向z定义为第三方向,以下图示中的立体结构示意图皆为如此定义,不再赘述。图3a为图2所示的电压调节模块所构成的第一实施例的等效电路图,图3b为图2所示的电压调节模块所构成的第二实施例的等效电路图。如图所示,本实施例的电压调节模块2可应用在电子装置内,并与电子装置内的系统板(未图标)以焊接方式连接。其中图2所示电压调节模块2可构成图3a或图3b所示的电路结构,而在电压调节模块2所构成的其中的一种电路结构上,即如图3a所示,电压调节模块2包含2个单相降压电路、至少一输入电容cin、输出电容cout。其中2个单相降压电路分别包含具有驱动器及开关元件的驱动器开关单元21(后面简称开关电路21)及电感l,换言之,即电压调节模块2包含2个开关电路21及2个电感l。于一些实施例中,每个开关电路21包含至少2个开关元件,该至少2个开关元件串联电气连接。

26.每一开关电路21串联连接于对应的电感l的第一端sw而构成单相降压电路,2个单相降压电路并联连接而构成2相降压电路。每个开关电路21具有3个端口,分别为第一端、第二端、第三端。2个开关电路21的第一端并联电性连接后与电压调节模块2的输入电容cin电性连接,以构成电压调节模块2的正输入端vin+。2个开关电路21的第二端并联电性连接后与电压调节模块2的输入电容cin的负端电性连接,以构成电压调节模块2的负输入端vin-。而2个开关电路21的第三端分别电性连接该2个电感l的一端(即第一端sw),且2个电感l的

另一端并联电性连接后与输出电容cout的第一端电性连接,以构成电压调节模块2的正输出端vo+。输出电容cout的第一端可构成电压调节模块2的正输出端vo+,输出电容cout的第二端可构成电压调节模块2的负输出端vo-,其中负输入端vin-与负输出端vo-电连接。输入电容cin的第一端是与电压调节模块2的正输入端vin+电性连接,输入电容cin的第二端是与电压调节模块2的负输入端vin-电性连接。

27.而在电压调节模块2所构成的另一电路结构上,如图3b所示,电压调节模块2包含2个开关电路21、2个电感l、2个储能电容cp、输入电容cin及输出电容cout。每个开关电路21具有4个端口,分别为第一端、第二端、第三端和第四端,此外,开关电路21的第一端并联电性连接后与电压调节模块2的输入电容cin的正端电性连接,以构成电压调节模块2的正输入端vin+,而2个开关电路21的第二端并联电性连接后与电压调节模块2的输入电容cin的负端电性连接,以构成电压调节模块2的负输入端vin-,该2个开关电路21的第三端分别电性连接该2个储能电容cp的一端,2个开关电路21的第四端分别电性连接该2个储能电容cp的另一端,并与该2个电感l的一端电性连接,2个电感l的另一端并联电性连接后与输出电容cout的第一端电性连接,以构成电压调节模块2的正输出端vo+。输出电容cout的第一端可构成电压调节模块2的正输出端vo+,输出电容cout的第二端可构成电压调节模块2的负输出端vo-。输入电容cin的第一端是与电压调节模块2的正输入端vin+电性连接,输入电容cin的第二端是与电压调节模块2的负输入端vin-电性连接,其中负输入端vin-与负输出端vo-电连接,且为短路相接。

28.于一些实施例中,构成图3a或图3b的电压调节模块2的开关电路21包含晶体管开关及用来驱动晶体管开关的驱动器。电压调节模块2还包含控制电路11,控制电路11通过采样电压调节模块2的输出电压和所需的电流而产生两组脉宽控制信号pwm1及pwm2,其中两组脉宽控制信号pwm1及pwm2错相180度,且脉宽控制信号pwm1用来控制其中的一开关电路21,脉宽控制信号pwm2用来控制另一开关电路21,于另一实施例中,该2个脉宽控制信号pwm1和pwm2错相相位差为[150,210]度范围内任一值,例如错相180度。此外,于其它实施例中,输出电容cout可设置于电压调节模块2内,但不以此为限,亦可设置于电子装置内的系统板上。

[0029]

在本实施例中,电压调节模块2的实体结构为包含印刷电路板组件10及磁性组件20。印刷电路板组件10包含印刷电路板100及2个开关电路21。印刷电路板100内部具有由印刷电路板平面绕组(由印刷电路板100内的布线所形成)所构成的至少一导电结构(未图示),且印刷电路板100包含4个侧边,即为相对的第一侧边100a与第二侧边100d,及位于第一侧边100a与第二侧边100d之间且为相对的第三侧边100b以及第四侧边100c,此外,印刷电路板100亦包含为相对的上表面100e以及下表面100f。电压调节模块2的电容组合,例如图3a所示的包含输入电容cin的电容组合,或是图3b所示的包含输入电容cin和储能电容cp的电容组合可以通过焊锡焊接方式或者导电胶黏贴方式设置下表面100f上(例如图7a-图7b所示)。2个开关电路21可为但不限于以焊锡焊接方式或者导电胶黏贴方式设置于印刷电路板100的上表面100e上,且2个开关电路21为沿第二方向邻近放置而构成1个开关电路组合,该开关电路组合贴合印刷电路板100的第一侧边100a、第三侧边100b及第四侧边100c放置。2个开关电路21的第一端并联,且第二端亦并联,并分别构成该开关电路组合的第一端和第二端,且共用一组输入电容cin。在本实施例中,输入电容cin邻近开关电路组合的第一

端放置,且放置于印刷电路板100的下表面100f,因此使得该2个开关电路21与输入电容cin之间寄生参数最小。于一实施例中,该开关电路组合的第一端可以对应到每个开关电路21的第一端所对应的脚位,也可以对应到连接该2个开关电路21的第一端所对应脚位的电气路径中的任一点。而由上可知,输入电容cin和开关电路乃沿第三方向分别设置于导电结构的上侧或下侧。

[0030]

于一实施例中,该2个开关电路21的控制信号错相相位差为[150,210]度范围内任一值,例如错相180度,输入电容cin的纹波电流频率是电压调节模块2的开关频率的2倍,从而使得输入电容cin的纹波电流小,输入电容cin上的损耗降低,更可以使用小尺寸的输入电容cin,以此来减小电压调节模块2的体积。

[0031]

此外,于另一实施例中,图3b所示的所述储能电容cp分别邻近一开关电路21的第三端和另一开关电路21的第四端所对应的脚位放置,且放置于印刷电路板100的下表面100f,因此,使得该2个开关电路21与储能电容cp之间寄生参数最小,储能电容cp的损耗降低。

[0032]

磁性组件20包含上磁盖201以及下磁盖202,边柱211和212以及中柱213,其中上磁盖201设置于印刷电路板100的上表面100e上,下磁盖202与上磁盖201相对应地设置于印刷电路板100的下表面100f上,边柱211和212以及中柱213设置于上磁盖201和下磁盖202之间,此外,边柱211和212以及中柱213穿过印刷电路板100内的对应的平面绕组,并与上磁盖201以及下磁盖202相互配合而形成2个电感l,其中2个电感l为磁集成电感,借此缩小2个电感l的体积。每1个电感l与每个开关电路21电连接。此外,该2个电感l构成一电感组,该电感组与该开关电路组合采用水平布局方式设置于印刷电路板100上,即该电感组与该开关电路组合沿第一方向依次设置于印刷电路板100上。

[0033]

由上述内容可知,由于本实施例的电压调节模块2内的2个电感l与2个开关电路21乃是采用水平布局方式设置于印刷电路板100上,因此相比现有电子装置内的电压调节模块的开关电路和磁性组件为上下叠放,本实施例的电压调节模块2的高度大幅下降,更甚者,由于本实施例的电压调节模块2的2个电感l为磁集成电感,故2个电感l的体积可减小,使得本实施例的电压调节模块2的体积和高度可再进一步缩小,因此本实施例的电压调节模块2的厚度整体可小于或等于5mm,甚至小于或等于3mm,以符合薄型化的应用需求。另外,2个电感l与2个开关电路21沿第一方向紧密摆放,而电容组合放在印刷电路板100的下表面100f和2个开关电路21对应的位置,使得2个邻近放置且错相180度控制的开关电路21,可和输入电容cin之间寄生参数最小外,和/或可和储能电容cp之间寄生参数最小,从而降低输入电容cin和储能电容cp的损耗,使得整个产品的尺寸也进一步减小。故本案的电压调节模块2可达到薄型化、小封装面积和高功率密度的优势。

[0034]

于一些实施例中,为了形成电压调节模块2的2个电感l,磁性组件20的2个边柱211、212是分别部分形成于上磁盖201上,2个边柱211、212其余部分则分别形成于下磁盖202上,此外,印刷电路板100亦对应包含2个孔洞101、102,其中孔洞101、102分别位于对应的开关电路21及第二侧边100d之间,且贯穿印刷电路板100,此外,孔洞101的位置与边柱211的位置相对应,孔洞102的位置与边柱212的位置相对应,当上磁盖201设置于印刷电路板100的上表面100e而下磁盖202设置于印刷电路板100的下表面100f时,边柱211便穿设孔洞101而容置于印刷电路板100内,并与印刷电路板100内对应的平面绕组形成电压调节模

块2的其中的一电感l,边柱212同样穿设孔洞102而容置于印刷电路板100内,并与印刷电路板100内对应的平面绕组形成电压调节模块2的另一电感l。另外,形成2个电感l的印刷电路板100内的每一平面绕组可相对于印刷电路板100的第一侧边100a而较为邻近于第二侧边100d、第三侧边100b及第四侧边100c,即磁性组件20贴合印刷电路板100的第二侧边100d、第三侧边100b及第四侧边100c放置。

[0035]

另外,为了避免构成电感l的印刷电路板100的平面绕组与开关电路21之间的传导路径过长而产生较大的电能损耗,较佳者,孔洞101与对应的开关电路21之间的最短距离l1可小于孔洞101与第二侧边100d之间的最短距离l2,孔洞102与对应的开关电路21之间的最短距离l3小于孔洞102与第二侧边100d之间的最短距离l4,以使2个电感l分别与对应的开关电路21相邻设。

[0036]

更甚者,因为电压调节模块2尺寸的限制,在印刷电路板100内所放置的平面绕组的宽度将受限,导致所述平面绕组的线阻增大而造成一定的能量损耗,故为了避免此情况发生,在一些实施例中,可将形成电感l的印刷电路板的平面绕组所邻近的第二侧边100d、第三侧边100b及第四侧边100c的壁面以及印刷电路板100的2个孔洞101、102的内侧壁面进行板边电镀而分别形成至少一电镀区105,电镀区105可与印刷电路板100中多层平面绕组中至少一平面绕组电气连接,故电镀区105可于第二侧边100d、第三侧边100b、第四侧边100c以及印刷电路板100的2个孔洞101、102的内侧壁面实现印刷电路板100中多层平面绕组中至少一平面绕组电气连接,更甚者该多层平面绕组通过该电镀区105并联连接借此降低所述平面绕组的线路损耗。

[0037]

请参阅图4,并配合图2及图3a-图3b,其中图4为图2所示的磁性组件组接扣合时的结构示意图。如图所示,于其它实施例中,由于2个电感l为磁集成电感,故磁性组件20更可包含中柱213,中柱213是部分形成于上磁盖201上,中柱213其余部分则形成于下磁盖202上,此外,磁性组件20更包含气隙214,气隙214形成于中柱213上。另外,由于磁性组件20借由上磁盖201及下磁盖202而形成中柱213,故为了使上磁盖201以及下磁盖202可彼此扣合于印刷电路板100上,于其它实施例中,印刷电路板100更可由第二侧边100d的中间位置内凹而形成中柱槽103,其中中柱槽103介于孔洞101、102之间并与中柱213的位置相对应,且中柱槽103的槽孔大小对应于中柱213的体积,更甚者,中柱槽103内的两相对内壁面104分别与第二侧边100d相邻接,当上磁盖201由印刷电路板100的上表面100e设置于印刷电路板100上且下磁盖202由印刷电路板100的下表面100f设置于印刷电路板100上时,中柱213便穿设中柱槽103而容置于印刷电路板100内。在另一实施例中,磁性组件20的2个边柱211、212上亦可分别形成气隙,其中借由该磁性组件20的中柱213的气隙大于或等于2个边柱211和212上的气隙,并配合印刷电路板100的平面绕组的绕制方向,使得该2个边柱211和212直流磁通方向相同,交流磁通方向相反,等效电感的纹波电流大幅下降,电感l的抗饱和能力也大幅提高。

[0038]

在另一实施例中,2个边柱211和212以及中柱213亦可全部形成于上磁盖201或全部形成于下磁盖202。例如,以2个边柱211和212以及中柱213全部形成上磁盖201为例,此时上磁盖201的2个边柱211和212及中柱213分别穿设放置于印刷电路板100的孔洞101和102及中柱槽103,进而与下磁盖202扣合印刷电路板100上,并在中柱213上设置气隙,借此配合印刷电路板100的平面绕组而构成2个磁集成电感l。

[0039]

另外,针对图3b所对应的单个降压电路的实施例中,因为该电路拓扑的开关电路21的开关元件可以采用大占空比d,从而根据交流磁通密度的公式,在相同的输出电压vo,相同的开关周期t

sw

,相同的变压器原边绕组匝数n,相同的交流磁通密度b

ac

的条件下,大占空比d的应用,可以降低磁芯有效截面积ae的数值,从而可以减小磁芯厚度,减小该电压调节模块2的厚度。更进一步可以减小磁芯组件20的中柱213的截面积,增大该印刷电路板100的平面绕组的宽度,减小平面绕组的寄生直流电阻阻值,减小平面绕组带来的直流损耗。此外,采用图3b的大占空比的实施例,更可以增强2个磁集成电感l的耦合效果,减小等效电感量。另外,图3b的电路拓扑中每个开关电路21的开关元件所承受的电压降低,从而所对应开关的寄生电容也降低,开关损耗亦同时降低,可以进一步提升该电路拓扑的工作频率,从而进一步降低该电路拓扑所应用的磁性组件的尺寸,实现薄型化,小尺寸,高功率密度的电压调节模块。

[0040]

另外,对应于中柱槽103的形成,故形成2个电感l的印刷电路板100的平面绕组同样可能分别部分暴露于中柱槽103内的两相对内壁面104,故为了降低所述平面绕组的线路损耗,亦可将两相对内壁面104电镀而形成电镀区105,使暴露于两相对内壁面104的印刷电路板的多层平面绕组中的至少一层与电镀区105电气连接,更甚者该多层平面绕组通过该电镀区105并联连接。

[0041]

请参阅图5,并配合图3a、图3b、图4,其中图5为图3a或图3b所示的2个电感上的电流的流动方向示意图。如图所示,电压调节模块2的降压电路内的电流从2个开关电路21流出,并如箭头所示以逆时针方向流过磁性组件20的2个边柱211和212,以此来实现流经2个边柱211和212的直流磁通方向相同,减小直流磁损。同时,根据错相控制的2个脉宽控制信号pwm1、pwm2,使流经2个边柱211和212的交流磁通方向相反,可以实现交流磁通的部分或者全部抵消,减小交流磁损,等效电感的纹波电流大幅下降,电感l的抗饱和能力也大幅提高。然流经电感l的电流方向并不以此为限,亦可以全部顺时针方向,只要能实现流经边柱211、212的直流磁通方向相同,交流磁通方向相反即可。在本实施例中,该2个脉宽控制信号pwm1和pwm2的错相角可以为[150,210]度之间的任一值,比如2个脉宽控制信号pwm1和pwm2可错相180度,交流磁损明显减少,且电感的纹波电流降低。

[0042]

请参阅图6,其是为本案第二较佳实施例的电压调节模块的爆炸结构示意图。如图所示,于一些实施例中,当图2、图4所示的中柱213上的气隙214的高度与中柱213的高度相等时,则磁性组件20可不具有中柱213,即如图6所示,磁性组件20仅包含2个边柱211、212。此外,对应于图6所示磁性组件20不具有中柱,故图6所示的印刷电路板100亦不具有类似于图2所示的印刷电路板100的中柱槽103,然而为了使方向与边柱211、212上的磁力线方向相反的磁力线可通过印刷电路板100,故印刷电路板100可包含净空区106,净空区106位于孔洞101、102之间,且印刷电路板100对应于净空区106的位置区域上不放置任何电子组件、任何平面绕组或是印刷电路板内用作电气连接的导电线路,借此与边柱211、212上的磁力线方向相反的磁力线便可经由净空区106通过印刷电路板100。

[0043]

请参阅图7a,其是为本案第三较佳实施例的电压调节模块的部分结构示意图。如图所示,于一些实施例中,印刷电路板100的下表面100f上更可设置多个铜块108、109、110、111、所述铜块108、109、110、111可分别电性连接于该印刷电路板100上的电压调节模块2的

正输入端、负输入端、正输出端、负输出端和相应的信号端中的其中之一,以构成电压调节模块2对应的导接脚位。另外,电压调节模块2的电容组合,例如输入电容cin等,可设置于印刷电路板100的下表面100f上。

[0044]

当然,印刷电路板100内的导电结构并不局限于由印刷电路板100内部的平面绕组(由印刷电路板100内的布线所形成)所构成。请参阅图7b,其是本案第四较佳实施例的电压调节模块的部分结构示意图。如图所示,于一些实施例中,电压调节模块2的印刷电路板100内可埋设2个铜块107(于此以虚线来代表铜块107埋设于印刷电路板100内),以取代第一实施例或第二实施例中印刷电路板100内部的平面绕组,进而构成印刷电路板100内的至少一导电结构,并形成2个电感l的绕组,其中每一铜块107的埋设位置与2个孔洞101、102中的其中的一孔洞相对应,且每一铜块107的一端电性连接开关电路21,在该印刷电路板100的下表面100f上,放置导接脚位108a与对应的铜块107电气连接。在另一实施例中,亦可将铜块107和导接脚位108a一体成型制作,即每一铜块107的另一端则至少部分暴露于印刷电路板100的下表面100f上而形成导接脚位108a,导接脚位108a可构成电压调节模块2的正输出端vo+。另外,如图7b所示,电压调节模块2的电容组合,例如输入电容cin等,可设置于印刷电路板100的下表面100f上。当然,印刷电路板100的下表面100f上更可设置多个铜块109、110、111,所述铜块109、110、111可分别电性连接于该印刷电路板100上的电压调节模块2的正输入端、负输出端和相应的信号端的其中的一电位点,以构成电压调节模块2对应的导接脚位。

[0045]

在上述这些实施例中,电压调节模块2更可包含塑封层,是设置于印刷电路板100的下表面100f上,用以将下表面100f连同放置在100f上的元器件一并塑封,例如图8所示,其是本案第五较佳实施例的电压调节模块的部分结构示意图,该电压调节模块2更可包含塑封层30。塑封层30是设置于印刷电路板100的下表面100f上,用以将图7a或图7b所示的印刷电路板100的下表面100f上连同设置于下表面100f上的电容组合和所有铜块(如图7a所示的铜块108、109、110、111或图7b所示的铜块109、110、111及导接脚位108a)塑封成一体。更甚者,当塑封层30塑封了印刷电路板100的下表面100f、电容组合和所有铜块后,可以对塑封层30的外表面30a进行打磨,使印刷电路板100的下表面100f上的所有铜块露出于塑封层30的外表面30a(未图式)。当然,塑封层30的外表面30a上更可利用电镀方式而形成多个电镀图形,每一电镀图形的形成位置对应于与自身导接且露出于塑封层30的外表面30a的铜块,且所述电镀图形的面积大于相对应的铜块的截面积,所述电镀图形可分别作为电压调节模块2的导接脚位,例如正输出端vo+、负输出端vo-、正输入端vin+等,当然部分电镀图形亦可作为电压调节模块2的信号端。举例而言,如图8所示,至少一电镀图形221可为电压调节模块2的正输出端vo+,至少一电镀图形222可为电压调节模块2的负输出端vo-,至少一电镀图形223可为电压调节模块2的正输入端vin+,至少一电镀图形224可为电压调节模块2的信号传输端。然电镀图形的个数与设置位置并不局限于如图8所示,可依实际需求而有不同的实施态样。另外,当电镀图形的电镀面积越大,电压调节模块2可焊接的面积越大,故于系统板再次回流焊时,该电压调节模块2因为再次受热而发生脱落或位移的风险就越小,且焊点电流密度大幅下降,产品焊点的可靠性大幅上升。

[0046]

请参阅图9及图10,其中图9为本案第六较佳实施例的电压调节模块的爆炸结构示意图,图10为图9所示的电压调节模块的等效电路图。如图所示,本实施例的电压调节模块

2a可应用在电子装置内,并与电子装置内的系统板(未图标)以焊接方式连接,其中由于本实施例的电压调节模块2a的部分组件与图2、图3a-图3b所示的电压调节模块2的部分组件相似,故在图9、图10中,部分组件将以相同于图2、图3a-图3b的标号来标示,而不再做细部说明。

[0047]

于本实施例中,电压调节模块2a包含并联连接的4个单相降压电路而构成4相降压电路,且电压调节模块2a亦包含输出电容cout。4个单相降压电路的其中2个单相降压电路构成一电源组22,4个单相降压电路的另外2个单相降压电路亦构成另一电源组22,且每一电源组22更包含至少一输入电容cin。2个电源组22的输入电容cin的第一端彼此电连接,以构成电压调节模块2a的正输入端vin+,2个电源组22的输入电容cin的第二端为短路相接,并构成电压调节模块2a的负输入端vin-。输出电容cout的第一端可构成电压调节模块2a的正输出端vo+,输出电容cout的第二端可构成电压调节模块2a的负输出端vo-。每一电源组22的每一单相降压电路更包含具有驱动器及开关元件的驱动器开关单元21(后面简称开关电路21)及电感l,每一开关电路21串联连接于对应的电感l的第一端sw。每个开关电路21具有3个端口,分别为第一端、第二端、第三端。每一电源组22内的2个开关电路21的第一端并联电性连接后与对应的电源组22的输入电容cin电性连接。每一电源组22内的2个开关电路21的第二端并联电性连接后与对应的电源组22的输入电容cin的负端电性连接。而每一电源组22内的2个开关电路21的第三端分别电性连接该2个电感l的一端,且2个电感l的另一端并联电性连接后与输出电容cout的第一端电性连接。

[0048]

其中一电源组22内的2个单相降压电路是与另一电源组22内的2个单相降压电路并联连接,且每一电源组22内的2个单相降压电路的第一端并联电连接,并电连接于输入电容cin的第一端,每一电源组22内的2个单相降压电路的第二端彼此电连接,并电连接于输出电容cout的第一端,此外,每一单相降压电路包含驱动器金属氧化物半导体场效应晶体管单元21(driver and metal-oxide-semiconductor field-effect transistor;dr.mos,后面简称为开关电路21)及电感l,故电压调节模块2a实际上包含4个开关电路21以及4个电感l。

[0049]

每一单相降压电路的开关电路21串联连接于对应的电感l的第一端sw,且与对应的输入电容cin的的第一端电连接。2个电源组22内的所有单相降压电路的电感l的第二端彼此电连接,且与输出电容cout的第一端电连接。

[0050]

于上述实施例中,由于电压调节模块2a实际上由4个单相降压电路并联连接所构成,故可有效地增大电压调节模块2a的输出电流能力。

[0051]

于一些实施例中,开关电路21包含晶体管开关及用来驱动晶体管开关的驱动器。电压调节模块2还包含控制电路11a,控制电路11a通过采样电压调节模块2的输出电压和各单相降压电路的输出电流而产生4组脉宽控制信号pwm1、pwm2、pwm3、pwm4,其中两组脉宽控制信号用来驱动其中的一电源组22,且错相180度,而另外两组脉宽控制信号用来驱动另一电源组22,且同样错向180度,此外,其中之一电源组22内的2个脉宽控制信号与另一电源组内的2个脉宽控制信号是两两错相90度。举例而言,脉宽控制信号pwm1用来控制其中之一电源组22中的第1个单相降压电路,脉宽控制信号pwm2用来控制其中之一电源组22中的第二个单相降压电路,脉宽控制信号pwm3用来另一电源组22中的第1个单相降压电路,脉宽控制信号pwm4用来另一电源组22中的第二个单相降压电路,且脉宽控制信号pwm1与脉宽控制信

号pwm2错相180度,脉宽控制信号pwm3和脉宽控制信号pwm4错相180度,又脉宽控制信号pwm1与脉宽控制信号pwm3错相90度,脉宽控制信号pwm2与脉宽控制信号pwm4错相90度。

[0052]

此外,于其它实施例中,输出电容cout可设置于电压调节模块2a内,但不以此为限,亦可设置于电子装置内的系统板上。

[0053]

在本实施例中,电压调节模块2a包含印刷电路板组件10a及磁性组件20a。印刷电路板组件10a包含印刷电路板300及4个开关电路21。印刷电路板300内部具有由印刷电路板平面绕组(由印刷电路板300内的布线所形成)所构成的导电结构(未图式),且印刷电路板300包含4个侧边,即为相对的第一侧边300a与第二侧边300d,及位于第一侧边300a与第二侧边300d之间且为相对的第三侧边300b以及第四侧边300c,此外,印刷电路板300亦包含为相对的上表面300e以及下表面300f。下表面300f上可以通过焊锡焊接方式或者导电胶黏贴方式而供输入电容cin设置(未图示)。4个开关电路21可为但不限于以焊锡焊接方式或者导电胶黏贴方式设置于印刷电路板300的上表面300e上,其中之一电源组22内的2个开关电路21并排设置在印刷电路板300的上表面300e上,该2个开关电路21构成的1个开关电路组合,相对于印刷电路板300的第二侧边300d而较为邻近于印刷电路板300的第一侧边300a、第三侧边300b以及第四侧边300c,即该开关电路组合贴合印刷电路板100的第一侧边300a、第三侧边300b及第四侧边300c放置。该开关组合中的该2个开关电路21的第一端并联,且第二端并联,并分别构成该开关电路组合的第一端和第二端,且共用一组输入电容cin,而被该2个开关电路21共用的输入电容cin放置在印刷电路板300的下表面300f,并靠近对应的该一开关电路组合的第一端放置,因此使得该2个开关电路21与共用的一组输入电容cin之间寄生参数最小。且,因为输入电容cin的纹波电流频率是该电压调节模块的开关频率的2倍,从而使得输入电容cin的纹波电流小,降低输入电容cin上的损耗,更可以使用小尺寸的电容cin,以此来减小电压调节模块的体积。另一电源组22内的2个开关电路21沿第二方向设置在印刷电路板300的上表面300e上,该2个开关电路21构成的另1个开关电路组合,该另1个开关电路组合相对于印刷电路板300的第一侧边300a而较为邻近于印刷电路板300的第二侧边300d、第三侧边300b以及第四侧边300c,即该另一开关电路组合贴合印刷电路板100的第二侧边300d、第三侧边300b及第四侧边300c放置,并且该另一开关电路组合中的该2个开关电路21的第一端并联连接,且第二端并联连接,并分别构成该开关电路组合的第一端和第二端,且共用另一组输入电容cin,而被该2个开关电路21共用的该另一组输入电容cin放置在印刷电路板300的下表面300f,并靠近对应的该另一开关电路组合的第一端放置,因此使得2个开关电路21和共用的另一组输入电容cin之间寄生参数最小。且因为输入电容cin的纹波电流频率是该电压调节模块的开关频率的2倍,从而使得输入电容cin的纹波电流小,降低输入电容cin上的损耗,更可以使用小尺寸的电容cin,以此来减小电压调节模块的体积。

[0054]

于一实施例中,该开关电路组合的第一端可以对应到每个开关电路21的第一端所对应的脚位,也可以对应到连接该2个开关电路21的第一端所对应脚位的电气路径中的任一点。另外,如第10图所示,电压调节模块2a内的2个开关电路组合的4个开关电路21为并联连接。

[0055]

于另一实施例中,可将以上实施例中的所述输入电容cin内埋于印刷电路板,且与该导电结构不同层。于另一实施例中,亦可将所述开关电路21内埋于印刷电路板,且与该导

电结构及输入电容皆不同层。

[0056]

磁性组件20a包含上磁盖401以及下磁盖402,边柱411、412、413和414以及中柱415,其中上磁盖401设置于印刷电路板300的上表面300e上,下磁盖402与上磁盖401相对应地设置于印刷电路板300的下表面300f上,且边柱411、412、413和414以及中柱415设置于上磁盖401以及下磁盖之间,并与上磁盖401以及下磁盖402及印刷电路板300内的对应的平面绕组相互配合而形成4个电感l,其中4个电感l为磁集成电感,借此缩小4个电感l的体积。此外,该磁芯组件20a和2个开关电路组合沿第一方向设置于印刷电路板300上,且磁芯组件20a的位置更位于印刷电路板300的中间区域而介于该一组开关组合和该另一组开关组合之间。

[0057]

由上述内容可知,由于本实施例的电压调节模块2a内的磁性组件与2个开关电路组合同样采用水平布局方式,即沿第一方向,设置于印刷电路板300上,因此相比现有电子装置内的电压调节模块的开关电路和磁性组件为上下叠放,本实施例的电压调节模块2a的高度可大幅下降,更甚者,由于本实施例的电压调节模块2a的4个电感l为磁集成电感,且4相磁集成,相比于2相磁集成,交流磁通的抵消能力进一步加强,电感电流纹波进一步减小,瞬态大电流条件下,电感l的抗饱和能力进一步加大,故4个电感l的体积可减小,使得本实施例的电压调节模块2a的体积和高度可再进一步缩小,因此本实施例的电压调节模块2a的厚度整体可小于或等于5mm,甚至小于等于3mm,以符合薄型化的应用需求。另外,4个电感l与4个开关电路21水平紧密摆放,输入电容cin和滤波电容(未图式)可放在印刷电路板300的下表面300f和4个开关电路21对应的位置,使得开关电路21可和输入电容cin之间寄生参数最小,和/或和储能电容cp之间寄生参数最小,从而降低输入电容cin和储能电容cp的损耗,使得整个产品的尺寸也进一步减小。故本案的电压调节模块2a可达到薄型化、小封装面积和高功率密度的优势。

[0058]

于一些实施例中,为了形成电压调节模块2a的4个电感l,磁性组件20a包含4个边柱411、412、413、414,4个边柱411、412、413、414分别部分形成于上磁盖401上,4个边柱411、412、413、414其余部分则分别形成于下磁盖402上,此外,印刷电路板300亦对应包含4个孔洞301、302、303、304,其中4个孔洞301、302、303、304位于印刷电路板300的中间区域并介于4个开关电路21之间,且贯穿印刷电路板300,此外,孔洞301的位置与边柱411的位置相对应,孔洞302的位置与边柱414的位置相对应,孔洞303的位置与边柱412的位置相对应,孔洞304的位置与边柱413的位置相对应,当上磁盖401设置于印刷电路板300的上表面300e而下磁盖402设置于印刷电路板300的下表面300f时,4个边柱411、412、413、414便分别穿设对应的孔洞301、303、304、302而容置于印刷电路板300内,以与印刷电路板300内对应的平面绕组配合而形成电压调节模块2a内的4个电感l。另外,形成4个电感l的印刷电路板300内的平面绕组可相对于印刷电路板300的第一侧边300a及第二侧边300d而较为邻近于第三侧边300b或第四侧边300c,即磁性组件20贴合印刷电路板300的第三侧边300b及第四侧边300c放置。

[0059]

更甚者,因为电压调节模块2a尺寸的限制,在印刷电路板300内所放置的平面绕组的宽度将受限,导致所述平面绕组的线阻增大而造成一定的能量损耗,故为了避免此情况发生,在一些实施例中,可将形成电感l的印刷电路板的平面绕组所邻近的第三侧边300b及第四侧边300c的壁面以及/或印刷电路板300的4个孔洞301、303、304、302的内侧壁面进行

板边电镀而形成电镀区306,电镀区306可与印刷电路板300中多层平面绕组中至少一平面绕组连接,故电镀区306可于第三侧边300b及第四侧边300c的壁面以及印刷电路板300的4个孔洞301、303、304、302的内侧壁面实现印刷电路板300中多层平面绕组中的至少一层与电镀区105电气连接,更甚者该多层平面绕组通过该电镀区105并联连接,借此降低所述平面绕组的线路损耗。

[0060]

其它实施例中,由于4个电感l为磁集成电感,故磁性组件20a更可包含中柱415,中柱415是部分形成于上磁盖401上,中柱415其余部分则形成于下磁盖402上,此外,磁性组件20a更包含气隙(未图示),气隙形成于中柱415上。另外,由于磁性组件20a借由上磁盖401及下磁盖402而形成中柱415,故为了使上磁盖401以及下磁盖402可彼此扣合于印刷电路板300上,于其它实施例中,印刷电路板300更包含中柱孔305,其中中柱孔305介于孔洞301、302、303、304之间并与中柱415的位置相对应,且中柱孔305的槽孔大小对应于中柱415的体积,当上磁盖401由印刷电路板300的上表面300e设置于印刷电路板300上且下磁盖402由印刷电路板300的下表面300f设置于印刷电路板300上时,中柱413便穿设中柱孔305容置于印刷电路板300内。在另一实施例中,磁性组件20a的4个边柱411、412、413和414上亦可分别形成气隙,其中借由该磁性组件20a的中柱415的气隙大于或等于4个边柱411、412、413和414上的气隙,并配合印刷电路板300的平面绕组的绕制方向,使得任意2个边柱直流磁通方向相同,交流磁通方向相反,等效电感的纹波电流大幅下降,电感l的抗饱和能力也大幅提高。

[0061]

在另一实施例中,4个边柱411、412、413和414及中柱415亦可全部形成于上磁盖401或全部形成于下磁盖402。例如,4个边柱411、412、413和414及中柱415亦可全部形成于上磁盖401为例,此时上磁盖401的4个边柱411、412、413和414及中柱415穿设放置于印刷电路板300的孔洞301、302、303和304及中柱槽305,进而与下磁盖402扣合印刷电路板300上,并在中柱415上设置气隙,借此配合印刷电路板300的平面绕组而构成4个磁集成电感l。

[0062]

请参阅图11,并配合图9及图10,其中图11为图10所示的4个电感上电流流动时的方向示意图。如图所示,电压调节模块2a的4个单相降压电路的电流分别从对应的开关电路21流出,并如箭头所示以逆时针方向流过磁性组件20a的4个边柱411、412、413、414,以此来实现流经4个边柱411、412、413、414的直流磁通方向相同,减小直流磁损,同时,根据四组脉宽控制信号pwm1、pwm3、pwm2、pwm4依次错相90度控制,使流经4个边柱411,412,413和414中相临近的2个边柱的交流磁通方向相反,可以实现交流磁通的部分或者全部抵消,减小交流磁损,等效电感的纹波电流大幅下降,电感的抗饱和能力也大幅提高。然流经电感l的电流方向并不以此为限,亦可以全部顺时针方向,只要能实现流经边柱411,412,413和414的直流磁通方向相同即可。在本实施例中,该4个脉宽控制信号pwm1、pwm3、pwm2、pwm4两两之间的错相角可以为[60,120]度之间的任一值,如4个脉宽控制信号pwm1、pwm3、pwm2、pwm4可依次错相90度,从而减小交流磁损,降低电感的纹波电流。

[0063]

另外,磁性组件20a中的4个边柱中的其中2个边柱,例如边柱411、414的位置是位于4个开关电路21中错相90度的其中2个开关电路21之间,进而沿第一方向依次放置成一列配置,磁性组件20a中的4个边柱中的另外2个边柱,例如边柱412、413的位置是位于4个开关电路21中错相90度的另外2个开关电路21之间,进而沿第一方向依次放置呈另一列配置,且每一列配置中的边柱与最相邻的开关电路21之间的最短距离l5的2倍是小于相邻2个相邻边柱之间的最短距离,例如小于每一列配置中2个相邻边柱之间的最短距离l6。

[0064]

请参阅图12,其是为本案第七较佳实施例的电压调节模块的爆炸结构示意图。如图所示,于一些实施例中,当图9所示的中柱415上的气隙的高度与中柱415的高度相等时,则磁性组件20a可不具有中柱415,即如图12所示,磁性组件20a仅包含4个边柱411、412、413、414。此外,由于本实施例的磁性组件20a不具有中柱,故图12所示的印刷电路板300亦不具有类似于图9所示的印刷电路板300的中柱孔305,然而为了使方向与边柱411、412、413、414上的磁力线方向相反的磁力线可通过印刷电路板300,故印刷电路板300可包含净空区307,净空区307位于孔洞301、302、303、304之间,且印刷电路板300对应于净空区307的位置区域上不放置任何电子组件、任何平面绕组或是印刷电路板内用作电气连接的导电线路,借此与边柱411、412、413、414上的磁力线方向相反的磁力线便可经由净空区307通过印刷电路板300。

[0065]

当然,印刷电路板300内的导电结构并不局限于由印刷电路板300内部的平面绕组(由印刷电路板300内的布线所形成)所构成,可类似于图7b将铜块埋设于印刷电路板300内,以取代原先印刷电路板300内的平面绕组,进而构成印刷电路板300内的导电结构,亦可采用图7a和图7b所采用的铜块108/108a,109,110和111,用来电气连接印刷电路板300。此外,更可采用类似于前述图8所述的技术将塑封层设置于印刷电路板300的下表面300f上,并打磨塑封层而露出铜块,更可在塑封层上进行电镀而形成多个相较于铜块的截面积而言面积更大的电镀图形,然相关技术皆已于前述内容进行公开,故此处不再赘述。

[0066]

当然,在前述图9所示的由4个单相降压电路并联所构成的电压调节模块2a的脚位布局中,可设计为兼容图2所示的由2个单相降压电路并联的电压调节模块2的脚位布局,借此可使用2个图2所示的2相降压转换器来达成图9所示的由4个单相降压电路并联所构成的电压调节模块2a,惟使用2个图2所示的2相降压转换器所构成的电压调节模块其电感仅为两两采用磁集成技术形成,并非如图9所示的4个电感一起采用磁集成技术形成。

[0067]

由上述所述实施例可推及包含2n个开关电路的实施例,本案的主要技术为电压调节模块可具有2n个输入电容cin、2n个开关电路及2n个电感,其中n为正整数,且2n个电感由磁集成技术实现,另外,2n个开关电路及2n个电感采用水平布局方式设置于印刷电路板上,且每一电感与对应的开关电路电连接,使2n个电感与2n个开关电路共同形成2n相降压电路,且每2个开关电路并联电连接,且沿该第二方向排放并构成一开关电路组合,其中,每一开关组合中两个开关电路组合的控制信号的相位差为[150,210]度范围内任一值,且该n个开关电路组合的对应的开关电路的控制信号相位差为[360/2n-30,360/2n+30]度范围内任一值。

[0068]

请参阅图13,其是为本案较佳实施例的电压调节装置的结构示意图。如图所示,于本实施例中,电压调节装置5包含多个并联连接的电压调节模块50,其中多个电压调节模块50可皆由前述具有2个单相降压电路的电压调节模块2(例如图3a所示)所构成,或是皆由前述具有单个降压电路的电压调节模块2(例如图3b所示),或是皆由前述具有4个单相降压电路的电压调节模块2a(例如图10所示)所构成,其中多个电压调节模块50之间的相位差可为[-30,30]度之间的任一值,譬如0度,但不以此为限,多个电压调节模块50两两之间的相位差亦可依序相差[360/(2*n*x)-30,360/(2*n*x)+30]或[360/(n*x)-30,360/(n*x)+30]之间的任一值,例如相差360/(2*n*x)或360/(n*x),其中,2n为开关电路21的个数,x为电压调节模块50的个数。更进一步说明,即电压调节装置5内的多个电压调节模块50分别具有多个

脉宽控制信号,且每一电压调节模块50的多个脉宽控制信号皆对应于其它电压调节模块50中的多个脉宽控制信号,此外,每一电压调节模块50的脉宽控制信号与其它电压调节模块50中的所对应的脉宽控制信号的相位差可为[-30,30]度之间的任一值,譬如0度,或是每一电压调节模块50的脉宽控制信号与次1个电压调节模块50中的所对应的脉宽控制信号相差[360/(2*n*x)-30,360/(2*n*x)+30]之间的任一值或[360/(n*x)-30,360/(n*x)+30]之间的任一值,例如相差360/(2*n*x)或360/(n*x)。举例而言,在一实施例中,当电压调节装置5由5个图3a所示的电压调节模块2并联连接所构成时,则每一电压调节模块2都包含两组脉宽控制信号pwm1及pwm2,其中每一电压调节模块2的脉宽控制信号pwm1与其它电压调节模块2的对应的脉宽控制信号pwm1的相位差为0度,每一电压调节模块2的脉宽控制信号pwm2与其它电压调节模块2的对应的脉宽控制信号pwm2的相位差为0度。当然,于其它实施例中,当电压调节装置5由5个图3a所示的电压调节模块2(即第一电压调节模块2、第二电压调节模块2、第三电压调节模块2、第四电压调节模块2以及第五电压调节模块5)所构成时,则第一电压调节模块2的脉宽控制信号pwm1与第二电压调节模块2的对应的脉宽控制信号pwm1的相位差为360/10=36度,第二电压调节模块2的脉宽控制信号pwm1信号与第3个电压调节模块2的对应的脉宽控制信号pwm1信号的相位差为36度,以此类推。

[0069]

于上述实施例中,印刷电路板也可为多层pcb板,导电结构和开关电路21可内埋于印刷电路板内,并且开关所在的pcb板层设置于导电结构所处的pcb板层的上层空间,亦可实现本发明所示的电压调节模块的水平布局结构,同样使得本案的电压调节模块的高度大幅下降,以此实现薄型化的应用需求。

[0070]

综上所述,本案为一种电压调节模块及其适用的电压调节装置,其中电压调节模块内的电感与开关电路乃是采用水平布局方式设置于印刷电路板上,因此相比现有电子装置内的电压调节模块的开关电路和磁性组件为上下叠放,本案的电压调节模块的高度大幅下降,更甚者,由于本案的电压调节模块的多个电感为磁集成电感,故电感的体积可减小,使得本案的电压调节模块的体积和高度可再进一步缩小,因此本实施例的电压调节模块的厚度整体可小于或等于5mm,甚者小于或等于3mm,以符合薄型化的应用需求。另外,本案的电压调节模块电感与开关电路水平错位紧密摆放,而电容组合放在印刷电路板的下表面和开关电路对应的位置,使得整个产品的尺寸也进一步减小。故本案的电压调节模块可达到薄型化、小封装面积和高功率密度的优势。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1