一种避免有源层蚀刻的7Mask阵列基板及其制造方法与流程

一种避免有源层蚀刻的7 mask阵列基板及其制造方法

技术领域

1.本发明涉及显示面板技术领域,尤其涉及一种避免有源层蚀刻的7 mask阵列基板及其制造方法。

背景技术:

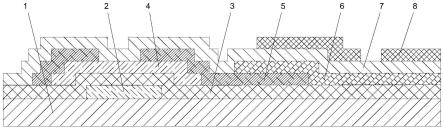

2.目前已应用于tft基板的array制造工艺主要集中在8 mask的外挂机种、9 mask top-com tic机种以及10 mask的mid-com tic机种。为了节省成本,现有的a-si机种也同步开发了7 mask的top-com外挂机种,不仅缩短了cycle time,并且简化了工艺流程,有效的提高效益。由于igzo制程与现有的a-si生产线有很好的兼容性,在不增加现有mask的情况下,可以实现a-si机种与igzo机种之间的直接转换。为此,基于7 mask机种的设计低成本优势,期望直接实现a-si转igzo,然而结合基板设计与制程工艺发现,如图1所示,由于7 mask设计省略了传统的tft器件上的pv绝缘膜层及有机平坦层oc,像素电极pe-ito设计与a-si共平面,传统的a-si pattern工艺采用的是干蚀刻方式,而像素电极pe-ito为草酸湿蚀刻。若a-si转igzo后,igzo蚀刻方式也为草酸湿蚀刻,不免造成无论先后pattern igzo还是ito,都会对另一道膜层pattern造成damage,从而影响画素无法正常显示。

技术实现要素:

3.本发明的目的在于提供一种避免有源层蚀刻的7 mask阵列基板及其制造方法。

4.本发明采用的技术方案是:一种避免有源层蚀刻的7 mask阵列基板,其包括玻璃基板,在玻璃基板上设有栅极金属层ge,栅极绝缘层gi完全覆盖栅极金属层ge,并直接覆盖玻璃基板的非栅极金属层ge覆盖的区域,有源层se设置在栅极绝缘层gi上表面对应栅极金属层ge上方的部分区域;源漏极金属层sd完全覆盖有源层se,并直接部分覆盖栅极绝缘层gi;像素电极层pe设置在源漏极金属层sd上,像素电极层pe部分覆盖源漏极金属层sd上,像素电极层pe部分直接覆盖在栅极绝缘层gi上;绝缘层ch完全覆盖像素电极层pe并直接覆盖源漏极金属层sd的部分区域,以及覆盖有源层se的背沟道;公共电极层uc设置在绝缘层ch上并覆盖绝缘层ch部分区域。

5.进一步地,栅极金属层ge采用ti/al/ti或mo/al/mo材料成型,金属层sd采用ti/al/ti或mo/al/mo材料成型。

6.进一步地,有源层se即tft器件半导体层,选用igzo材料成型。

7.进一步地,栅极绝缘层gi采用siox材料成型,绝缘层ch采用siox和sinx材料成型。

8.进一步地,公共电极uc为ito层,像素电极pe为ito层。

9.进一步的,公共电极uc对应设在像素电极层pe的上方区域。

10.一种避免有源层蚀刻的7 mask阵列基板的制造方法,其包括以下步骤:步骤1,在玻璃基板上图形化形成栅极金属层ge;步骤2,沉积一层栅极绝缘层gi完全覆盖栅极金属层ge,并直接覆盖玻璃基板的非

栅极金属层ge的区域;步骤3,在栅极绝缘层gi的表面对栅极金属层ge的上方区域图形化形成有源层se;步骤4,在有源层se上沉积一层源漏极金属层sd,源漏极金属层sd完全覆盖有源层se,并直接覆盖栅极绝缘层gi的非有源层se覆盖的区域;步骤5,在源漏极金属层sd上涂布一层光阻pr,采用灰阶光罩进行曝光显影制程,步骤6,经曝光/显影后保留源漏极金属层sd区域的保留剩余的光阻pr;步骤7,蚀刻掉未被光阻pr保护的源漏极金属层sd,以露出对应栅极金属层ge两侧的部分有源层se;步骤8,去掉光阻pr;步骤9,在源漏极金属层sd上图形化形成像素电极层pe,像素电极层pe部分覆盖源漏极金属层sd上,像素电极层pe部分直接覆盖在栅极绝缘层gi上;步骤10,在像素电极层pe上涂布一层光阻pr,采用灰阶光罩进行曝光显影制程,步骤11,经曝光/显影后在源漏极金属层sd表面保留光阻pr,且光阻pr在金属层sd对应有源层se区域留有孔洞以漏出源漏极金属层sd;步骤12,蚀刻掉未被光阻pr保护的源漏极金属层sd,以形成有源层的背沟道;步骤13,去掉光阻pr;步骤14,在像素电极层pe上沉积一层绝缘层ch,绝缘层ch完全覆盖像素电极层pe并直接覆盖源漏极金属层sd的部分区域,以及覆盖有源层se的背沟道;步骤15,在绝缘层ch上图形化形成公共电极层uc,公共电极层uc覆盖绝缘层ch部分区域。

11.进一步地,步骤1中采用干蚀刻方式制作栅极金属层ge。

12.进一步地,步骤4中采用pvd沉积一层源漏极金属层sd。

13.进一步地,步骤10的曝光量大于步骤6曝光的曝光量。

14.进一步的,步骤14中采用cvd沉积一层绝缘层ch。

15.进一步的,灰阶光罩具有对应最终源漏极金属层sd设置的非透光区域、对应非源漏极金属层sd区域设置的孔1以及对应背沟道处设置的孔2,且孔1的穿透率>孔2的穿透率。

16.本发明采用以上技术方案,在不改变7 mask的光罩数量基础上,变更了像素电极和源漏极的成膜顺序,源漏极光罩采用具有不同穿透率的灰阶光罩,结合两次不同的曝光工艺,以及源漏极先成膜,后蚀刻的方式,有效避免了igzo与像素电极之间的相互蚀刻问题。

附图说明

17.以下结合附图和具体实施方式对本发明做进一步详细说明;图1为现有的7 mask的tft基板结构示意图;图2为本发明一种避免有源层蚀刻的7 mask阵列基板的结构示意图;图3为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤1制作有源层se并图形化处理后的状态示意图;图4为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤2的过程

状态示意图;图5为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤3的过程状态示意图;图6为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤4的过程状态示意图;图7为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤5的过程状态示意图;图8为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤6的过程状态示意图;图9为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤7的过程状态示意图;图10为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤8的过程状态示意图。

18.图11为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤9的过程状态示意图;图12为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤10的过程状态示意图;图13为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤11的过程状态示意图;图14为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤12的过程状态示意图;图15为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤13的过程状态示意图;图16为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤14的过程状态示意图。

19.图17为本发明一种避免有源层蚀刻的7 mask阵列基板的制备方法的步骤15的过程状态示意图。

具体实施方式

20.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图对本技术实施例中的技术方案进行清楚、完整地描述。

21.附图中相关标号的说明:1、玻璃基板glass:array侧基板玻璃,显示器件的基本部件,其上依序形成tft等有源器件;2、栅极金属层ge: metal 1金属层,此处可选mo/al/mo或ti/al/ti;3、栅极绝缘层gi:具有较大介电常数的绝缘层,本发明方案可选siox;4、有源层se: tft器件半导体层,本发明方案将a-si改为igzo;5、源漏极金属层sd:metal 2金属层,此处为ti/al/ti或mo/al/mo;6、像素电极层pe:为ito层;7、绝缘层ch:具有较大介电常数的绝缘层,本发明方案可选siox和sinx;8、公共电极层uc:为ito层;9、孔1;10、非透光区;11,孔2; 12,光阻;13,背沟道;14,灰阶光罩。

22.如图2至17之一所示,本发明公开了一种避免有源层蚀刻的7 mask阵列基板,其包

括玻璃基板,在玻璃基板上设有栅极金属层ge,栅极绝缘层gi完全覆盖栅极金属层ge,并直接覆盖玻璃基板的非栅极金属层ge覆盖的区域,有源层se设置在栅极绝缘层gi上表面对应栅极金属层ge上方的部分区域;源漏极金属层sd完全覆盖有源层se,并直接部分覆盖栅极绝缘层gi;像素电极层pe设置在源漏极金属层sd上,像素电极层pe部分覆盖源漏极金属层sd上,像素电极层pe部分直接覆盖在栅极绝缘层gi上;绝缘层ch完全覆盖像素电极层pe并直接覆盖源漏极金属层sd的部分区域,以及覆盖有源层se的背沟道;公共电极层uc设置在绝缘层ch上并覆盖绝缘层ch部分区域。

23.进一步地,栅极金属层ge采用ti/al/ti或mo/al/mo材料成型,金属层sd采用ti/al/ti或mo/al/mo材料成型。

24.进一步地,有源层se即tft器件半导体层,选用igzo材料成型。

25.进一步地,栅极绝缘层gi采用siox材料成型,绝缘层ch采用siox和sinx材料成型。

26.进一步地,公共电极uc为ito层,像素电极pe为ito层。

27.进一步的,公共电极uc对应设在像素电极层pe的上方区域。

28.一种避免有源层蚀刻的7 mask阵列基板的制造方法,其包括以下步骤:步骤1,在玻璃基板上图形化形成栅极金属层ge;步骤2,沉积一层栅极绝缘层gi完全覆盖栅极金属层ge,并直接覆盖玻璃基板的非栅极金属层ge的区域;步骤3,在栅极绝缘层gi的表面对栅极金属层ge的上方区域图形化形成有源层se;步骤4,在有源层se上沉积一层源漏极金属层sd,源漏极金属层sd完全覆盖有源层se,并直接覆盖栅极绝缘层gi的非有源层se覆盖的区域;步骤5,在源漏极金属层sd上涂布一层光阻pr,采用灰阶光罩进行曝光显影制程,步骤6,经曝光/显影后以在待保留源漏极金属层sd区域的保留剩余的光阻pr;步骤7,蚀刻掉未被光阻pr保护的源漏极金属层sd,以露出对应栅极金属层ge两侧的部分有源层se;步骤8,去掉光阻pr;步骤9,在源漏极金属层sd上图形化形成像素电极层pe,像素电极层pe部分覆盖源漏极金属层sd上,像素电极层pe部分直接覆盖在栅极绝缘层gi上;步骤10,在像素电极层pe上涂布一层光阻pr,采用灰阶光罩进行曝光显影制程,步骤11,经曝光/显影后在源漏极金属层sd表面保留光阻pr,且光阻pr在金属层sd对应有源层se区域留有孔洞以漏出源漏极金属层sd;步骤12,蚀刻掉未被光阻pr保护的源漏极金属层sd,以形成有源层的背沟道;步骤13,去掉光阻pr;步骤14,在像素电极层pe上沉积一层绝缘层ch,绝缘层ch完全覆盖像素电极层pe并直接覆盖源漏极金属层sd的部分区域,以及覆盖有源层se的背沟道;步骤15,在绝缘层ch上图形化形成公共电极层uc,公共电极层uc覆盖绝缘层ch部分区域。

29.进一步地,步骤1中采用干蚀刻方式制作栅极金属层ge。

30.进一步地,步骤4中采用pvd沉积一层源漏极金属层sd。

31.进一步地,步骤10的曝光量大于步骤6曝光的曝光量。

32.进一步的,步骤14中采用cvd沉积一层绝缘层ch。

33.进一步的,灰阶光罩具有对应最终源漏极金属层sd设置的非透光区域、对应非源漏极金属层sd区域设置的孔1以及对应背沟道设置的孔2,且孔1的穿透率>孔2的穿透率。

34.本发明采用以上技术方案,在不改变7 mask的光罩数量基础上,变更了像素电极和源漏极的成膜顺序,源漏极光罩采用具有不同穿透率的灰阶光罩,结合两次不同的曝光工艺,以及源漏极先成膜,后蚀刻的方式,有效避免了igzo与像素电极之间的相互蚀刻问题。

35.显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。因此,本技术的实施例的详细描述并非旨在限制要求保护的本技术的范围,而是仅仅表示本技术的选定实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1