半导体工艺方法和半导体装置系统与流程

1.本发明涉及半导体工艺领域,具体地,涉及一种半导体工艺方法和一种用于执行该半导体工艺方法的半导体装置系统。

背景技术:

2.在半导体制程进入14nm及以下,半导体逻辑器件采用鳍式场效应晶体管(fin field-effect transistor,finfet)技术,而鳍(fin)图形的关键尺寸(critical dimension,cd)和间距(pitch)分别微缩到20nm和48nm以下。由于arf浸没式(arf-immersion)光刻技术的极限,使得由一次光刻得不到想要的关键尺寸和间距,因此业界普遍自对准双重图形(self-aligned double patterning,sadp)和自对准四重图形(self-aligned quadruple patterning,saqp)技术来获得想要的尺寸和间距。

3.以自对准双重图形技术为例,如图1至图7所示,自对准双重图形技术一般包括:1)芯轴光刻;2)芯轴刻蚀;3)原子层侧壁沉积;4)侧壁刻蚀;5)芯轴移除;6)鳍片掩模刻蚀;7)鳍片刻蚀这七个步骤。在自对准双重图形和四重图形中,过程中的每一道的工艺都会影响最终鳍片的间距,包括芯轴光刻的尺寸,芯轴刻蚀后的尺寸,原子层侧壁沉积的厚度,原子层侧壁的刻蚀之后的尺寸和刻蚀之后倾斜的角度,鳍片掩模刻蚀后的尺寸,和最终鳍片的尺寸,都会影响到最终鳍片的间距,使鳍片之间的间距均匀性较差。

4.因此,如何保证鳍片间距的均匀性,成为本领域亟待解决的技术问题。

技术实现要素:

5.本发明旨在提供一种半导体工艺方法和一种用于执行该半导体工艺方法的半导体装置系统,该半导体工艺方法能够实现稳定维持鳍片间距的均匀性。

6.为实现上述目的,作为本发明的一个方面,提供一种半导体工艺方法,用于对预定基板进行处理,所述预定基板包括衬底和位于所述衬底上的至少一层芯轴层,所述半导体工艺方法包括:

7.在第一工艺条件下,对位于顶层的所述芯轴层进行刻蚀,形成多个第一芯轴;

8.获取每个所述第一芯轴的宽度值;

9.在每个所述第一芯轴的两侧形成第一侧壁;

10.以所述第一侧壁为掩膜对所述预定基板进行刻蚀,以在所述衬底上形成多个鳍片结构;

11.获取多个所述鳍片结构之间的间距;

12.基于所述第一芯轴的宽度值以及对应的所述鳍片结构之间的间距,判断多个所述鳍片结构之间的间距是否一致,若不一致,则调整所述第一工艺条件为第二工艺条件,通过所述第二工艺条件对在后执行所述半导体工艺时所述第一芯轴的宽度值进行调节,以使多个所述鳍片结构之间的间距趋于一致。

13.可选地,所述芯轴层为单层结构;

14.所述基于所述第一芯轴的宽度值以及对应的所述鳍片结构之间的间距,判断多个所述鳍片结构之间的间距是否一致,包括:

15.计算多个所述第一芯轴对应的多对所述鳍片结构中每对所述鳍片结构之间的间距的平均值与多对相邻且对应于不同所述第一芯轴的所述鳍片结构之间的间距的平均值之间的第一差值;

16.判断所述第一差值是否在预设范围内;

17.若所述第一差值超出所述预设范围,则多个所述鳍片结构之间的间距不一致。

18.可选地,所述调整所述第一工艺条件为第二工艺条件,通过所述第二工艺条件对在后执行所述半导体工艺时所述第一芯轴的宽度值进行调节,包括:

19.将所述第一芯轴的宽度值和所述第一差值做一一对应关系并做拟合,寻找在所述预设范围内的所述第一芯轴的目标宽度值;

20.调整所述第一工艺条件为第二工艺条件,以使在后形成的所述第一芯轴的宽度值满足目标宽度值。

21.可选地,所述预定基板包括位于衬底上且由下至上依次层叠设置的第二芯轴层和第一芯轴层;

22.所述对所述预定基板进行刻蚀,以在所述基底上形成多个鳍片结构,包括:

23.以所述第一侧壁为掩膜对所述第二芯轴层进行刻蚀,得到多个第二芯轴;

24.在每个所述第二芯轴的两侧制作第二侧壁;

25.以所述第二侧壁为掩膜对所述衬底进行刻蚀,以在所述衬底上形成多个所述鳍片结构;

26.所述基于所述第一芯轴的宽度值以及对应的所述鳍片结构之间的间距,判断多个所述鳍片结构之间的间距趋于一致,包括:

27.计算多个所述第一芯轴对应的多组所述鳍片结构中两个所述第二芯轴对应的两对所述鳍片结构之间的间距的第一平均值与多对相邻且对应于不同组的所述鳍片结构之间的间距的第二平均值;

28.判断所述第一平均值和所述第二平均值之间的第二差值是否在预设范围内,若所述第二差值超出所述预设范围,则多个所述鳍片结构之间的间距不一致。

29.可选地,所述调整所述第一工艺条件为第二工艺条件,通过所述第二工艺条件对在后执行所述半导体工艺时所述第一芯轴的宽度值进行调节,包括:

30.将所述第一芯轴的宽度值和所述第二差值做一一对应关系并做拟合,寻找在所述预设范围内的所述第一芯轴的目标宽度值;

31.调整所述第一工艺条件为第二工艺条件,以使在后形成的所述第一芯轴的宽度值满足目标宽度值。

32.可选地,所述在每个所述第一芯轴的两侧形成第一侧壁,包括:

33.在第三工艺条件下,在所述第一芯轴的表面沉积第一侧壁层;

34.刻蚀所述第一侧壁层,形成顶面裸露的所述第一芯轴和竖直的所述第一侧壁;

35.所述半导体工艺方法还包括:

36.获得所述第一侧壁层的厚度值;

37.计算多个所述第二芯轴对应的每对所述鳍片结构之间的间距的第三平均值,以及

所述第一平均值与所述第二平均值之间的第四平均值,以得到所述第四平均值与所述第三平均值之间的第三差值;

38.建立所述第一侧壁层的厚度值与所述第三差值之间的对应关系;

39.判断所述第四平均值与所述第三平均值之间的第三差值是否在预设范围内,若所述第三差值超出所述预设范围,则调整所述第三工艺条件为第四工艺条件,通过所述第四工艺条件对在后执行所述半导体工艺时所述第一侧壁的宽度值进行调节。

40.可选地,根据重新确定的所述第一侧壁层的目标厚度,调节对所述第一芯轴层进行沉积的沉积参数,所述沉积参数包括沉积时间、沉积气体流量、温度中的至少一者。

41.可选地,所述预设范围为大于等于-0.5nm,且小于等于0.5nm。

42.可选地,所述调整所述第一工艺条件为第二工艺条件,通过所述第二工艺条件对在后执行所述半导体工艺时所述第一芯轴的宽度值进行调节,包括:

43.根据重新确定的所述第一芯轴的目标宽度值,调节对所述第一芯轴层进行刻蚀的步骤中的刻蚀参数,形成所述第二工艺条件,其中,所述刻蚀参数包括刻蚀时间、刻蚀气体流量、温度中的至少一者。

44.作为本发明的第二个方面,提供一种半导体装置系统,所述半导体装置系统用于执行前面所述的半导体工艺方法。

45.可选地,所述半导体装置系统包括半导体工艺设备、间隙检测装置和控制器,所述半导体工艺设备用于形成所述鳍片结构,所述间隙检测装置用于检测所述鳍片结构之间的间距,所述控制器用于基于所述第一芯轴的宽度值以及对应的所述鳍片结构之间的间距,判断多个所述鳍片结构之间的间距趋于一致,若不一致,则调整所述第一工艺条件为第二工艺条件,通过所述第二工艺条件对在后执行所述半导体工艺时所述第一芯轴的宽度值进行调节。

46.可选地,还包括膜厚检测装置,所述膜厚检测装置用于检测沉积在所述第一芯轴上的第一侧壁层的厚度值。

47.在本发明提供的半导体工艺方法和半导体装置系统中,半导体装置系统能够根据前面执行半导体工艺时第一芯轴的宽度值与鳍片间距之间的对应关系,对下一次执行半导体工艺时第一芯轴的宽度值进行调节,以使多个鳍片结构之间的间距趋于一致,从而能够在量产过程中根据前面多次执行工艺的工艺结果实时对下一次执行工艺时第一芯轴的宽度值进行反馈调节,进而实时稳定维持鳍片间距的均匀性,保证了产品性能、提高了产品良率。

附图说明

48.附图是用来提供对本发明的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明,但并不构成对本发明的限制。在附图中:

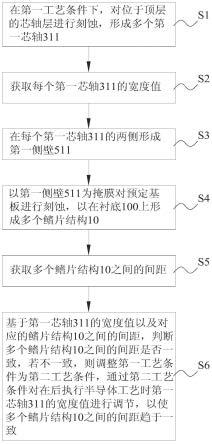

49.图1至图7是自对准双重图形技术的工艺过程示意图;

50.图8是自对准双重图形技术中各膜层图案之间的对应关系示意图;

51.图9是芯轴宽度值过小时,鳍片结构之间的间距情况示意图;

52.图10是芯轴宽度值过大时,鳍片结构之间的间距情况示意图;

53.图11是本发明实施例提供的半导体工艺方法的流程示意图;

54.图12是本发明实施例提供的半导体工艺方法得到的鳍片结构的俯视示意图;

55.图13是利用本发明实施例提供的半导体工艺方法对多个第一差值与对应的第一芯轴的宽度值做拟合后得到的曲线的示意图;

56.图14至图25是自对准四重图形技术的工艺过程示意图;

57.图26是自对准四重图形技术中各膜层图案之间的对应关系示意图;

58.图27是本发明实施例提供的半导体工艺方法得到的鳍片结构的俯视示意图;

59.图28是四重图形工艺中第一芯轴的宽度值对鳍片间距的影响效果示意图;

60.图29是四重图形工艺中第一芯轴的不同宽度值对应的鳍片结构之间的间距情况示意图。

61.附图标记说明:

62.100:衬底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

210:第一掩膜层

63.211:第一掩膜结构

ꢀꢀꢀꢀꢀ

310:第一芯轴层

64.311:第一芯轴

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

220:第二掩膜层

65.221:第二掩膜结构

ꢀꢀꢀꢀꢀ

320:第二芯轴层

66.321:第二芯轴

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

410:碳涂层

67.420:抗反射层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

430:光刻胶层

68.510:第一侧壁层

ꢀꢀꢀꢀꢀꢀꢀ

511:第一侧壁

69.520:第二侧壁层

ꢀꢀꢀꢀꢀꢀꢀ

521:第二侧壁

70.10:鳍片结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110:衬底鳍片

具体实施方式

71.以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

72.本发明的发明人在研究中发现,在自对准双重图形和四重图形技术中,芯轴宽度值的精确性对鳍片结构10均匀性存在较大影响,以自对准双重图形技术为例。如图1至图7所示,其步骤包括:

73.制备预定基板,如图1所示,该预定基板包括衬底100和位于衬底100上且由下至上依次层叠设置的第一掩膜层210和第一芯轴层310。然后,对预定基板进行芯轴光刻以及芯轴刻蚀步骤,即,依次在第一芯轴层310上制作碳涂层410(spin-on-carbon,即soc层)、抗反射层420和光刻胶层430,然后对光刻胶层430进行曝光工艺得到所需的第一芯轴311对应的图案,再以曝光后的刻胶层430为掩膜对第一芯轴层310进行刻蚀,形成多个第一芯轴311,如图2所示。

74.接着进行原子层侧壁沉积和侧壁刻蚀步骤,即,如图2至图3所示,在第一掩膜层210及其上方的多个第一芯轴311上沉积第一侧壁层510,然后,如图3至图4所示,对该结构进行刻蚀,以去除第一掩膜层210上以及多个第一芯轴311顶部的第一侧壁层510材料,仅留下每个第一芯轴311两侧的第一侧壁511;

75.然后,进行芯轴移除步骤,如图4至图5所示,去除第一芯轴311;再进行鳍片掩模刻蚀步骤,如图5至图6所示,以第一侧壁511为掩膜,对第一掩膜层210进行刻蚀得到多个第一掩膜结构211;最后,进行鳍片刻蚀步骤,如图6至图7所示,以第一侧壁511为掩膜,对衬底

100进行刻蚀,得到多个鳍片结构10。如图7所示,鳍片结构10可以包括衬底100材料形成的衬底鳍片110,还可以包括每个衬底鳍片110上方膜层的残留材料(例如第一掩膜结构211、一部分第一侧壁511等)。

76.在自对准图形工艺过程中,每一道工艺都会影响最终鳍片的间距,包括芯轴光刻的尺寸、芯轴刻蚀后的尺寸、原子层侧壁(第一侧壁511)沉积的厚度、原子层侧壁刻蚀之后的尺寸和刻蚀之后倾斜的角度、鳍片掩模刻蚀后的尺寸、和最终鳍片的尺寸等参数都会影响到最终鳍片结构10之间的间距,使鳍片结构10之间的间距均匀性较差。

77.例如,如图8所示,在自对准双重图形工艺中,每个第一芯轴311芯轴的两侧形成的第一侧壁511对应于最终形成的一对鳍片结构10。如图9所示,当芯轴宽度值过小时,会导致每个第一芯轴311对应的一对鳍片结构10之间的间距α较小,而相邻且不属于同一对的两鳍片结构10之间的间距β较大;如图10所示,当芯轴宽度值过大时,会导致每个第一芯轴311对应的一对鳍片结构10之间的间距α较大,而相邻且不属于同一对的两鳍片结构10之间的间距β较小。

78.因此,如何保证芯轴宽度值的精确性,是解决鳍片间距不一致问题的关键。

79.为解决上述技术问题,作为本发明的一个方面,提供一种半导体工艺方法,用于对预定基板进行处理,如图1、图14所示,该预定基板包括衬底100和位于衬底100上的至少一层芯轴层(例如,包括第一芯轴层310(即图1所示情况)或者包括第一芯轴层310和第二芯轴层320(即图14所示情况)),如图11所示,该半导体工艺方法包括:

80.步骤s1、在第一工艺条件下,对位于顶层的芯轴层进行刻蚀,形成多个第一芯轴311(如图1至图2、图14至图15所示);

81.步骤s2、获取每个第一芯轴311的宽度值;

82.步骤s3、在每个第一芯轴311的两侧形成第一侧壁511(如图2至图5、图15至图18所示);

83.步骤s4、以第一侧壁511为掩膜对预定基板进行刻蚀,以在衬底100上形成多个鳍片结构10(如图5至图7、图18至图25所示);

84.步骤s5、获取多个鳍片结构10之间的间距;

85.步骤s6、基于第一芯轴311的宽度值以及对应的鳍片结构10之间的间距,判断多个鳍片结构10之间的间距是否一致,若不一致,则调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节,以使多个鳍片结构10之间的间距趋于一致。

86.本发明提供的半导体工艺方法能够根据前面执行半导体工艺时第一芯轴311的宽度值与鳍片间距(即结构10之间的间距)之间的对应关系,对下一次执行半导体工艺时第一芯轴311的宽度值进行调节,以使多个鳍片结构10之间的间距趋于一致,从而能够在量产过程中根据前面多次执行工艺的工艺结果实时对下一次执行工艺时第一芯轴311的宽度值进行反馈调节,进而实时稳定维持鳍片间距的均匀性,保证了产品性能、提高了产品良率。

87.作为本发明的一种可选实施方式,该半导体工艺方法通过半导体工艺设备的控制器实现。可选地,该半导体工艺设备包括间隙检测装置,例如,可以是特征尺寸测量用扫描电子显微镜(critical dimension scanning electron microscope,cdsem)或者光学线宽测量(optical critical dimension,ocd)机台,用于检测当前半导体工艺设备中晶圆表面

图案的线宽(例如,第一芯轴311的宽度值或者最终得到的鳍片结构10之间的间距等)。

88.作为本发明的一种可选实施方式,步骤s1中通过光刻工艺对位于顶层的芯轴层进行刻蚀得到多个第一芯轴311。具体地,如图1、图14所示,预定基板还包括由下至上依次层叠设置在位于顶层的芯轴层上的碳涂层410、抗反射层420和光刻胶层430,步骤s1具体包括:

89.对光刻胶层430进行曝光构图,以得到所需的第一芯轴311对应的图案,再以曝光后的刻胶层430为掩膜对抗反射层420、碳涂层410和第一芯轴层310进行刻蚀,形成多个第一芯轴311,最后去除第一芯轴311上方残余的膜层材料,得到如图2、图15所示结构。

90.作为本发明的一种可选实施方式,芯轴层为单层结构(仅包括第一芯轴层310),即,本发明提供的半导体工艺方法为自对准双重图形工艺,如图1至图7所示。对应地,步骤s6中基于第一芯轴311的宽度值以及对应的鳍片结构10之间的间距,判断多个鳍片结构10之间的间距是否一致,具体包括:

91.步骤s611、计算多个第一芯轴311对应的多对鳍片结构10中每对鳍片结构10之间的间距α的平均值与多对相邻且对应于不同第一芯轴311的鳍片结构10之间的间距β的平均值之间的第一差值(即鳍片间距漂移(α-β)的平均值);

92.步骤s612、判断第一差值是否在预设范围内;

93.步骤s613、若第一差值超出预设范围,则多个鳍片结构10之间的间距不一致。

94.相应地,后续步骤中调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节,以使第一差值趋于零,即,使多个鳍片结构10之间的间距趋于一致。

95.在理想状况下间距α与间距β的大小应保持一致,如图12所示,即第一预设阈值应为零,然而,考虑到实际检测以及对刻蚀参数进行调节时存在一定误差,为避免频繁调节工艺条件(例如刻蚀工艺参数),以保证生产效率,作为本发明的一种优选实施方式,预设范围为大于等于-0.5nm(纳米),且小于等于0.5nm,即,在间距α的平均值与间距β的平均值之间差值的大小在0.5nm内时,则认为鳍片结构10之间的间距总体均匀,无需对工艺条件进行调节。

96.需要说明的是,本发明实施例中根据第一芯轴311宽度值及对应的鳍片结构10间距调整工艺条件的具体原理是根据不同的第一芯轴311宽度值与鳍片结构10间距的均匀程度,建立二者之间的线性对应关系,并基于已确定的线性对应关系重新确定所需的第一芯轴311宽度值,并为之调整工艺条件。

97.具体地,调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节的步骤具体包括:

98.将第一芯轴311的宽度值和第一差值做一一对应关系并做拟合,寻找在预设范围内的第一芯轴311的目标宽度值;

99.调整第一工艺条件为第二工艺条件,以使在后形成的第一芯轴311的宽度值满足目标宽度值。

100.例如,如图13所示为多个第一差值与对应的第一芯轴311的宽度值做拟合后得到的曲线的示意图,由该拟合得到的曲线即可确定第一差值为零的区域所对应的横坐标范围,即目标宽度值所在的范围,从而可以确定第一芯轴311的宽度值的调整范围,进而向响应方向调整工艺条件。

101.为避免步骤s1中刻蚀形成多个第一芯轴311时刻穿至衬底100,作为本发明的一种优选实施方式,如图1、图14所示,该预定基板还包括层叠设置在衬底100与第一芯轴层310之间的第一掩膜层210,即,步骤s1中仅刻蚀至第一掩膜层210,步骤s4中以第一侧壁511为掩膜依次对预定基板中的第一掩膜层210和衬底100进行刻蚀,最终得到如图7所示的包括衬底鳍片110与第一掩膜结构211的鳍片结构10。

102.作为本发明的一种可选实施方式,半导体工艺设备的控制器可以为先进工艺控制(advanced process control,apc)系统,由先进工艺控制系统在进行每次半导体工艺时,实时将扫描电子显微镜或光学线宽测量机台检测得到的第一芯轴311的宽度值以及最终将得到的不同类型的鳍片间距的数据自动收入,并对第一芯轴311宽度值与衡量鳍片间距的数值(如,间距漂移α-β)之间的对应关系做拟合,如图13所示,即可实时得到当前与鳍片间距最均匀(间距漂移α-β趋近于零)对应的第一芯轴311的最优宽度值。

103.作为本发明的一种可选实施方式,调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节具体包括:

104.根据重新确定的第一芯轴311的目标宽度值,调节对第一芯轴层310进行刻蚀的步骤中的刻蚀参数,形成第二工艺条件,其中,刻蚀参数包括刻蚀时间、刻蚀气体流量、温度中的至少一者。

105.在本发明的其他实施方式中,该半导体工艺也可以是自对准四重图形工艺,具体地,如图14所示,预定基板包括位于衬底100上且由下至上依次层叠设置的第二芯轴层320和第一芯轴层310;

106.对预定基板进行刻蚀,以在基底上形成多个鳍片结构10的步骤s4具体包括:

107.步骤s41、以第一侧壁511为掩膜对第二芯轴层320进行刻蚀,得到多个第二芯轴321(如图18至图20所示);

108.步骤s42、在每个第二芯轴321的两侧制作第二侧壁521(如图20至图23所示);

109.步骤s43、以第二侧壁521为掩膜对衬底100进行刻蚀,以在衬底100上形成多个鳍片结构10(如图23至图25所示)。

110.在此情况下,如图26、图27所示,每个第一芯轴311的两侧形成的两个第一侧壁511对应于两个第二芯轴321,每个第二芯轴321的两侧形成的第二侧壁521对应于最终形成的一对鳍片结构10,即,每个第一芯轴311对应于两对鳍片结构10(以下称这两对鳍片结构10为一组鳍片结构10)。此时,鳍片结构10之间的间距存在三种类型,一种是每组鳍片结构10中两个第二芯轴321对应的两对鳍片结构10之间的间距β,一种是不同组的相邻两鳍片结构10之间的间距γ,还有一种是每个第二芯轴321对应的一对鳍片结构10之间的间距α。

111.其中,间距β和间距γ均与第一芯轴311的宽度值相关,第一芯轴311宽度值过小时会导致每个第一芯轴311对应的一对第二芯轴321之间的间距较小,进而导致每组鳍片结构10中两对鳍片结构10之间的间距β较小,同时还会导致对应于不同第一芯轴311的相邻两第

二芯轴321之间的间距较大,进而导致不同组的相邻鳍片结构10之间的间距γ较大(即图29中左侧示意图所示);反之,第一芯轴311宽度值过大时会导致间距β较大、间距γ较小(即图29中右侧示意图所示),理想状况下间距β与间距γ的大小一致(即图29中中间示意图所示)。因此,可以通过间距β与间距γ之间的差值β-γ衡量鳍片结构10间距的均匀程度,并根据β-γ对第一芯轴311的宽度值进行反馈调节。

112.因此,相应地,基于第一芯轴311的宽度值以及对应的鳍片结构10之间的间距,判断多个鳍片结构10之间的间距趋于一致的步骤具体可以包括:

113.步骤s621、计算多个第一芯轴311对应的多组鳍片结构10中两个第二芯轴321对应的两对鳍片结构10之间的间距β的第一平均值与多对相邻且对应于不同组的鳍片结构10之间的间距γ的第二平均值

114.步骤s622、判断第一平均值和第二平均值之间的第二差值是否在预设范围内,若第二差值超出预设范围,则多个鳍片结构10之间的间距不一致。

115.进而,调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节的步骤具体可以包括:

116.将第一芯轴311的宽度值和第二差值做一一对应关系并做拟合,寻找在预设范围内的第一芯轴311的目标宽度值;

117.调整第一工艺条件为第二工艺条件,以使在后形成的第一芯轴311的宽度值满足目标宽度值。

118.考虑到实际检测以及对刻蚀参数进行调节时存在一定误差,为避免频繁调节刻蚀参数,以保证生产效率,作为本发明的一种优选实施方式,第二预设范围为大于等于-0.5nm且小于等于0.5nm,即,在间距β的第一平均值与间距γ的第二平均值之间的第二差值的大小在0.5nm内时,则认为与第一芯轴311宽度值存在对应关系的鳍片结构10之间的间距总体均匀,无需对刻蚀第一芯轴311时的刻蚀参数进行调节。

119.为避免步骤s1中刻蚀形成多个第一芯轴311以及步骤s41中刻蚀形成多个第二芯轴321时刻穿至衬底100,作为本发明的一种优选实施方式,如图14所示,该预定基板还包括层叠设置在第二芯轴层320与第一芯轴层310之间的第一掩膜层210,以及层叠设置在衬底100与第二芯轴层320之间的第二掩膜层220。

120.即,步骤s1中仅刻蚀至第一掩膜层210,步骤s41中以第一侧壁511为掩膜依次对预定基板中的第一掩膜层210和第二芯轴层320进行刻蚀,得到如图19所示结构;步骤s43中以第二侧壁521为掩膜依次对预定基板中的第二掩膜层220和衬底100进行刻蚀,最终得到如图25所示的包括衬底鳍片110与第二掩膜结构221的鳍片结构10。

121.即,以第二侧壁521为掩膜对衬底100进行刻蚀的步骤s43具体包括:

122.以第二侧壁521为掩膜对第二掩膜层220进行刻蚀,得到多个第二掩膜结构221,如图23至图24所示;

123.以第二侧壁521为掩膜,对衬底100进行刻蚀,得到多个鳍片结构10,如图24至图25所示。

124.作为本发明的一种可选实施方式,第一侧壁511可以通过刻蚀工艺得到,即,先在

第一芯轴311上制作完整膜层,再对该膜层进行刻蚀得到第一芯轴311,具体地:如图2至图4、图15至图17所示,步骤s1中,在每个第一芯轴311的两侧形成第一侧壁511的步骤具体包括:

125.在第三工艺条件下,在第一芯轴311的表面沉积第一侧壁层510(如图2至图3、图15至图16所示);

126.刻蚀第一侧壁层510,形成顶面裸露的第一芯轴311和竖直的第一侧壁511(如图3至图4、图16至图17所示)。

127.作为本发明的一种可选实施方式,该半导体工艺方法还包括,在刻蚀得到第一芯轴311以及第二芯轴321后,去除芯轴结构(第一芯轴311或第二芯轴321)上方的残留膜层,以免芯轴结构顶部残留的结构影响侧壁层(第一侧壁层510、第二侧壁层520)的正常沉积。

128.本发明的发明人在研究中还发现,在自对准四重图形工艺中,鳍片结构10间距的均匀程度还与第一侧壁层510的厚度相关,具体地,如图26、图27所示,第一侧壁层510的厚度决定了每个第一芯轴311的两侧形成的第一侧壁511的宽度值,进而决定每个第二芯轴321的宽度值。

129.因此,第一侧壁层510的厚度过小会导致每个第二芯轴321的宽度值过小,进而导致每个第二芯轴321对应的两个第二侧壁521的间距过小,使每个第二芯轴321对应的一对鳍片结构10之间的间距α过小,并导致对应于不同第二芯轴321的相邻两鳍片结构10之间的间距过大,即,使每组鳍片结构10中两个第二芯轴321对应的两对鳍片结构10之间的间距β以及不同组的相邻两鳍片结构10之间的间距γ过大。反之,第一侧壁层510的厚度过大会导致间距α过大,间距β与间距γ过小。

130.因此,为进一步提高鳍片结构10间距的均匀程度,作为本发明的一种优选实施方式,可以通过间距α与其他类型的间距(例如,间距β、间距γ)之间的差值衡量鳍片结构10间距的均匀程度,并根据该差值对第一侧壁层510的厚度进行反馈调节。

131.具体地,该半导体工艺方法还包括:

132.获得第一侧壁层510的厚度值;

133.建立第一侧壁层510的厚度值和多个第二芯轴321对应的每对鳍片结构10之间的间距α的第三平均值的对应关系;

134.计算多个第二芯轴321对应的每对鳍片结构10之间的间距α的第三平均值以及第一平均值与第二平均值之间的第四平均值以得到第四平均值与第三平均值之间的第三差值

135.建立第一侧壁层510的厚度值与第三差值之间的对应关系;

136.判断第四平均值与第三平均值之间的第三差值是否在预设范围内,若第三差值超出预设范围,则调整第三工艺条件为第四工艺条件,通过第四工艺条件对在后执行半导体工艺时第一侧壁511的宽度值进行调节,以使第三差值

趋近于零。

137.考虑到实际检测以及对沉积第一侧壁层510的参数进行调节时存在一定误差,为避免频繁调节工艺参数,以保证生产效率,作为本发明的一种优选实施方式,第三预设范围为大于等于-0.5nm且小于等于0.5nm,即,当第三差值的大小在0.5nm内时,则认为与第一侧壁层510厚度存在对应关系的鳍片结构10之间的间距总体均匀,无需对沉积第一侧壁层510时的工艺参数进行调节。

138.作为本发明的一种可选实施方式,调整第三工艺条件为第四工艺条件具体包括:根据重新确定的第一侧壁层510的目标厚度,调节对第一芯轴层310进行沉积的沉积参数,形成第四工艺条件,其中,沉积参数包括沉积时间、沉积气体流量、温度中的至少一者。

139.作为本发明的一种优选实施方式,每执行预定数量次步骤s1时执行一次步骤s6,即,每加工多片晶圆后,基于鳍片间距的均匀程度对半导体工艺设备的工艺参数进行一次校准,从而避免频繁调节工艺参数,提高半导体工艺效率。

140.作为本发明的一种可选实施方式,第二侧壁521也可以通过刻蚀工艺得到,即,先在第二芯轴321上制作完整膜层,再对该膜层进行刻蚀得到第一芯轴311,具体地:如图2至图4、图15至图17所示,步骤s1中,在每个第一芯轴311的两侧形成第一侧壁511的步骤具体包括:

141.在第二芯轴321的表面沉积第二侧壁层520(如图20至图21所示);

142.刻蚀第二侧壁层520,形成顶面裸露的第二芯轴321和竖直的第二侧壁521(如图21至图22所示)。

143.作为本发明的第二个方面,提供一种半导体装置系统,该半导体装置系统用于执行本发明实施例提供的半导体工艺方法。

144.本发明提供的半导体装置系统能够根据前面执行半导体工艺时第一芯轴311的宽度值与鳍片间距(即结构10之间的间距)之间的对应关系,对下一次执行半导体工艺时第一芯轴311的宽度值进行调节,以使多个鳍片结构10之间的间距趋于一致,从而能够在量产过程中根据前面多次执行工艺的工艺结果实时对下一次执行工艺时第一芯轴311的宽度值进行反馈调节,进而实时稳定维持鳍片间距的均匀性,保证了产品性能、提高了产品良率。

145.作为本发明的一种可选实施方式,该半导体装置系统包括半导体工艺设备、间隙检测装置和控制器,半导体工艺设备用于形成鳍片结构10,间隙检测装置用于检测鳍片结构10之间的间距,控制器用于基于第一芯轴311的宽度值以及对应的鳍片结构10之间的间距,判断多个鳍片结构10之间的间距趋于一致,若不一致,则调整第一工艺条件为第二工艺条件,通过第二工艺条件对在后执行半导体工艺时第一芯轴311的宽度值进行调节。

146.作为本发明的一种可选实施方式,间隙检测装置可以为特征尺寸测量用扫描电子显微镜或者光学线宽测量机台,控制器可以为先进工艺控制系统,先进工艺控制系统在进行每次半导体工艺时,实时将扫描电子显微镜或光学线宽测量机台检测得到的第一芯轴311的宽度值以及最终得到中不同类型的鳍片间距的数据自动收入,并建立第一芯轴311宽度值与衡量鳍片间距的数值之间的对应关系。

147.例如,在半导体工艺为自对准四重图形工艺的情况下,先进工艺控制系统能够建立不同第一芯轴311宽度值(cd1、cd2、cd3)与三种类型的鳍片间距(每组鳍片结构10中两个

第二芯轴321对应的两对鳍片结构10之间的间距β、不同组的相邻两鳍片结构10之间的间距γ、以及每个第二芯轴321对应的一对鳍片结构10之间的间距α)之间的对应关系。如图28所示,基于前述分析,在四重图形工艺中第一芯轴311的宽度值主要影响间距β和间距γ,因此,由图像可知,当第一芯轴311的宽度值为cd3时,间距β与间距γ最为接近,因此可将cd3确定为最优的第一芯轴311尺寸,实现反馈控制。

148.需要说明的是,图28所示情况只是为便于理解而提供的示意性实施例,在实际分析中控制器需记录大量数据并通过图13所示方式对这些数据进行拟合分析,以保证调节工艺参数(例如,第一芯轴311的宽度值对应的刻蚀参数或者第一侧壁层510厚度对应的沉积工艺的工艺参数)的精确性。

149.作为本发明的一种可选实施方式,该半导体装置系统还包括膜厚检测装置,膜厚检测装置用于检测沉积在第一芯轴311上的第一侧壁层510的厚度值。

150.可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1