高压隔离器件及其制作方法与流程

本公开的实施例主要涉及半导体领域,并且更具体地,涉及高压隔离器件及其制作方法。

背景技术:

1、高压隔离在汽车系统以及其他工业领域中十分常见,其通过隔离防护的方式可以消除高电压与接地电压之间的电位差对半导体元器件的不利影响。近年来,采用电容式或电感式的高压隔离器件变得越来越普遍。然而,传统的高压隔离器件的结构比较复杂,制作工艺中包含多次掩膜(mask)操作,因此增加了工艺难度和成本。此外,传统的高压隔离器件存在成品率低、导电性能受限以及内部应力不稳定等问题。如何提供一种具有简化结构并且便于制作的高压隔离器件是当前亟待解决的问题。

技术实现思路

1、根据本公开的示例实施例,提供了一种新的高压隔离器件制作方案。

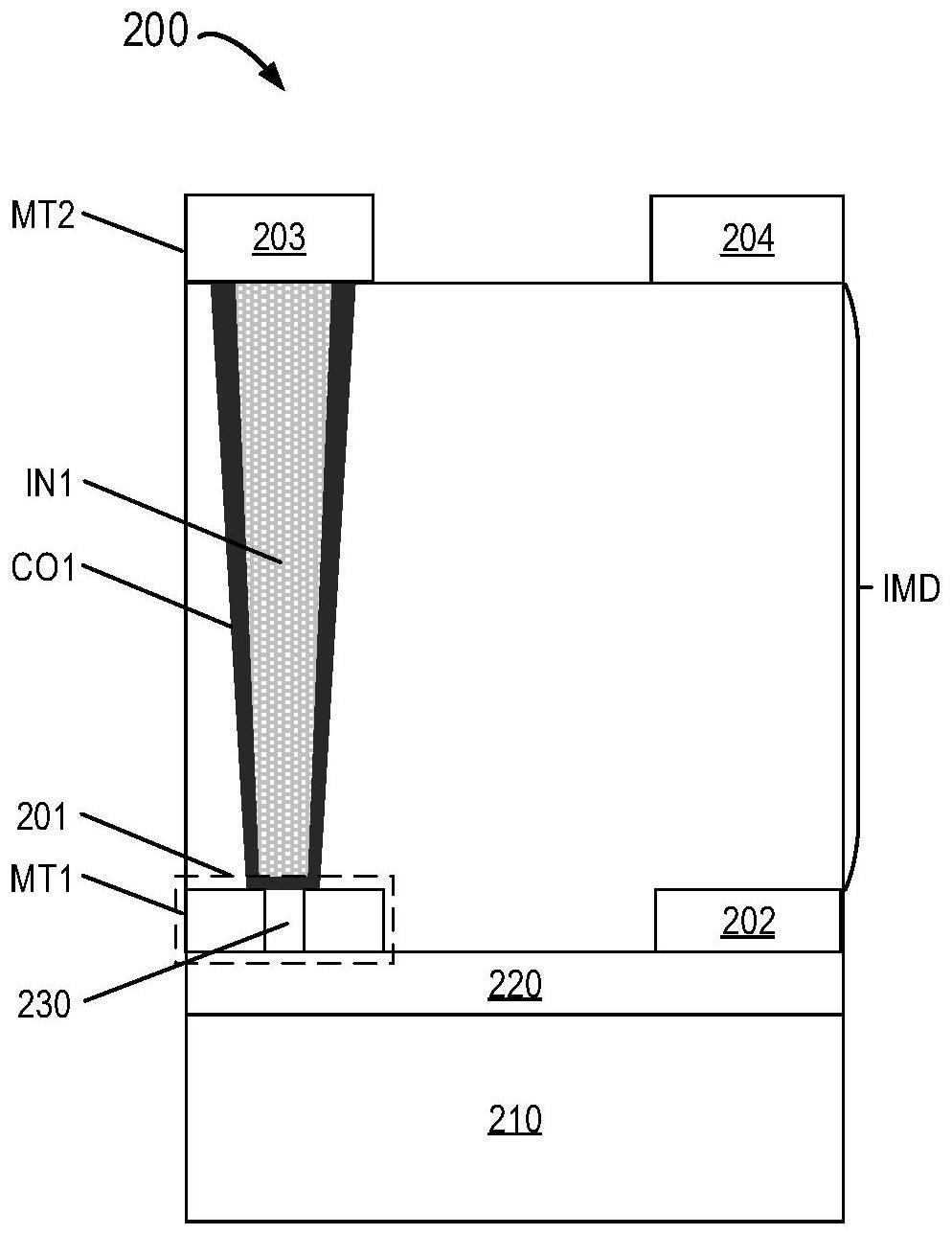

2、在本公开的第一方面中,提供了一种高压隔离器件,包括:第一金属层,具有彼此绝缘的第一部分和第二部分;第二金属层,位于所述第一金属层之上,并且具有彼此绝缘的第三部分和第四部分,所述第三部分与所述第一部分相对应,所述第四部分与所述第二部分相对应;电介质层,位于所述第一金属层与所述第二金属层之间,并且具有连通所述第一部分与所述第三部分的沟槽,其中在所述沟槽内布置有用于电连接所述第一部分与所述第三部分的导电材料,并且在布置有所述导电材料的所述沟槽中还填充有绝缘材料;以及阻挡层,位于所述第一金属层下方,其中所述阻挡层被布置为位于半导体衬底中的半导体器件及其布线上,并且所述第一金属层的所述第一部分与所述半导体器件电连接。

3、在某些实施例中,所述第一部分被纵向开槽。

4、在某些实施例中,所述第一部分是铜层。

5、在某些实施例中,所述沟槽是通过蚀刻所述电介质层而形成的,并且所述阻挡层被布置为在所述电介质层被蚀刻期间保护所述半导体衬底中的半导体器件及其布线不受破坏。

6、在某些实施例中,所述沟槽被布置为将所述半导体器件及其布线电连接至焊盘,所述焊盘是所述第二金属层中裸露于其上表面的钝化层的部分。

7、在某些实施例中,所述第一金属层的所述第二部分与所述第二金属层的所述第四部分被布置为形成高压隔离电容和高压隔离电感中的一个。

8、在某些实施例中,所述沟槽的与所述第三部分相连的开口的第二宽度大于或等于0.25um。优选地,该第二宽度大于或等于0.5um。优选地,该第二宽度大于或等于1um。优选地,该第二宽度大于或等于2um。优选地,该第二宽度大于或等于5um。优选地,该第二宽度大于或等于10um。

9、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述高压隔离器件的耐压值相关联。

10、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度在0.5um到20um的范围内。优选地,该厚度在1um到20um的范围内。优选地,该厚度在3um到20um的范围内。优选地,该厚度在6um到20um的范围内。优选地,该厚度在10um到20um的范围内。

11、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述沟槽的与所述第三部分相连的开口的第二宽度的比值小于3:1。

12、在某些实施例中,所述电介质层包括多层电介质。

13、在本公开的第二方面中,提供了一种电子器件,包括:如本公开的第一方面所述的高压隔离器件;以及附加高压隔离器件,其中所述附加高压隔离器件至少包括:第三金属层,与所述第二金属层的所述第四部分电连接;第四金属层,位于与所述半导体器件不同的附加半导体器件及其布线上并且与所述附加半导体器件电连接;以及附加电介质层,位于所述第三金属层与所述第四金属层之间。

14、在本公开的第三方面中,提供了一种制作高压隔离器件的方法,包括:在包含半导体器件及其布线的半导体衬底上蚀刻阻挡层;通过沉积和蚀刻在所述阻挡层上形成第一金属层,所述第一金属层具有彼此绝缘的第一部分和第二部分,并且所述第一金属层的所述第一部分与所述半导体器件电连接;在所述第一金属层上沉积电介质层;蚀刻所述电介质层,直至露出所述阻挡层,以形成沟槽;至少沿所述沟槽的侧壁和底部布置导电材料;在所述沟槽中的由所述导电材料形成的腔体内至少填充绝缘材料;以及通过沉积和蚀刻形成第二金属层,所述第二金属层具有彼此绝缘的第三部分和第四部分,所述第三部分与所述第一部分相对应,所述第四部分与所述第二部分相对应,其中所述导电材料用于电连接所述第一部分与所述第三部分。

15、在某些实施例中,所述第一部分是纵向开槽的铜层。

16、在某些实施例中,布置所述导电材料包括:在形成所述沟槽的所述电介质层的露出表面上布置所述导电材料,其中所述导电材料是堆叠层,所述堆叠层包括:第一阻挡层,与所述沟槽侧壁和底部接触;第二阻挡层,与所述绝缘材料接触;以及导电金属层,位于所述第一阻挡层与所述第二阻挡层之间。

17、在某些实施例中,至少填充所述绝缘材料包括:在所述导电材料的露出表面上沉积所述绝缘材料。

18、在某些实施例中,形成所述第二金属层包括:通过平坦化工艺移除所述导电材料和所述绝缘材料的位于所述电介质层上方的部分,以露出所述电介质层;以及在所述电介质层上通过沉积和蚀刻形成所述第二金属层,所述第二金属层与所述导电材料电连接。

19、在某些实施例中,蚀刻所述电介质层包括:在所述电介质层上沉积硬掩膜层;在所述硬掩膜层上沉积光刻胶层,所述光刻胶层被显影,以定义用于形成所述沟槽的蚀刻位置;移除所述光刻胶层;在所述蚀刻位置处蚀刻所述硬掩膜层;以及通过蚀刻被经蚀刻的所述硬掩膜层覆盖的所述电介质层,形成所述沟槽。

20、在某些实施例中,形成所述第二金属层包括:通过平坦化工艺移除所述导电材料和所述绝缘材料的位于所述硬掩膜层上方的部分;移除所述硬掩膜层;以及在所述电介质层上通过沉积和蚀刻形成所述第二金属层,所述第二金属层与所述导电材料电连接。

21、在某些实施例中,形成所述第一金属层包括:在所述半导体衬底上形成金属层;在所述金属层上沉积阻挡层;通过蚀刻工艺移除所述阻挡层的一部分,以剩余所述阻挡层的在用于形成所述沟槽的蚀刻位置附近的另一部分;以及通过蚀刻工艺将所述金属层形成为所述第一金属层的所述第一部分和所述第二部分,所述阻挡层的所述另一部分位于所述第一部分上。

22、在某些实施例中,所述沟槽的与所述第一部分相连的开口的第一宽度小于或等于所述沟槽的与所述第三部分相连的开口的第二宽度。

23、在某些实施例中,所述沟槽的与所述第三部分相连的开口的第二宽度大于或等于0.25um。优选地,该第二宽度大于或等于0.5um。优选地,该第二宽度大于或等于1um。优选地,该第二宽度大于或等于2um。优选地,该第二宽度大于或等于5um。优选地,该第二宽度大于或等于10um。

24、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述高压隔离器件的耐压值相关联。

25、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度在0.5um到20um的范围内。优选地,该厚度在1um到20um的范围内。优选地,该厚度在3um到20um的范围内。优选地,该厚度在6um到20um的范围内。优选地,该厚度在10um到20um的范围内。

26、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述沟槽的与所述第三部分相连的开口的第二宽度的比值小于3:1。

27、在某些实施例中,所述电介质层的厚度大于6um,且所述沟槽的与所述第三部分相连的开口的第二宽度大于3um。

28、在某些实施例中,所述电介质层包括经平坦化的多层电介质。

29、在本公开的第四方面中,提供了一种高压隔离器件,包括:第一金属层,具有彼此绝缘的第一部分和第二部分;第二金属层,位于所述第一金属层之上,并且具有彼此绝缘的第三部分和第四部分,所述第三部分与所述第一部分相对应,所述第四部分与所述第二部分相对应;以及电介质层,位于所述第一金属层与所述第二金属层之间,并且具有连通所述第一部分与所述第三部分的沟槽,其中在所述沟槽内布置有用于电连接所述第一部分与所述第三部分的导电材料,并且其中所述导电材料至少包括:第一导电部,沿所述沟槽的侧壁和底部形成;以及第二导电部,沿所述第一导电部的侧壁和底部形成,所述第二导电部与第一导电部的材料不同。

30、在某些实施例中,第一导电部的材料包括钨且第二导电部的材料包括铜或铝铜。

31、在某些实施例中,所述第二导电部中形成有气隙。

32、在某些实施例中,在布置有所述导电材料的所述沟槽中还填充有绝缘材料,所述绝缘材料位于所述第二导电部限定的内部区域中。

33、在某些实施例中,所述绝缘材料包括沿所述第二导电部的梭形腔体布置的绝缘部以及在布置所述绝缘部时形成的气隙。

34、在某些实施例中,所述绝缘材料包括沿所述第一导电部布置的、位于所述第一导电部与所述第二导电部之间的绝缘部以及在布置所述第二导电部时形成的气隙。

35、在某些实施例中,第二导电部通过利用物理气相沉积工艺或化学气相沉积工艺形成。

36、在某些实施例中,所述第一金属层被布置为位于半导体衬底中的半导体器件及其布线上并且所述第一金属层的所述第一部分与所述半导体器件电连接。

37、在某些实施例中,所述沟槽被布置为将所述半导体器件及其布线电连接至焊盘,所述焊盘是所述第二金属层中裸露于其上表面的钝化层的部分。

38、在某些实施例中,所述第一金属层的所述第二部分与所述第二金属层的所述第四部分被布置为形成高压隔离电容和高压隔离电感中的一个。

39、在某些实施例中,所述沟槽的与所述第三部分相连的开口的第二宽度大于或等于0.25um。

40、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述高压隔离器件的耐压值相关联。

41、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度在0.5um到20um的范围内。优选地,该厚度在1um到20um的范围内。优选地,该厚度在3um到20um的范围内。优选地,该厚度在6um到20um的范围内。优选地,该厚度在10um到20um的范围内。

42、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述沟槽的与所述第三部分相连的开口的第二宽度的比值小于3:1。

43、在本公开的第五方面中,提供了一种制作高压隔离器件的方法,包括:在包含半导体器件及其布线的半导体衬底上通过沉积和蚀刻形成第一金属层,所述第一金属层具有彼此绝缘的第一部分和第二部分;在所述第一金属层上沉积电介质层;蚀刻所述电介质层,直至露出所述第一部分,以形成沟槽;至少沿所述沟槽的侧壁和底部沉积导电材料的第一导电部;沿所述第一导电部的侧壁和底部形成所述导电材料的第二导电部,所述第二导电部与第一导电部的材料不同;以及通过沉积和蚀刻形成第二金属层,所述第二金属层具有彼此绝缘的第三部分和第四部分,所述第三部分与所述第一部分相对应,所述第四部分与所述第二部分相对应,其中所述导电材料用于电连接所述第一部分与所述第三部分。

44、在某些实施例中,第一导电部的材料包括钨且第二导电部的材料包括铜或铝铜。

45、在某些实施例中,所述第二导电部中形成有气隙。

46、在某些实施例中,在形成所述第二导电部之后,还包括:沿所述第二导电部的梭形腔体沉积绝缘材料,以使所述绝缘材料内形成气隙。

47、在某些实施例中,形成所述第二导电部包括:通过利用物理气相沉积工艺或化学气相沉积工艺沿所述第一导电部的侧壁和底部形成所述第二导电部,气隙在形成所述第二导电部的过程中被形成。

48、在某些实施例中,形成所述第二导电部包括:至少沿所述第一导电部的侧壁沉积形成绝缘材料;以及通过利用物理气相沉积工艺或化学气相沉积工艺沿所述绝缘材料的侧壁和底部形成所述第二导电部,气隙在形成所述第二导电部的过程中被形成。

49、在某些实施例中,形成所述第二金属层包括:通过平坦化工艺移除所述导电材料和所述绝缘材料的位于所述电介质层上方的部分,以露出所述电介质层;以及在所述电介质层上通过沉积和蚀刻形成所述第二金属层,所述第二金属层与所述导电材料电连接。

50、在某些实施例中,蚀刻所述电介质层包括:在所述电介质层上沉积硬掩膜层;在所述硬掩膜层上沉积光刻胶层,所述光刻胶层被显影,以定义用于形成所述沟槽的蚀刻位置;移除所述光刻胶层;在所述蚀刻位置处蚀刻所述硬掩膜层;以及通过蚀刻被经蚀刻的所述硬掩膜层覆盖的所述电介质层,形成所述沟槽。

51、在某些实施例中,形成所述第二金属层包括:通过平坦化工艺移除所述导电材料和所述绝缘材料的位于所述硬掩膜层上方的部分;移除所述硬掩膜层;以及在所述电介质层上通过沉积和蚀刻形成所述第二金属层,所述第二金属层与所述导电材料电连接。

52、在某些实施例中,形成所述第一金属层包括:在所述半导体衬底上形成金属层;在所述金属层上沉积附加阻挡层;通过蚀刻工艺移除所述附加阻挡层的一部分,以剩余所述附加阻挡层的在用于形成所述沟槽的蚀刻位置附近的另一部分;以及通过蚀刻工艺将所述金属层形成为所述第一金属层的所述第一部分和所述第二部分,所述附加阻挡层的所述另一部分位于所述第一部分上。

53、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度在0.5um到20um的范围内。优选地,该厚度在1um到20um的范围内。优选地,该厚度在3um到20um的范围内。优选地,该厚度在6um到20um的范围内。优选地,该厚度在10um到20um的范围内。

54、在某些实施例中,所述电介质层的位于所述第二部分与所述第四部分之间的部分的厚度与所述沟槽的与所述第三部分相连的开口的第二宽度的比值小于3:1。

55、在某些实施例中,所述电介质层的厚度大于6um,且所述沟槽的与所述第三部分相连的开口的第二宽度大于3um。

56、提供

技术实现要素:

部分是为了以简化的形式来介绍一系列概念,它们在下文的具体实施方式中将被进一步描述。发明内容部分不旨在标识本公开的关键特征或必要特征,也不旨在限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!