只读存储器的位错失效分析方法与流程

1.本发明涉及一种半导体集成电路制造方法,特别是涉及一种只读存储器(rom)的位错失效分析(fa)方法。

背景技术:

2.对于rom产品,其中有一种rom产品是通过将信息由光罩(mask)转移到存储单元阵列(cell array)内,使用此方式制造成本较低,常用于电子设备的开启或存储智能卡类产品的一些基本程序。这种产品通过定义有源区(active area,aa),或控制有源区是否与“行或列”相连,从而定义数据为“0”或“1”;其中有源区是由场氧如浅沟槽场氧环绕区域的半导体衬底组成,源区和漏区通常自对准形成于多晶硅栅两侧的有源区,位于源区和漏区之间的被多晶硅栅覆盖的沟道区也形成于有源区中;定义有源区为对源区、漏区或沟道区的形成区域进行定义,源区、漏区和沟道区的形成区域为有源区时存储的数据以及在源区、漏区或沟道区的形成区域为场氧时存储的数据不同;控制有源区是否与“行或列”相连是指,源区、漏区和沟道区的形成区域都为有源区,但是通过控制源区或漏区和“行或列”是否相连来定义相应的数据。rom一经制造完成,使用者无法修改,所以根据rom的这种特性,做一些常规的失效定位分析。

3.针对rom失效,可以进行电性方面失效分析(efa),例如:能通过测试仪或一些板卡对芯片上电,使其吐出一个内部的实际代码。如图1所示,是现有只读存储器发生位错失效时定义数据和读取数据的比较图;图表101中显示了mask定义数据,图表102显示了实际读取的数据,数据都为二进制数据。可以看出,图表102中的框103所示的列数据都为0,故efa仅能得到失效的列,并不能得到失效的位。

4.物理层面失效分析(pfa)需要对先失效位置进行精确定位,之后对定位的失效位置进行tem样品制作以及tem成像和分析。

5.现有方法利用电压衬度像(voltage contrast,vc)来见失效位置定义。电压衬度像的成像机理包括:当电子束或离子束扫描样品表面时,会与表面产生非弹性碰撞,并放射出一些低能如《50ev的二次电子。这些二次电子一般仅能离开表面30nm以内,利用侦测器前端外加几百伏特的电压将这些二次电子吸收,并成像。样品表面的电位会影响二次电子的产率,电位越高放射二次电子量越少,电位越低放射量越多,利用此电压衬度像可以判断连接线包括金属、多晶硅或接触孔等连线的短路与断路。

6.实际应用中,一般采用低压电子束或者高压离子束进行电压衬度实验,rom中的存储单元的源区(source)和漏区(drain)均为同一种类型如n型的注入,此时若半导体衬底aa损伤,我们无法通过接触孔(contact)的电压衬度像来确认异常所在位置。如图2所示,是现有只读存储器的位错失效分析方法中形成的电压衬度像104;电压衬度像104中各接触孔的图像完全正常,并不能分辨出哪些图像是异常的,仅能通过图1中的框103的列的坐标在电压衬度像104中找到对应的失效列103a。所以,通过图2所示的电压衬度像104,只能通过二进制代码换算的物理地址推算出失效列103a。由于衬底注入均为n型,无法通过vc判断具体

的失效位置,导致分析无法继续下去。

技术实现要素:

7.本发明所要解决的技术问题是提供一种只读存储器的位错失效分析方法,能通过电压衬度像快速定位位错失效位置。

8.为解决上述技术问题,本发明提供的只读存储器的位错失效分析方法包括:

9.步骤一、将只读存储器的后道金属线层都剥离并使接触孔的顶部表面露出。

10.步骤二、在失效模块外选定第一切割区域并对所述第一切割区域进行切割形成第一凹槽,所述第一凹槽沿所述只读存储器的存储单元阵列的列方向延伸;由同一行的各所述存储单元的多晶硅栅连接在一起形成多晶硅条,各行多晶硅条的侧面在所述第一凹槽的侧面暴露,所述第一凹槽还将半导体衬底表面暴露。

11.步骤三、在所述第一凹槽的内侧表面形成第一金属层,所述第一金属层使各行所述多晶硅条和所述半导体衬底都接触并接地。

12.步骤四、对所述只读存储器件进行电压衬度成像并形成第一电压衬度像,所述第一电压衬度像中,接地的所述多晶硅条形成亮图像,结构正常的存储单元的漏极接触孔形成暗图像,在所述失效模块中将漏极接触孔的图像为亮图像的存储单元定位为位错失效位置。

13.进一步改进是,步骤一中,对所述后道金属线层的剥离工艺中包括采用聚焦离子束(fib)进行剥离。

14.进一步改进是,步骤二中,所述失效模块通过对所述位错失效位置进行初步定位形成。

15.进一步改进是,所述初步定位包括在步骤一之前对所述只读存储器进行efa分析得到。

16.进一步改进是,所述efa分析包括对所述只读存储器进行数据读取,当具有列失效时,列失效对应的存储单元列中具有位错失效,将选定包括了失效列的模块作为所述失效模块。

17.进一步改进是,步骤二中,形成所述第一凹槽的切割工艺采用fib刻蚀。

18.进一步改进是,所述fib刻蚀中采用镓离子束进行刻蚀。

19.进一步改进是,在所述fib刻蚀过程中,切割面处会有镓离子残留,步骤三中的所述第一金属层直接由残留在所述第一凹槽的内侧表面的镓层组成。

20.进一步改进是,步骤四中,在所述失效列上寻找亮图像的漏极接触孔并从而实现所述位错失效位置的定位。

21.进一步改进是,步骤四完成后,还包括:

22.进行tem样品制样,所述tem样品中包括所述位错失效位置;

23.对所述tem样品进行tem成像并进行分析。

24.进一步改进是,所述只读存储器的存储单元阵列中,同一列的所述存储单元的漏区通过所述漏极接触孔连接到位线。

25.进一步改进是,所述只读存储器的存储单元阵列中,同一行的所述存储单元的源区在所述半导体衬底中连接在一起并形成源区行。

26.进一步改进是,所述源区行接源线。

27.进一步改进是,在所述存储单元阵列的模块的两侧,各所述多晶硅条的顶部形成有栅极接触孔。

28.进一步改进是,所述源区和所述漏区都为n+掺杂;在所述位错失效位置处,所述漏极接触孔的底部会和所述半导体衬底接触。

29.本发明通过在失效模块外侧切割形成第一凹槽并在第一凹槽内侧表面形成第一金属层,之后再进行电压衬度成像,此时形成的第一电压衬度像中,能使具有位错缺陷的存储单元和结构正常的存储单元的漏极接触孔的图像区分开来,从而实现对位错失效位置的定位,所以,本发明能通过电压衬度像快速定位位错失效位置。

附图说明

30.下面结合附图和具体实施方式对本发明作进一步详细的说明:

31.图1是现有只读存储器发生位错失效时定义数据和读取数据的比较图;

32.图2是现有只读存储器的位错失效分析方法中形成的电压衬度像;

33.图3是本发明实施例只读存储器的位错失效分析方法的流程图;

34.图4a是本发明实施例只读存储器的位错失效分析方法的步骤一的剥离过程中得到的多晶硅体和接触孔的版图;

35.图4b是本发明实施例只读存储器的位错失效分析方法的步骤一的剥离过程中得到的有源区的版图;

36.图5a是本发明实施例只读存储器的位错失效分析方法的步骤二进行切割前的器件结构示意图;

37.图5b是本发明实施例只读存储器的位错失效分析方法的步骤二进行切割后的器件结构示意图;

38.图5c是图5b对应的俯视图;

39.图6a是作为比较的现有只读存储器的位错失效分析方法形成的电压衬度像;

40.图6b是本发明实施例只读存储器的位错失效分析方法的步骤四形成的第一电压衬度像;

41.图7是本发明实施例只读存储器的位错失效分析方法在位错失效位置处形成的tem照片;

42.图8是本发明实施例只读存储器的位错失效分析方法中的位错失效电路示意图。

具体实施方式

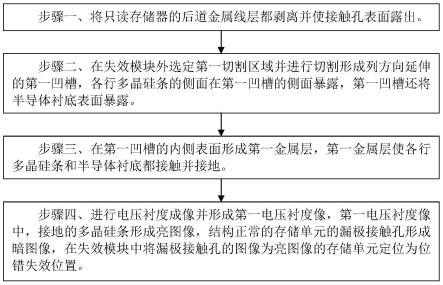

43.如图3所示,是本发明实施例只读存储器的位错失效分析方法的流程图;本发明实施例只读存储器的位错失效分析方法包括:

44.步骤一、将只读存储器的后道金属线层都剥离并使接触孔的顶部表面露出。

45.本发明实施例中,对所述后道金属线层的剥离工艺中包括采用fib进行剥离。

46.如图4a所示,是本发明实施例只读存储器的位错失效分析方法的步骤一的剥离过程中得到的多晶硅体201和接触孔的版图;可以看出,版图显示了:

47.由同一行的多晶硅栅连接形成的多晶硅体201,源区的形成区域位于大括号202对

应的区域中,漏区的形成区域位于大括号203对应的区域中,区域202和203分别位于各条所述多晶硅体201的两侧。图4a中多晶硅体201也用poly表示。

48.接触孔包括形成于漏区顶部的漏极接触孔204a;在多晶硅体201的一侧的端部形成的栅极接触孔204b;在源区行的一侧的端部形成的源极接触孔204c。虚线框205表示位于同一列上的漏极接触孔204a,同一列的漏极接触孔204a会连接到同一根位线(bl)。同一行的所述存储单元的源区在所述半导体衬底中连接在一起并形成源区行。源区行采用sl表示。所述源区行通过源极接触孔204c连接到源线。

49.如图4b所示,是本发明实施例只读存储器的位错失效分析方法的步骤一的剥离过程中得到的有源区206的版图;图4b没有具体显示多晶硅条201的图像,多晶硅条201采用虚线框表示,组成多晶硅条201的多晶硅栅也采用poly gate表示。图4b中也显示了区域202和203分别位于多晶硅条201的两侧。漏区顶部的位线用bl表示。图4b中,有源区206具有图形化结构,通过有源区206的图形化实现编程。一个完整的存储单元的源区、沟道区和漏区的形成区域中都需要形成有源区206,这样存储单元会存储一种数据;如果源区、沟道区或漏区中的一个以上的形成区域采用场氧时,则该存储单元不能导通,从而存储另一种数据。

50.同时请参考图5c所示,所述只读存储器的存储单元阵列中,同一列的所述存储单元的漏区通过所述漏极接触孔204a连接到同一根位线bl。

51.所述只读存储器的存储单元阵列中,同一行的所述存储单元的源区在所述半导体衬底中连接在一起并形成源区行。源区行采用sl表示。所述源区行通过源极接触孔204c连接到源线。

52.所述栅极接触孔204b形成在所述存储单元阵列的模块的两侧的各所述多晶硅条201的顶部;所述源极接触孔204c形成在所述存储单元阵列的模块的两侧的所述源区行的顶部。

53.步骤二、在失效模块外选定第一切割区域并对所述第一切割区域进行切割形成第一凹槽402。

54.所述第一凹槽402沿所述只读存储器的存储单元阵列的列方向延伸;由同一行的各所述存储单元的多晶硅栅连接在一起形成多晶硅条201,各行多晶硅条201的侧面在所述第一凹槽402的侧面暴露,所述第一凹槽402还将半导体衬底表面暴露。

55.本发明实施例中,所述失效模块通过对所述位错失效位置进行初步定位形成。

56.所述初步定位包括在步骤一之前对所述只读存储器进行efa分析得到。efa分析请参考图1所示,所述efa分析包括对所述只读存储器进行数据读取,当具有列失效时,列失效对应的存储单元列中具有位错失效,将选定包括了失效列的模块作为所述失效模块。

57.本发明实施例中,形成所述第一凹槽402的切割工艺采用fib刻蚀。

58.如图5a所示,是步骤二中进行切割前的器件结构示意图;为了便于更直观的理解,图5a中同时给出了俯视图和剖面图,其中,虚线aa左侧为俯视图301,虚线aa右侧为剖面图302,俯视图301中包括了一条所述多晶硅条201上的部分存储单元的结构示意图;剖面图302则是沿图301中的所述多晶硅条201的剖面的结构示意图。

59.俯视图301中显示了多个漏区203a以及形成于漏区203a顶部的漏极接触孔204a;俯视图301中还包括了一个具有位错失效缺陷303的存储单元,具有位错失效缺陷303的存储单元的漏极接触孔单独用标记204a1标出。

60.在剖面图302中显示了半导体衬底401,所述多晶硅条201形成于所述半导体衬底401的表面上;图5a中,在所述半导体衬底401的表面还进行了图形化刻蚀,图形化刻蚀后的半导体衬底401的突出部分单独用标记401a标出。

61.所述源区和所述漏区都为n+掺杂;在所述位错失效位置处,所述漏极接触孔204a1的底部会和所述半导体衬底401接触。

62.在图5a的条件下进行电压衬度成像时,多晶硅条201的图像为暗图像,各所述漏极接触孔204a的图像都为亮图像。这时对所述只读存储器进行电压衬度成像所形成的电压衬度像501如图6a所示,图6a和图2相同,并不能失实现对标记204a1所示的漏极接触孔定位。

63.如图5b所示,是步骤二中进行切割后的器件结构示意图,和图5a相比,图5b中形成有所述第一凹槽402。

64.如图5c所示,是图5b对应的俯视图,可以看出,所述失效模块两端分别设置有所述栅极接触孔204b和所述源极接触孔204c,所述第一凹槽402则位于所述失效模块外侧,故所述第一凹槽402并不会破坏失效现场。

65.步骤三、在所述第一凹槽402的内侧表面形成第一金属层403,所述第一金属层403使各行所述多晶硅条201和所述半导体衬底都接触并接地。

66.本发明实施例中,步骤二的所述fib刻蚀中采用镓离子束进行刻蚀。

67.在所述fib刻蚀过程中,切割面处会有镓离子残留,步骤三中的所述第一金属层403直接由残留在所述第一凹槽402的内侧表面的镓层组成。

68.步骤四、对所述只读存储器件进行电压衬度成像并形成第一电压衬度像,所述第一电压衬度像中,接地的所述多晶硅条201形成亮图像,结构正常的存储单元的漏极接触孔形成暗图像,在所述失效模块中将漏极接触孔的图像为亮图像的存储单元定位为位错失效位置。

69.如图5b所示,对图5b所示结构进行电压衬度成像时,所述多晶硅条201会通过所述第一金属层403接地,所述多晶硅条201的图像为亮图像;和图5a中的多晶硅条201的图像为暗图像正好相反。本发明实施例中,电压衬度成像所述fib扫描实现,fib中接地会呈亮图像。

70.同样,具有位错失效位置处的漏极接触孔204a1也会通过所述半导体衬底401接地,最后呈亮图像。

71.其他功能正常的存储单元的漏极接触孔204a都不接地,故都呈暗图像。故本发明实施例能实现漏极接触孔204a1和正常的漏极接触孔204a的区分,从而能实现位错实失效位置的定位。

72.如图6b所示,是本发明实施例只读存储器的位错失效分析方法的步骤四形成的第一电压衬度像502;图6b是在图5b的基础上形成的整个只读存储器对应的第一电压衬度像502;图6b中的图像503是第一电压衬度像502的白色方框中的放大像。从图像503中可以看出所述多晶硅条201的亮图像,正常位置的漏极接触孔204a的暗图像,位错失效位置的漏极接触孔204a1的亮图像。

73.本发明实施例中,在所述失效列504上寻找亮图像的漏极接触孔204a1并从而实现所述位错失效位置的定位。所述失效列504和图1中的列103对应。

74.步骤四完成后,还包括:

75.进行tem样品制样,所述tem样品中包括所述位错失效位置;

76.对所述tem样品进行tem成像并进行分析。

77.如图7所示,是本发明实施例只读存储器的位错失效分析方法在位错失效位置处形成的tem照片601,图7中还包括tem照片601的方框中的放大照片602,照片601和602中显示了多晶硅条201对应的多晶硅栅,多晶硅栅底部的半导体衬底401,漏区顶部的漏极接触孔204a1。箭头对应的区域具有位错失效缺陷303。

78.如图8所示,是本发明实施例只读存储器的位错失效分析方法中的位错失效电路示意图。存储单元701都由nmos,nmos包括了源区s、漏区d和栅极g,漏区d都通过漏极接触孔204a连接到位线bl,源区s通过源区行sl连接在一起并通过源极接触孔204c接地。在位错失效位置处,位错失效缺陷303会使漏极接触孔204a1和半导体衬底401接触,从而能通过电压衬度像定位。

79.本发明实施例通过在失效模块外侧切割形成第一凹槽402并在第一凹槽402内侧表面形成第一金属层403,之后再进行电压衬度成像,此时形成的第一电压衬度像中,能使具有位错缺陷的存储单元和结构正常的存储单元的漏极接触孔的图像区分开来,从而实现对位错失效位置的定位,所以,本发明实施例能通过电压衬度像快速定位位错失效位置。

80.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1