用于ESD保护的双向双极型器件的制作方法

用于esd保护的双向双极型器件

技术领域

1.本公开一般地涉及静电放电(esd)保护器件及形成esd保护器件的方法。

背景技术:

2.高于提供给电子设备的普通电压的esd电压会损坏这些设备。因此,电子设备经常耦接到esd保护器件以保护其免受此类损坏。当esd电压低于预定水平时,可忽略的电流流经这些esd保护器件。然而,当esd电压超过预定水平时,esd保护器件可能会接通以将电流导离这些设备,从而保护这些设备免受损坏。

3.常规的基于npn(或pnp)的esd保护器件是单向器件,不能直接用于双向esd保护。也就是说,常规的双极型esd保护器件只能支持单极高电压偏置,即只能在一个方向上承受高电压偏置。例如,对于典型的基于npn晶体管的esd保护器件,高电压偏置只能在从npn晶体管的集电极端子到发射极/基极端子(或从pnp晶体管的发射极/基极端子到集电极端子)的方向上施加,以作为有效的esd保护器件工作。否则,如果发射极/基极端子处的电压远高于集电极端子处的电压(例如高出了大于0.7v),则npn晶体管被正向偏置,并可能接通而将电流导离设备,即使当端子之间的电压偏置低于预定水平时也是如此。

技术实现要素:

4.根据各种实施例,提供了一种提供esd保护的半导体器件。所述esd保护器件可以包括衬底,所述衬底包括布置在所述衬底中的双极结型晶体管,包括:第一掺杂区、第二掺杂区和第三掺杂区,所述第二掺杂区设置在所述第一掺杂区和所述第三掺杂区之间,其中所述第二掺杂区具有第一导电类型和第一掺杂浓度,并且所述第一掺杂区和所述第三掺杂区具有第二导电类型和第二掺杂浓度;第一掺杂端子区,其设置在所述第一掺杂区内;第二掺杂端子区,其设置在所述第三掺杂区内;以及掺杂岛区,其设置在所述第二掺杂区内,其中所述第一掺杂端子区、所述第二掺杂端子区和所述掺杂岛区具有所述第二导电类型和第三掺杂浓度,所述第三掺杂浓度高于所述第一掺杂浓度和所述第二掺杂浓度;以及第一导电端子,其耦接到所述第一掺杂端子区;第二导电端子,其耦接到所述第二掺杂端子区;以及绝缘层,其布置在所述第一导电端子和所述第二导电端子之间的所述衬底上,所述绝缘层至少覆盖所述第二掺杂区。

5.根据各种实施例,提供了一种用于形成esd保护器件的方法。所述方法可以包括:提供衬底,所述衬底包括布置在所述衬底中的双极结型晶体管,所述提供衬底包括:提供第一掺杂区、第二掺杂区和第三掺杂区,所述第二掺杂区设置在所述第一掺杂区和所述第三掺杂区之间,其中所述第二掺杂区具有第一导电类型和第一掺杂浓度,并且所述第一掺杂区和所述第三掺杂区具有第二导电类型和第二掺杂浓度;提供设置在所述第一掺杂区内的第一掺杂端子区;提供设置在所述第三掺杂区内的第二掺杂端子区;以及提供设置在所述第二掺杂区内的掺杂岛区,其中所述第一掺杂端子区、所述第二掺杂端子区和所述掺杂岛区具有所述第二导电类型和第三掺杂浓度,所述第三掺杂浓度高于所述第一掺杂浓度和所

述第二掺杂浓度;以及提供耦接到所述第一掺杂端子区的第一导电端子;提供耦接到所述第二掺杂端子区的第二导电端子;以及提供布置在所述第一导电端子和所述第二导电端子之间的所述衬底上的绝缘层,所述绝缘层至少覆盖所述第二掺杂区。

6.有利实施例的其他特征在从属权利要求中提供。

附图说明

7.在附图中,相同的参考标号通常指示所有不同视图中的相同部件。附图不一定按比例绘制,而是通常强调说明本发明的原理。在以下描述中,参考以下附图描述了各种实施例,其中:

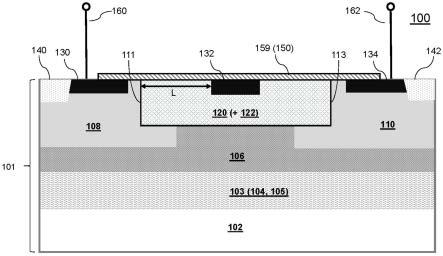

8.图1示出了根据各种非限制性实施例的双向esd器件的简化截面图。

9.图2示出了根据各种非限制性实施例的图1的双向esd器件的简化示意图。

10.图3示出了针对通过使用技术计算机辅助设计(tcad)模拟esd保护器件而获得的不同基部长度(base length)的图1的esd保护器件的性能图表。

11.图4a和4b示出了针对使用tcad模拟esd保护器件而获得的不同电流的图1的esd保护器件的一部分的电流密度(current density)图。

12.图5示出了根据替代的非限制性实施例的esd保护器件的简化截面图。

13.图6示出了根据另外的替代的非限制性实施例的esd保护器件的简化截面图。

14.图7示出了根据另外的替代的非限制性实施例的esd保护器件的简化截面图。

15.图8示出了根据另外的替代的非限制性实施例的esd保护器件的简化截面图。

16.图9a示出了根据另外的替代的非限制性实施例的esd保护器件的简化截面图。

17.图9b示出了图9a的esd保护器件的简化示意图。

18.图10a和10b示出了根据各种非限制性实施例的用于形成esd保护器件的方法的流程图。

具体实施方式

19.本公开的实施例一般地涉及半导体器件。更具体地,实施例涉及提供半导体器件中的esd保护器件。例如,这种esd保护器件可以被并入集成电路(ic)中。半导体器件或ic可以与例如但不限于消费电子产品的设备一起使用。用于将esd保护器件集成到半导体器件中的现有方法需要多个蚀刻掩模和较大占位面积(footprint)。一些实施例涉及具有较小占位面积并且可以在制造过程中以减少数量的蚀刻掩模集成到半导体器件中的esd保护器件。

20.下面参考在附图中示出的非限制性示例,更全面地解释本发明的各方面及其某些特征、优点和细节。省略对公知的材料、制造工具、加工技术等的描述,以免不必要地让细节模糊本发明。然而,应当理解,详细说明和具体示例虽然指示了本发明的方面,但是仅以举例说明的方式给出,并非以限制的方式给出。通过本公开,在基本发明构思的精神和/或范围内的各种替换、修改、添加和/或布置对于本领域技术人员而言将是显而易见的。

21.如在整个说明书和权利要求书中所使用的,近似语言可用于修饰在不导致与之相关的基本功能发生变化的情况下可允许变化的任何定量表示。因此,由诸如“近似”、“约”之类的一个或多个术语修饰的值不限于所指定的精确值。在某些情况下,近似语言可以对应

于用于测量该值的仪器的精度。此外,由诸如“基本上”之类的一个或多个术语修饰方向,意味着该方向在半导体工业的正常容差范围内应用。例如,“基本上平行”意味着在半导体工业的正常容差范围内大致沿相同方向延伸,而“基本上垂直”意味着九十度加上或减去半导体工业的正常容差的角度。

22.本文使用的术语仅出于描述具体示例的目的,并非旨在限制本发明。如本文所使用的,单数形式“一”、“一个”和“该”旨在也包括复数形式,除非上下文另外明确指出。还将理解,术语“comprise(包括)”(以及comprise的任何形式,例如“comprises”和“comprising”),“have(具有)”(以及have的任何形式,例如“has”和“having”),“include(包含)”(以及include的任何形式,例如“includes”和“including”),以及“contain(含有)”(以及contain的任何形式,例如“contains”和“containing”)是开放式链接动词。因此,“包括”、“具有”、“包含”或“含有”一个或多个步骤或元件的方法或装置具有这些一个或多个步骤或元件,但不限于仅具有这些一个或多个步骤或元件。同样地,“包括”、“具有”、“包含”或“含有”一个或多个特征的方法步骤或装置元件具有这些一个或多个特征,但不限于仅具有这些一个或多个特征。此外,以某种方式配置的装置或结构至少以这种方式配置,但是也可以以未列出的方式配置。

23.如本文所使用的,当用于指示两个物理元件时,术语“连接”表示两个物理元件之间的直接连接。然而,术语“耦接”可以表示直接连接或通过一个或多个中间元件的连接。

24.如本文所使用的,术语“可以”和“可以是”表示:在一组情况内发生的可能性;拥有指定的性质、特性或功能;和/或通过表达与限定动词相关联的能力、功能或可能性中的一项或多项来限定另一动词。因此,“可以”和“可以是”的使用表示被修饰的术语显然适合、允许或适于指定的能力、功能或用途,同时考虑到在某些情况下被修饰的术语有时不适合、允许或适于。例如,在某些情况下,可预期一事件或能力,而在其他情况下,则不能出现该事件或能力——这种区别由术语“可以”和“可以是”捕获。

25.图1示出了根据各种非限制性实施例的双向双极型esd器件的简化截面图。

26.图2示出了根据各种非限制性实施例的图1的双向双极型esd器件的简化示意图。

27.参考图1,根据本公开的各种非限制性实施例的esd器件可以包括具有两个发射极/集电极部分的对称双向双极型晶体管结构。发射极/集电极部分可以各自包括位于具有第二导电类型的中压阱区108、110(例如,mv nwell或mv pwell)内的第二导电类型的重掺杂端子区130、134(例如,n+区或p+区)。重掺杂端子区130、134连接到导电端子160、162(例如,形成在衬底上方的金属层中)。在发射极/集电极部分之间的中央,具有第二导电类型的重掺杂浮置区(即,不连接到任何端子)132(例如,n+区或p+区),其在具有第一导电类型的低压阱区120(例如,lv pwell或lv nwell)和具有第一导电类型的漂移区122(例如p-drift或n-drift)内并被它们包围。重掺杂浮置中心岛区132通过形成在衬底表面上的阻挡或绝缘层159而与两个重掺杂端子区隔离。绝缘层159可以形成在导电端子之间并且至少在具有漂移区120、122的低压阱区的表面上,漂移区120、122在衬底内将包括发射极/集电极端子的两个发射极/集电极部分与浮置中心岛区分隔开。绝缘层159可以是硅化物阻挡层150(例如,sab)或多晶硅阻挡层151a、151b,但不是浅沟槽隔离(sti)结构。双向双极型晶体管结构布置在具有第一导电类型的高压阱106(例如,hv pwell或hv nwell)内,该高压阱106与具有第一导电类型的体衬底区102(例如,p-sub或n-sub)隔离。衬底隔离区103将具有第一导

电类型的高压阱106(例如,hv pwell或hv nwell)与具有第一导电类型的体衬底区102(例如,p-sub或n-sub)分隔开。衬底隔离区103可以是具有第二导电类型的外延掺杂区(例如,n-epi或p-epi)或掩埋氧化物区。

28.具有第一导电类型的低压阱和漂移区120、122(例如,p型区或n型区)也可以补偿位于顶部(例如,朝着与体衬底层102相对的衬底101的表面)的具有第二导电类型的中压阱108(例如,mv nwell或mv pwell)的一部分,以使中压阱的顶部成为具有第一导电类型的区域。也就是说,具有漂移区120、122(例如,p型区或n型区)的低压阱补偿位于顶部的中压阱(例如,mv nwell)的一部分,作为双极型晶体管结构(npn或pnp)的基极。特别地,在该区域中,具有漂移区120、122的低压阱(例如,lv pwell和p-drift或lv nwell和n-drift)的总掺杂浓度高于中压阱区108、110(例如,mv nwell或mv pwell)的掺杂浓度,导致中压阱区108、110的靠近端子160、162的一部分中的净掺杂浓度变成第一导电类型(例如,p型或n型)。

29.参考图1,在一些非限制性实施例中,在第一导电类型(102、106、120、122)和第二导电类型(103、108、110、130、132、134)的多个掺杂区中,第一导电类型为p型,第二导电类型为n型。或者,在其他非限制性实施例中,在第一导电类型(102、106、120、122)和第二导电类型(103、108、110、130、132、134)的多个掺杂区中,第一导电类型为n型,第二导电类型为p型。

30.esd保护器件100可以包括衬底101。在各种非限制性实施例中,衬底101可以包括任何含硅衬底,包括但不限于硅(si)、单晶硅、多晶si、非晶si、蓝宝石上硅(sos)、绝缘体上硅(soi)或替代绝缘体上硅(sri)或硅锗衬底等。衬底102还可以包括各种隔离、掺杂和/或器件特征。衬底102可以包括:其他合适的单质半导体,例如晶体中的锗(ge);化合物半导体,例如碳化硅(sic)、砷化镓(gaas)、磷化镓(gap)、磷化铟(inp)、砷化铟(inas)和/或锑化铟(insb)或其组合;合金半导体,包括gaasp、alinas、galnas、gainp、gainasp或其组合。

31.在各种非限制性实施例中,衬底101可以具有布置在衬底101内的体或衬底区102。衬底区102可以具有第一导电类型。例如,衬底区102可以具有为p型的第一导电类型。在这种情况下,衬底区102可以包含p型掺杂剂。衬底区102的掺杂浓度范围可以在约1e15cm-3

到5e15cm-3

之间。因此,衬底区102可以包括p型衬底区(例如,p-sub)。然而,在替代的非限制性实施例中,衬底101可以具有为n型的第一导电类型的衬底区102。因此,衬底区102可以包括n型衬底区(例如,n-sub)。在这种情况下,衬底区102可以包含具有与p型掺杂剂相似的掺杂浓度的n型掺杂剂。

32.esd保护器件100的衬底101还可以包括衬底隔离区103,衬底隔离区103布置在衬底101内并且至少部分地位于衬底区102上方。衬底隔离区103可以是外延区104。外延区104可以具有不同于衬底区102的第一导电类型的第二导电类型。外延区104可以具有比衬底区102高的掺杂浓度。例如,外延区104可具有约5e15cm-3

到1e16 cm-3

的掺杂浓度范围。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,外延区104可以包括n型掺杂剂。因此,外延区104可以包括n-外延区。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,外延区104可以包括p型掺杂剂。因此,外延区104可以包括p-外延区(例如,p-epi)。或者,衬底隔离区103可以包括深阱区而不是外延区。例如,在一些实施例中,可以使用深nwell(或深pwell)来代替n-外延区(或p-外延区)。

33.esd保护器件100的衬底101还可以包括布置在衬底101内并且至少部分地位于衬底隔离区103(例如,外延区104)和衬底区102两者上方的第一导电区106。第一导电区106可以具有与衬底区102相似的第一导电类型。第一导电区106可以具有比衬底区102和衬底隔离区103的掺杂浓度高的掺杂浓度。第一导电区106可以是高压阱区。例如,第一导电区106可以具有约1e16cm-3

到5e16cm-3

的掺杂浓度。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第一导电区106可以包括p型掺杂剂。因此,第一导电区106可以包括高压p型阱(例如,hv pwell)。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第一导电区106可以包括n型掺杂剂。因此,第一导电区106可以包括高压n型阱(例如,hv n-well)。

34.esd保护器件100的衬底101还可以包括第一端子部和第二端子部,第一端子部包括第二导电区108,第二端子部包括第三导电区110,第一和第二端子部布置在衬底101内并且至少部分地位于第一导电区106上方。第二和第三导电区108、110可以布置成彼此间隔开。第二导电区108和第三导电区110的至少一部分可以各自布置在衬底101的顶表面的紧接下方。衬底101的顶表面与衬底区102相反。第二导电区108和第三导电区110可以各自是中压阱。第二和第三导电区108、110可以具有与外延区104或衬底隔离区103的深阱区相同的第二导电类型。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第二导电区108和第三导电区110可以包括n型掺杂剂。因此,第二和第三导电区108、110可以各自包括中压n型阱区(例如,mv nwell)。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第二和第三导电区108、110可以包括p型掺杂剂。因此,第二和第三导电区108、110可以各自包括中压p型阱区(例如,mv pwell)。第二和第三导电区(中压阱区)可以具有比第一导电区106高的掺杂浓度。例如,第二和第三导电区可以具有约1e17cm-3

到5e17cm-3

的掺杂浓度范围。

35.第一和第二端子部还可以各自包括相应的端子区。第一端子区130可以至少部分地布置在第二导电区108内。第一端子区130可以被配置为连接到第一外部电压。第二端子区134可以至少部分地布置在第三导电区110内。第二端子区134可以被配置为连接到第二外部电压。

36.第一和第二端子区130、134可以具有与第二和第三导电区108、110的导电类型相同的第二导电类型。第一端子区130和第二端子区134可以各自包括重掺杂区。也就是说,第一和第二端子区130、134的掺杂浓度高于第二和第三导电区108、110的掺杂浓度。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第一和第二端子区130、134可以包括n型掺杂剂。因此,第一和第二端子区130、134可以各自为n+区。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第一和第二端子区130、134可以包括p型掺杂剂。因此,第一和第二端子区130、134可以各自为p+区。

37.参考图1所示的示例性的非限制性实施例,第一端子区130和第二端子区134可以布置在衬底101的顶表面的紧接下方。第一端子区130可以连接到可以被施加第一外部电压的第一外部端子160,第二端子区134可以连接到可以被施加第二外部电压的第二外部端子162。此外,第一和第二端子区130、134以及第二和第三导电区108、110可以通过第一导电区

106和衬底隔离区103(例如,外延区104)与衬底区102隔离。

38.esd保护器件100的衬底101还可以包括布置在衬底101内并且至少部分地位于第一导电区106上方的第四导电区120。第四导电区120的至少一部分可以布置在衬底101的顶表面的紧接下方。第四导电区120的至少一部分可以进一步邻接(即,直接接触)第一导电区106的一部分。第四导电区120可以进一步居中地(例如,等距地)布置在第一和第二端子部的第二导电区108和第三导电区110之间。第四导电区120也可以邻接(即,直接接触)第二和第三导电区108、110。第四导电区120的第一侧壁111可以邻接第二导电区108,并且第四导电区120的第二侧壁113(与第一侧壁相反)可以邻接第三导电区110。第四导电区120通过第二和第三导电区的至少一部分与第一和第二端子区130、134分隔开。此外,在一些实施例中,第四导电区120的一部分可以进一步与第二导电区108的一部分重叠,并且第四导电区120的另一部分可以进一步与第三导电区110的一部分重叠。重叠可以提供esd保护器件的更佳性能。

39.第四导电区120可以是具有第一导电类型的低压阱区。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第四导电区120可以包括p型掺杂剂。因此,第四导电区120可以包括低压p型阱(例如,lv pwell)。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第四导电区120可以包括n型掺杂剂。因此,第四导电区120可以包括低压n型阱(例如,lv nwell)。

40.参考图1所示的示例性的非限制性实施例,第四导电区可以布置在衬底101的顶表面的紧接下方。此外,第四导电区120可以通过第一导电区106和衬底隔离区103(例如,外延区104)与衬底区102分隔开。

41.第四导电区120可以进一步包括浮置(或未连接的)中心岛区132。浮置区132可以是布置在第四导电区120内的重掺杂区。浮置区132可以布置在第四导电区120的中央,使得浮置区132与第四导电区120的第一侧壁111和第二侧壁113等距。浮置区132可以布置成与第四导电区120的第一和第二侧壁111和113相距一距离l。距离l调整双向双极型esd保护器件以用于不同的电压应用。击穿电压和保持电压(holding voltage)可以基于距离l而改变。例如,在浮置区和侧壁之间具有较长距离l的双向npn(或pnp)器件的击穿电压和保持电压高于具有较短距离l的双向npn(或pnp)器件。在浮置区和侧壁之间具有较短距离l的双向npn(或pnp)器件的击穿低压和保持电压低于具有较长距离l的双向npn(或pnp)器件。浮置区132具有与第一和第二端子区130、134相同的第二导电类型。然而,浮置区132不被配置为连接到外部电压。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,浮置区132可以包括n型掺杂剂。因此,浮置区132可以包括n+区。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,浮置区132可以包括p型掺杂剂。因此,浮置区132可以包括p+区。

42.参考图1所示的示例性的非限制性实施例,浮置区132可以居中地布置在第四导电区120内衬底101的顶表面的紧接下方。此外,浮置区132可以通过第一导电区106和衬底隔离区103(例如,外延区104)与衬底区102隔离。

43.第四导电区120的深度可以小于或基本等于第二导电区108和第三导电区110的深度。参考图1所示的示例性的非限制性实施例,第四导电区120的深度可以小于第二导电区

108和第三导电区110的深度。然而,在替代的非限制性实施例中,第二导电区108、第三导电区110和第四导电区120的深度可以基本相同。

44.第二导电区108和第三导电区110可以具有大致相等的掺杂浓度。此外,第二和第三导电区108、110的掺杂浓度可以高于第一导电区106的掺杂浓度。第一端子区130和第二端子区134可以分别具有比第二和第三导电区108、110高的掺杂浓度。例如,第二导电区108可以具有约1e17cm-3

到5e17cm-3

的掺杂浓度范围;第三导电区110也可以具有约1e17cm-3

到5e17cm-3

的掺杂浓度范围;第一端子区130可以具有约5e19 cm-3

到5e20cm-3

的掺杂浓度范围,并且第二端子区134可以具有约5e19 cm-3

到5e20cm-3

的掺杂浓度范围。第二和第三导电区108、110以及第一和第二端子区130、134可以具有与外延区104相同的导电类型。也就是说,它们可以具有第二导电类型。在第一导电类型可以为p型并且第二导电类型可以为n型的示例性的非限制性实施例中,第二和第三导电区108、110可以为n型阱并且第一和第二端子区130、134可以为n+区。

45.第四导电区120可以具有约5e17cm-3

到1e18cm-3

的掺杂浓度范围。此外,第四导电区120的掺杂浓度可以高于外延区104的掺杂浓度。第四导电区120可以具有比第一导电区106高的掺杂浓度。第四导电区120可以具有比第二和第三导电区108、110高的掺杂浓度。提供具有比第二和第三导电区108、110高的掺杂浓度的第四导电区120可以帮助实现足够高的保持电压以提供抗闩锁能力(latch-up immunity)。

46.重掺杂浮置区132可以具有与重掺杂第一端子区130和第二端子区134相同的掺杂浓度。

47.在多个掺杂区中,衬底区102具有最低掺杂浓度。当衬底隔离区104是外延区103或深阱区时,它具有比衬底区102高的掺杂浓度。第一导电区106具有比衬底隔离区104和/或衬底区102高的掺杂浓度。第二和第三导电区108、110具有相同的掺杂浓度并且高于第一导电区106的掺杂浓度。第四导电区120具有比第二和第三导电区108、110高的掺杂浓度。第一端子区130、浮置区132和第二端子区134具有相同的掺杂浓度,并且相对于其他区域也是最高的掺杂浓度。

48.在一些示例性的非限制性实施例中,第四导电区120还可以包括沿着与第二和第三导电区108、110的边界(例如,沿着第四导电区120的侧壁111和113)的漂移区122(例如,用于lv pwell的p-drift或用于lv nwell的n-drift)。漂移区122可以具有约5e16cm-3

到1e17cm-3

的掺杂浓度范围。漂移区可以帮助增大esd保护器件100的击穿电压。

49.esd保护器件100还可以包括布置在衬底101的顶表面上方的阻挡或绝缘层159。如图1所示,绝缘层159可以是布置成在第二导电区108和第三导电区110之间延伸的硅化物阻挡层150,与这些导电区108、110和第四导电区120的至少一部分重叠。在各种非限制性实施例中,硅化物阻挡层150可以防止第一端子区130、第二端子区134和浮置区132上的硅化物相互作用或处理(或换言之,阻挡在esd保护器件100的制造期间沉积的硅化物与第一端子区130、第二端子区134和浮置区132相互作用)。绝缘层159用于使浮置区132与端子区130、134电绝缘。硅化物阻挡层150可以由本领域技术人员已知的任何硅化物阻挡材料形成,例如但不限于氮化物。需要绝缘层159是因为硅化物材料可能在衬底101的表面的任何暴露或未覆盖区域中生成。在电学上,硅化物材料的作用类似于金属,并且硅化物材料会使浮置区132和端子区130、134短接在一起。硅化物阻挡材料(例如,氮化物)防止在覆盖区域中硅化

物生成,从而防止短路。

50.esd保护器件100还可以包括第一隔离元件140和第二隔离元件142。第一隔离元件140可以被配置为隔离第二导电区108和第一端子区130。第二隔离元件142可以被配置为隔离第三导电区110和第二端子区134。第一隔离元件140布置在衬底101的顶表面的紧接下方,位于第一端子区130和第二导电区108的背离浮置端子区132和第四导电区120的一侧。第二隔离元件142布置在衬底101的顶表面的紧接下方,位于第二端子区134和第三导电区110的背离浮置端子区132和第四导电区120的一侧。也就是说,第一和第二隔离元件140、142布置在esd保护器件100的端部处。例如,第一和第二隔离元件140、142可以是浅沟槽隔离(sti)块。

51.当esd保护器件100在使用中时,esd保护器件100还可以被配置为连接到设备(图1中未示出),例如但不限于消费电子产品,即,要被esd保护器件100保护的设备。在使用中,要被保护的设备连接到esd保护器件100的第一和第二端子160、162。这些端子160、162之间的电压可以称为esd电压。取决于esd电压,第一和第二端子160、162可以是发射极或集电极。也就是说,第一和第二端子160、162中的一者可以是发射极,而第一和第二端子160、162中的另一者可以是集电极,具体取决于esd电压的电压差的方向。当esd电压低于预定水平时,可忽略不计的电流流过esd保护器件100。然而,当esd电压超过预定水平时,esd保护器件100接通以将电流导离设备,从而保护设备免于损坏。

52.特别地,为了保护设备避免因为端子160、162之间的过高esd电压而损坏,esd保护器件100可以被配置为使得当第一外部电压和第二外部电压之间的差超过预定阈值时,至少一个放电电流可以通过esd保护器件100。

53.参考图1和图2,设备可以被配置为例如经由端子160、162连接到第一端子区130和第二端子区134。当第一外部电压高于第二外部电压时,第四导电区220和第二导电区108之间的第一侧壁111处的p-n(或n-p)结可以被反向偏置。因此,当第一外部电压和第二外部电压之间的差超过第一预定阈值时,第一侧壁111处的p-n结可能击穿,并且第一npn(或pnp)晶体管可以接通,该晶体管可以包括第二导电区108作为集电极,第四导电区120作为基极,第三导电区110作为发射极。然后,第一放电电流可以从第一npn晶体管的发射极通过基极流到集电极。换言之,第一放电电流可以通过第四导电区120在第二导电区108和第三导电区110之间流过。然后,第一放电电流可以接通第二npn(或pnp)晶体管,该晶体管可以包括第三导电区110作为发射极,第一导电区106作为基极,外延区104作为集电极。然后,第二放电电流可以从该第二npn(或pnp)晶体管的发射极通过基极流到集电极。换言之,第一放电电流可使第二放电电流通过第一导电区106在外延区104和第三导电区110之间流过。

54.当第二外部电压高于第一外部电压时,第四导电区120和第三导电区110之间的第二侧壁113处的p-n结也可以被反向偏置。因此,当第一外部电压和第二外部电压之间的差超过第一预定阈值时,第二侧壁113处的p-n(或n-p)结可能击穿并且第一npn(或pnp)晶体管可以接通,该晶体管可以包括第三导电区110作为集电极,第四导电区120作为基极,第二导电区108作为发射极。然后,第一放电电流可以从第一npn(或pnp)晶体管的发射极通过基极流到集电极。换言之,第一放电电流可以通过第四导电区120在第二导电区108和第三导电区110之间流过。然后,第一放电电流可以接通第二npn(或pnp)晶体管,该晶体管可以包括第二导电区108作为发射极,第一导电区106作为基极,外延区104作为集电极。然后,第二

放电电流可以从该第二npn晶体管的发射极通过基极流到集电极。换言之,第一放电电流可使第二放电电流通过第一导电区106在外延区104和第二导电区108之间流过。

55.因此,如图2所示,在各种非限制性实施例中,esd保护器件100的等效电路可以包括晶体管,该晶体管具有第二导电区108作为发射极(当第二外部电压高于第一外部电压时),以及具有第三导电区110作为发射极(当第一外部电压高于第二外部电压时)。无论经过esd保护器件的电流方向如何,第一导电区106都可以作为基极。将理解,如果图2所示的实施例中的导电类型反转,则上述电流的方向可以反转。

56.提供衬底隔离区103(例如,外延区104)和第一导电区106并将这些区域103、106设置为浮置可以允许衬底隔离区103充当第二npn(或pnp)晶体管的集电极,并且允许第一导电区106充当第一和第二npn(或pnp)晶体管的基极,而无论第一和第二端子部108/130、110/134之间的电压极性如何(换言之,无论第一和第二外部电压中的哪一者更高)。因此,esd保护器件100能够支持双向高电压偏置并提供双向esd电流传导。在第一外部电压可以高于第二外部电压的各种非限制性实施例中,第一外部电压可以是一般电源电压(例如,vdd)并且第二外部电压可以是接地(例如,gnd),或者,第一外部电压可以为正,第二外部电压可以为负。在第一外部电压可以低于第二外部电压的替代非限制性实施例中,第二外部电压可以是一般电源电压(例如,vdd)并且第一外部电压可以是接地。或者,第一外部电压可以为负,第二外部电压可以为正。

57.此外,在各种非限制性实施例中,如上所述通过esd保护器件100的第一放电电流和第二放电电流二者都可以帮助将电流导离设备。这可以允许esd保护器件100具有改进的esd电流传导能力。

58.在各种非限制性实施例中,esd保护器件100可以为紧凑型,并且可以具有良好的钳位能力(即,使接通电阻的变化最小化)和高保持电压以提供抗闩锁能力。图3示出了本发明的具有不同基部长度的bi-npn结构的tcad模拟的类tlp i-v曲线。图3示出了当esd保护器件100的基部长度设定为0.8um(301)及1.2um(311)且第一外部电压大于第二外部电压时,esd保护器件100的性能。然而,由于esd保护器件100的结构的对称性,在第二外部电压大于第一外部电压时获得的结果与图3所示的结果基本相同。特别地,图表300是传输线脉冲(tlp)电流与传输线脉冲(tlp)电压的关系的绘图。图表300示出了通过使用技术计算机辅助设计(tcad)模拟器件100获得的结果。参考图表300,结果表明基部长度为0.8um的器件100可以具有约12.0v的保持电压(vh)(在303处),约13.0v的触发电压(vt1)(在305处)、约23.5v的第二击穿电压(vt2)(在307处)和约3.5ma/um的第二击穿电流(it2)(在307处)。此外,结果表明基部长度为1.2um的器件100可以具有约14.0v的保持电压(vh)(在313处)、约16.0v的触发电压(vt1)(在315处)、约27.5v的第二击穿电压(vt2)(在317处)和约3.4ma/um的第二击穿电流(it2)(在317处)。如图3所示,绘图301和311中的每一者都示出了高保持电压和小折回(snapback)以提供抗闩锁的esd保护。例如,保持电压必须大于电源电压(例如,vdd)以避免闩锁,并且保持电压应为高的以使触发电压和保持电压之间的差最小化(即,小折回)。这些绘图没有表现出单向npn器件中常见的弯曲(bending)行为。由于电流流动更均匀,不发生弯曲行为。弯曲行为是不希望的,因为那将意味着接通电阻的大幅增加。

59.图4a-4b示出了通过使用tcad模拟esd保护器件100获得的esd保护器件100的一部分的电流密度图。图4a示出了约0.2ma/um的放电电流的电流密度图。图4b示出了约2ma/um

的放电电流的电流密度图。在模拟中,第一电压(左端子)高于第二电压(右端子)。如图4a所示,在较低的放电电流下,与通过第四导电区120到达第三导电区110相比,较高的电流密度从第二导电区108流动通过第一导电区106。如图4b所示,在较高的放电电流下,与通过第一导电区208相比,较高的电流密度从第二导电区108通过第四导电区120流到第三导电区110。换言之,电流密度图指示对于高放电电流,第一放电电流可以高于第二放电电流。这表明esd器件100最初在底部处被触发。但是随着放电电流的增加,浮置区132辅助收集大量的较高电流电平的电流。

60.在各种非限制性实施例中,用于衬底区102、外延区104、第一至第四导电区106、108、110、120;端子区130、134;以及浮置区132的注入材料可以是相同的注入材料,例如非限制性实施例中为外延硅材料。p型材料可以是或包括但不限于外延硅锗,和/或n型材料可以是或包括但不限于包含n型掺杂剂的掺杂硅材料。p型掺杂剂例如可以包括但不限于硼(b)、铝(al)、铟(in)或其组合,而n型掺杂剂可以包括碳(c)、磷(p)、砷(as)、锑(sb)或其组合。本领域技术人员已知的其他类型的注入材料和掺杂剂也可用于形成区域102、104、106、108、110、120;端子区130、134;以及浮置区132。

61.图5示出了根据替代的非限制性实施例的esd保护器件500的简化截面图。esd保护器件500与esd保护器件100相似,因此,共同的特征用相同的参考标号标记并且不需要讨论。如图5所示,第四导电区120’与esd保护器件100的第四导电区120相似,但esd保护器件500的第四导电区120’不与第二和第三导电区108、110重叠。此外,esd保护器件500的衬底部分可以通过竖直隔离元件(例如,沟槽)170、172进一步与衬底中的其他器件隔离。竖直隔离元件170、172可以是深沟槽隔离(例如,dti)结构,深沟槽隔离结构从衬底101的顶表面延伸到衬底101的衬底区102(即,体衬底)内。例如,竖直隔离元件170、172可以布置在esd保护器件500的分别与第一和第二隔离元件140、142相邻的端部处。

62.图6示出了根据替代的非限制性实施例的esd保护器件600的简化截面图。esd保护器件600是具有多界结(poly bounded junction)的双向双极型esd保护器件。esd保护器件600与esd保护器件100相似,因此,共同的特征用相同的参考标号标记并且不需要讨论。如图6所示,esd保护器件600的阻挡或绝缘层159可以包括两个多界结(例如,多晶块(polyblock))151a、151b,而不是硅化物阻挡层150。多晶块151a、151b可以包括:栅极氧化物区156a、156b;多晶硅158a、158b和用于多晶硅的间隔物(spacer)154a、154b。第一多晶块151a可以使浮置区132与第一端子区130绝缘。第二多晶块151b可以使浮置区132与第二端子区134绝缘。

63.图7示出了根据替代的非限制性实施例的esd保护器件700的简化截面图。esd保护器件700是使用绝缘体上硅(soi)结构形成的双向双极型esd保护器件。esd保护器件700与esd保护器件100相似,因此,共同的特征用相同的参考标号标记并且不需要讨论。如图7所示,衬底隔离区103可以包括掩埋氧化物区105而不是外延区103。掩埋氧化物区105可以设置在esd保护器件100的衬底区102和第一导电区106(而不是外延区或深阱区)之间。掩埋氧化物区105可以促进更薄的衬底。氧化物材料是一种几乎不电气传导电流的绝缘体材料。氧化物材料可用于将双向双极型器件与衬底完全隔离。掩埋氧化物层105可以提供更好的隔离性能。

64.图8示出了根据替代的非限制性实施例的esd保护器件800的简化截面图。图8示出

了布置成堆叠的esd保护器件以用于更高电压应用。esd保护器件800可以包括堆叠两个或更多个esd保护器件100以促进更大的电流传导。例如,如图8所示,esd保护器件800可以包括在衬底101中彼此相邻布置的第一esd保护器件100a和第二esd保护器件100b。第一和第二esd保护器件100a、100b可以各自是图1的esd保护器件。共同的特征用相同的参考标号标记并且不需要讨论。参考图8,第一和第二esd保护器件100a、100b的衬底部分可以通过竖直隔离元件(例如,沟槽)170、172、174彼此隔离。竖直隔离元件170、172、174可以是深沟槽隔离(例如,dti)结构,这些深沟槽隔离结构从衬底101的顶表面延伸到衬底101的衬底区102(即,体衬底)内。竖直隔离元件可以布置在两个或更多个相邻esd保护器件中的每一者之间(例如,在第一和第二esd保护器件100a、100b之间)以及布置在被配置为端子端部的esd保护器件的端部处(例如,第一和第二esd保护器件100a、100b的端部处)。

65.参考图8,第一esd保护器件100a的第一端子区130a可以被配置为通过第一外部端子160’连接到第一外部电压,并且第二esd保护器件100b的第二端子区134b可以被配置为通过第二外部端子162’连接到第二外部电压。第一esd保护器件100a的第二端子区134a可以通过端子连接器165连接到第二esd保护器件100b的第一端子区130b。端子连接器165可以形成在与外部端子160’和162’相同的层(例如,衬底上方的金属层)中。

66.为了更高电压的esd保护,额外的esd保护器件100可以在衬底中彼此相邻地布置并且它们的端子串联连接。例如,第一esd保护器件的第一端子区可以被配置为通过第一外部端子连接到第一外部电压,并且最后一个esd保护器件的第二端子区可以被配置为通过第二外部端子连接到第二外部电压。每个中间esd保护器件可以被菊花链式连接(daisy chain)。例如,中间esd保护器件的第一端子区可以连接到前一esd保护器件的第二端子区,并且中间esd保护器件的第二端子区可以连接到后一esd保护器件的第一端子区。

67.替代地,esd保护器件100a、100b也可以是esd保护器件500、600或700之一。

68.图9a示出了根据替代的非限制性实施例的esd保护器件900的简化截面图。图9a示出了被配置用于多端子保护的esd保护器件。特别地,图9a示出了用于三端子结构的esd保护器件900,其中每个端子(160、162、164)与其他两个端子隔离。例如,这三个端子可以是电源端子(例如,vdd)、输入/输出端子(例如,io)和接地端子(例如,gnd)。esd保护器件900可以同时为一个结构内的vdd到i/o路径和i/o到地路径提供双极性esd电流传导。esd保护器件900的一些部分与esd保护器件100类似,因此,共同的特征用相同的参考标号标记并且不需要讨论。图9b示出了根据本公开的各个方面的esd保护器件900的简化示意图。如图9b所示,esd保护器件900可以连接到另一半导体器件901(例如,消费电子设备)和/或与另一半导体器件901(例如,消费电子设备)集成以向半导体器件901提供esd保护。

69.如图9a所示,esd保护器件900还可以包括第三端子部。第三端子部可以包括第五导电区112、第三端子区138和第三外部端子164。第五导电区112可以布置在衬底101内并且至少部分地位于第一导电区106上方。第五导电区112与第二和第三导电区108、110类似。也就是说,掺杂浓度与第二和第三导电区108、110相似并且导电类型与第二和第三导电区108、110相同。此外,第二、第三和第五导电区108、110、112可以布置成在第一导电区106内彼此间隔开。第五导电区112的至少一部分也可以布置在衬底101的顶表面的紧接下方。第五导电区112也可以是中压阱。第五导电区112也可以具有与第二和第三导电区108、110相同的第二导电类型。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二

导电类型可以为n型。在这种情况下,第五导电区112也可以包括n型掺杂剂。因此,第五导电区112也可以包括中压n型阱区(例如,mv nwell)。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第五导电区111可以包括p型掺杂剂。因此,第五导电区112可以包括中压p型阱区(例如,mv pwell)。

70.类似地,第五导电区112也可以进一步包括相应的端子区。第三端子区138可以至少部分地布置在第五导电区112内。第三端子区138可以被配置为连接到第三外部电压。例如,第一端子区130可以被配置为连接到电源线(例如,vdd),第二端子区134可以被配置为连接到输入/输出线,并且第三端子区138可以被配置为连接到地。

71.第三端子区138也可以具有与第五导电区112的导电类型相同的第二导电类型。第三端子区138可以类似于第一和第二端子区130、134。也就是说,掺杂浓度相似且导电类型相同。第三端子区138还可以包括重掺杂区。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第三端子区138也可以包括n型掺杂剂。因此,第三端子区138也可以像第一和第二端子区一样为n+区。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第三端子区138可以包括p型掺杂剂。因此,第三端子区138也可以像第一和第二端子区一样为p+区。

72.参考图9a所示的示例性的非限制性实施例,第三端子区138也可以布置在衬底101的顶表面的紧接下方。第三端子区138可以连接到可以被施加第三外部电压的第三外部端子164。此外,第三端子区138和第五导电区112可以通过第一导电区106和衬底隔离区103(例如,外延区104)而与衬底区102隔离。

73.esd保护器件900的衬底101可以进一步包括布置在衬底101内并且至少部分地位于第一导电区106上方的第六导电区124。第六导电区124的至少一部分可以邻接(即,直接接触)第一导电区106的一部分。第六导电区124可以进一步居中地(例如,等距地)布置在第三导电区110和第五导电区112之间。第六导电区124可以邻接(即,直接接触)第三和第五导电区110、112。第六导电区124的第一侧壁115可以邻接第三导电区110,并且第六导电区124的第二侧壁117(与第一侧壁相反)可以邻接第五导电区112。第六导电区124通过第三和第五导电区的至少一部分与第二和第三端子区134、138分隔开。此外,在一些实施例中,第六导电区124的一部分可以进一步与第三导电区110的一部分重叠,并且第六导电区124的另一部分可以进一步与第五导电区112的一部分重叠。重叠可以提供esd保护器件的更佳性能。

74.第六导电区124类似于第四导电区120。也就是说,掺杂浓度相似且导电类型相同。第六导电区124也可以是具有第一导电类型的低压阱区。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第六导电区124可以包括p型掺杂剂。因此,第六导电区124可以包括低压p型阱(例如,lv pwell)。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第六导电区124可以包括n型掺杂剂。因此,第六导电区124可以包括低压n型阱(例如,lv nwell)。

75.参考图9a所示的示例性的非限制性实施例,第六导电区124可以布置在衬底101的顶表面的紧接下方。此外,第六导电区124可以通过第一导电区106和衬底隔离区103(例如,

外延104区)而与衬底区102分隔开。

76.第六导电区124可以进一步包括第二重掺杂浮置(或未连接)区136。第二浮置区136可以布置在第六导电区124内。第二浮置区136可以布置在第六导电区124的中央,使得第二浮置区136与第六导电区124的第一侧壁115和第二侧壁117等距。第二浮置区136与浮置区132类似。在一些示例性的非限制性实施例中,第一导电类型可以为p型并且第二导电类型可以为n型。在这种情况下,第一和第二浮置区132、136可以包括n型掺杂剂。因此,第一和第二浮置区132、136也可以包括n+区。然而,在替代的非限制性实施例中,第一导电类型可以为n型并且第二导电类型可以为p型。在这种情况下,第一和第二浮置区132、136可以包括p型掺杂剂。因此,第一和第二浮置区132、136可以包括p+区。

77.参考图9a所示的示例性的非限制性实施例,第二浮置区136可以布置在衬底101的顶表面的紧接下方。此外,第二浮置区136可以通过第一导电区106和衬底隔离区103(例如,外延区104)而与衬底区102隔离。

78.在一些示例性的非限制性实施例中,第六导电区124还可以包括沿着与第三和第五导电区110、112的边界(例如,沿着第六导电区124的侧壁115和117)的漂移区126(例如,用于lv pwell的p-drift或用于lv nwell的n-drift)。漂移区有助于增大esd保护器件900的击穿电压。

79.esd保护器件900还可以包括布置在衬底101的顶表面上方的第二阻挡或绝缘层159’。如图9a所示,第二绝缘层159’可以是布置成在第三导电区110和第五导电区112之间延伸的第二硅化物阻挡层152,与这些导电区110、112和第六导电区124的至少一部分重叠。与绝缘层159一样,第二绝缘层159’防止第二端子区134、第三端子区138和第二浮置区136上的硅化物相互作用或处理(或换言之,阻挡在esd保护器件900的制造期间沉积的硅化物与第二端子区134、第三端子区138和第二浮置区136相互作用)。绝缘层159’用于将第二浮置区136与端子区134、138电绝缘。

80.esd保护器件900可以进一步包括第一隔离元件140’和第二隔离元件142’。第一隔离元件140’可以被配置为隔离第二导电区108和第一端子区130。第二隔离元件142’可以被配置为隔离第五导电区112和第三端子区138。第一隔离元件140’布置在衬底101的顶表面的紧接下方,位于第一端子区130和第二导电区108的背离浮置端子区132和第四导电区120的一侧。第二隔离元件142'布置在衬底101的顶表面的紧接下方,位于第三端子区138和第五导电区112的背离第二浮置端子区136和第六导电区124的一侧。也就是说,第一和第二隔离元件140’、142’布置在esd保护器件900的端部处。例如,第一和第二隔离元件140’、142’可以是浅沟槽隔离(sti)块。此外,esd保护器件900的衬底部分可以通过竖直隔离元件(例如,沟槽)170’、172’进一步与衬底中的其他器件隔离。

81.图10a和10b示出了根据各种非限制性实施例的用于形成esd保护器件的方法1000的流程图。如图10a所示,方法1000可以通过提供衬底101开始(在1002处)。方法1000可以包括在衬底101内形成(在1004处)第一导电类型的衬底区102。方法1000可以包括在衬底101内且至少部分地在衬底区102上方形成(在1006处)衬底隔离区103(例如,具有第二导电类型的外延区104或掩埋氧化物层105)。方法1000可以包括在衬底101内且至少部分地在外延区104上方形成(在1008处)具有第一导电类型的第一导电区106。方法1000可以包括在衬底101内且至少部分地在第一导电区106上方形成(在1010处)具有第二导电类型的第二和第

三导电区108、110。第二和第三导电区108、110彼此间隔开。方法1000可以包括在衬底101内且至少部分地在第一导电区106上方在第二和第三导电区108、110之间形成(在1012处)第四导电区120。在一些替代的非限制性实施例中,第四导电区120还可部分地形成在第二和第三导电区108、110的部分上方。

82.衬底区102、外延区104、掩埋氧化物区105、第一、第二、第三和第四导电区106、108、110、120可以使用本领域技术人员已知的任何方法形成。在非限制性示例中,这些区域102、104、106、108、110、120中的每一者可以通过使用掩模来暴露旨在用于相应区域102、104、106、108、110、120的衬底101的一部分,并用适当的掺杂剂(例如,p型或n型掺杂剂)掺杂暴露部分而形成。在非限制性示例中,掩埋氧化物区105可以通过使用掩模来暴露旨在用于相应区域102、104、106、108、110、120的衬底101的一部分并将氧注入暴露的部分而形成。

83.接下来,方法1000可以包括形成和配置(在1016处)端子区130、134和浮置区132。例如,在1016处,方法1000可以包括至少部分地在第二导电区108内形成第一端子区130,至少部分地在第三导电区110内形成第二端子区134,至少部分地在第四导电区120内形成浮置区132,并且配置第一端子区130和第二端子区134以分别连接到第一外部电压和第二外部电压。在各种非限制性实施例中,端子区130、134和浮置区120可以通过将掺杂剂注入到衬底101的相应部分中来形成。掺杂剂的注入可以通过本领域技术人员已知的任何方法来执行,例如但不限于离子注入。

84.方法1000还可以包括在衬底101上方形成(在1018处)阻挡或绝缘层159(例如,硅化物阻挡层150或多晶硅块151a、151b)以至少覆盖第四导电区120并且至少部分地覆盖第二导电区108和第三导电区110。硅化物阻挡层150可以进一步完全覆盖浮置区132和第四导电区120并且至少部分地覆盖第一端子区130、第二导电区108、第二端子区134和第三导电区110。可以使用本领域技术人员已知的任何方法形成硅化物阻挡层150和多晶硅块151a、151b。例如,在非限制性示例中,可以通过在衬底101的顶表面上方沉积硅化物阻挡材料并蚀刻该硅化物阻挡材料来形成硅化物阻挡层150。

85.方法1000然后可以包括形成(在1020处)隔离元件140、142(例如,浅沟槽隔离(sti)块)。在各种非限制性实施例中,隔离元件140、142可以通过本领域技术人员已知的任何方法形成。例如,可以在衬底101上方布置掩模以暴露衬底101的旨在用于隔离元件140、142的部分,然后可以蚀刻暴露的部分以形成沟槽,并且可以用隔离材料填充沟槽。

86.接着,方法1000可以包括在形成衬底区之前形成(在1003处)深隔离元件170、172、174(例如,深沟槽隔离(dti)块)。在各种非限制性实施例中,深隔离元件170、172可以通过本领域技术人员已知的任何方法形成。例如,可以在衬底101上方布置掩模以暴露衬底101的旨在用于深隔离元件170、172的部分,然后可以蚀刻暴露的部分以形成深沟槽,并且可以用隔离材料填充沟槽。

87.在不脱离本发明的精神或基本特性的情况下,本发明可以以其他特定形式体现。因此,前述实施例在所有方面都被认为是示例性的,而不是限制本文描述的发明。因此,本发明的范围由所附权利要求书而不是由前述说明书指示,并且落入权利要求的等同物的含义和范围内的所有改变旨在被包含在其中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1