一种亚纳米级铁电存储计算一体器件及其制备方法与流程

1.本发明属于半导体芯片技术领域,尤其涉及一种亚纳米级铁电存储计算一体器件及其制备方法。

背景技术:

2.随着人工智能时代的到来,数据的深度处理和存储要求更高的运算速度和更低的能耗,传统的冯诺依曼架构的计算和存储单元是分离的,面临着速度瓶颈与功耗浪费的问题,因此新型计算存储一体化技术成为研究的重要方向。

3.铁电存储计算一体具备读写速度快、抗疲劳性能突出、功耗低以及结构简单等优势具有重大的应用前景。目前的铁电存储计算一体器件主要包括fefet、mfmfet、feram、ftj等,其中,fefet高的写入电压和与si通道的非理想界面限制了它的循环稳定性能,而feram及ftj做存储计算一体应用时需额外接入晶体管,且由于器件与外接晶体管源漏电级直接接触,不能进行多值运算。相比之下,mfmfet在fe铁电层和晶体管栅氧层之间插入额外的电极层,不仅避免了si通道的非理想界面,缓解了逻辑与存储器之间的设计冲突,提高了循环稳定性能,而且能够进行多值运算。此外,通过调整铁电存储器mfm(afe)与晶体管fet(amos)之间的面积比(ar=afe/amos),可以有效增加与铁电耦合的电压,从而在低电压下高效写入。

4.随着摩尔定律不断延续,晶体管的尺寸不断缩小,fet的产线工艺已经达到几纳米级别。根据最新研究表明,ar=1:10时可以实现存储计算一体技术最佳的写入和读出性能,因此与晶体管相对应铁电存储器mfm的尺寸需要达到亚纳米级别,这在现有的fab工艺技术与设备中是很难达到的,存在与标准的cmos工艺兼容性和尺寸微缩难的问题,我们必须进行结构创新和选用新材料。

技术实现要素:

5.为解决上述技术问题,本发明的第一方面提出了一种亚纳米级铁电存储计算一体器件,所述铁电存储计算一体器件包括,铁电存储器和mosfet晶体管;

6.所述铁电存储器作为数据存储元件,所述mosfet晶体管执行数据计算功能;

7.采用低维材料制作所述铁电存储器的底电极2,所述铁电存储器从上到下依次包括:金属电极5、顶电极4、铁电层3和底电极2;各层均位于mosfet晶体管的栅极之上依预定构型层叠制作;

8.所述mosfet晶体管作为所述铁电存储计算一体器件的基体,所述铁电存储器的底电极2与所述mosfet晶体管的栅极直接连接;

9.所述铁电存储器的有效工作区域6的尺寸仅由底电极2的厚度方向相对于铁电层3的宽度来确定,以将所述铁电存储器有效工作区6的线宽尺寸限定在亚纳米级别。

10.如本发明第一方面的器件,所述铁电存储计算一体器件还包括一台阶状隔离层1,所述铁电存储器与mosfet晶体管的栅极之间被台阶状隔离层1隔离并绝缘,所述台阶状隔

离层1的位于所述栅极中间区域上部的所述台阶状隔离层1左侧部分高于所述台阶状隔离层1右侧部分一个预定尺寸。

11.如本发明第一方面的器件,位于所述底电极2和所述台阶状隔离层1之上的所述铁电层3呈凸字形状,所述铁电层3完全覆盖所述台阶状隔离层1和所述底电极2;

12.所述顶电极4和所述金属电极5仅设置在所述隔离层1右侧部分的台阶下层对应的所述铁电层3之上。

13.如本发明第一方面的器件,控制铁电存储器的面积与所述mosfet晶体管的面积比ar的取值范围为:1:5到1:20。

14.本发明的第二方面提出一种亚纳米级铁电存储计算一体器件的制备方法,所述制备方法包括以下步骤:

15.步骤1,以纳米级尺寸的金属氧化物场效应晶体管mosfet晶片为基板,在制作铁电存储器之前,对所述mosfet晶片执行清洗和烘干;

16.步骤2,在经步骤1处理的所述mosfet晶片上制备隔离层1,对所述隔离层1执行多次光刻图形化,形成位于mosfet栅极上面的台阶状隔离层1,所述台阶状隔离层1的台阶上层区域的高度高于台阶下层区域一个预定尺寸;所述台阶状隔离层1仅覆盖所述mosfet栅极的右侧部分区域;

17.步骤3,在台阶状隔离层1上制备所述铁电存储器的底电极2层;对所述底电极2层进行光刻图形化,使底电极2层覆盖所述mosfet栅极上没有被台阶状隔离层1覆盖的区域和所述台阶状隔离层1的台阶上层区域,而所述台阶下层区域不被所述底电极2层覆盖;

18.步骤4,在步骤3完成后,制备铁电层3,所述铁电层3制成后执行光刻图形化,仅保留位于mosfet栅极之上的铁电层3,将其余的铁电层3刻蚀去除;

19.步骤5,在铁电层3上依次沉积顶电极4层和金属电极5层,对所述顶电极4层和所述金属电极5层执行光刻图形化,仅保留位于所述台阶状隔离层1的台阶下层区域上的顶电极4层和金属电极5层,将顶电极4层和金属电极5层的多余部分刻蚀去除,以构成顶电极4和金属电极5;

20.步骤6,由所述mosfet晶片上由多个mosfet晶体管构成晶体管阵列,将所述晶体管阵列中各个mosfet晶体管的源级互联形成接地线,将所述晶体管阵列的各个mosfet晶体管的漏极互联形成位线,将各个铁电存储器的金属电极5互联形成字线,从而使所述晶体管阵列中的亚纳米级铁电存储计算一体器件同时具备存储和多值计算功能。

21.如本发明第二方面的制备方法,所述台阶状隔离层1采用低介电常数材料三氧化二铝或二氧化硅;所述台阶状隔离层1制备工艺采用以下方法之一:溅射法、原子力沉积法、化学气相沉积法或物理气相沉积法。

22.如本发明第二方面的制备方法,所述底电极2层采用的低维材料从以下材料中择一选用:二维薄膜材料、一维纤维材料或零维量子点材料;所述低维材料的尺度均在纳米级;

23.步骤3中采用所述低维材料湿法转移制备方法制备所述铁电存储器的底电极2层,所述湿法转移制备方法采用以下方法之一:转印、喷涂、旋涂或刮涂;

24.所述顶电极4材料为氮化钛;

25.所述金属电极5材料从以下材料中择一选用:钨、铝、镍或铂;

26.所述顶电极4和所述金属电极5的制备工艺采用以下方法之一:溅射、原子力沉积、化学气相沉积、物理气相沉积或热蒸镀。

27.如本发明第二方面的制备方法,所述二维薄膜材料从以下材料中择一选用:石墨烯或mos2;所述一维纤维材料采用银纳米线;所述零维量子点材料采用金量子点。

28.如本发明第二方面的制备方法,所述铁电层3薄膜材料包括以下材料之一或它们的混合物:hfo2、zro2、hfxzr

1-x

o2、锆钛酸铅;所述铁电层3的制备工艺采用以下方法之一:溅射、原子力沉积、化学气相沉积或物理气相沉积。

29.如本发明第二方面的制备方法,步骤6还包括在氮气气氛中快速退火使得铁电薄膜结晶。

30.采用本发明的方法有以下优点,

31.1铁电存储器底电极选用低维材料,在特定维度形成分子乃至原子尺寸的厚度,且厚度能调节的范围更宽,既能与标准的cmos工艺兼容,也能使铁电存储器mfm的尺寸达到亚纳米分子或原子尺寸级别。

32.2在隔离层上形成台阶状分布,使得铁电存储器纵向垂直分布,有效电场来自底电极层厚度,能够更好与现有晶体管纳米级别工艺技术相匹配ar=1:10,实现最佳写入和读出性能的同时,解决尺寸微缩难的问题。

33.3铁电存储计算一体阵列具备读写速度快、抗疲劳性能突出、功耗低以及结构简单等优势,能够有效突破传统冯诺依曼架构计算和存储单元分离,解决大量数据深度处理时的存储墙和功耗墙问题。

附图说明

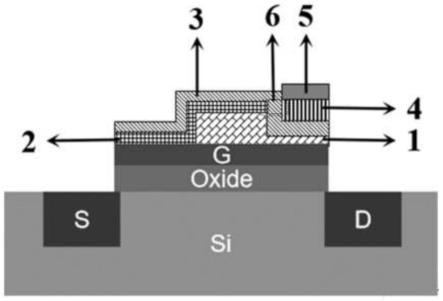

34.图1为本发明提出的一种亚纳米级别的铁电存储计算一体器件剖面图;

35.图2为现有的纳米级技术节点制造的金属氧化物场效应晶体管mosfet剖面图;

36.图3为本发明中在金属氧化物半导体场效应晶体管的基础上制备底电极层;

37.图4为本发明中在底电极层上制备铁电层;

38.图5为本发明中在铁电层上依次沉积顶电极和金属电极;

39.图6为本发明中在铁电存储计算一体阵列的设计;

40.图7为本发明的铁电存储计算电原理图。

41.其中,1-隔离层、2-底电极、3-铁电层,4-顶电极,5-金属电极、6-有效工作区域。

具体实施方式

42.本发明为了解决新型铁电存储计算一体器件的工艺兼容性问题,通过器件结构创新和选用低维材料,突破传统的冯诺依曼架构,缓解逻辑与存储之间的设计冲突,实现铁电存储器与晶体管的纳米集成,避免si通道的非理想界面,获得低电压下高效写入能力,根据本发明第一方面提高循环稳定性能。

43.我们选用低维材料作为铁电存储器底电极,在特定维度形成分子乃至原子尺寸的厚度,同时通过结构创新,在隔离层上形成台阶状分布,使得铁电存储器纵向垂直分布,有效电场来自底电极层厚度,能够更好与现有晶体管纳米级别工艺技术相匹配ar=1:10,实现最佳写入和读出性能的同时,解决尺寸微缩难的问题,使得铁电存储器mfm的尺寸达到亚

纳米分子或原子尺寸级别。所得铁电存储计算一体阵列具备读写速度快、抗疲劳性能突出、功耗低以及结构简单等优势,能够有效突破传统冯诺依曼架构计算和存储单元分离,解决大量数据深度处理时的存储墙和功耗墙问题。

44.以下结合附图对本发明的具体实施方式作出详细说明。

45.本发明的第一方面提出了一种亚纳米级铁电存储计算一体器件,所述铁电存储计算一体器件包括,铁电存储器和mosfet晶体管;

46.所述铁电存储器作为数据存储元件,所述mosfet晶体管执行数据计算功能;

47.采用低维材料制作所述铁电存储器的底电极2,所述铁电存储器从上到下依次包括:金属电极5、顶电极4、铁电层3和底电极2;各层均位于mosfet晶体管的栅极之上依预定构型层叠制作;

48.所述mosfet晶体管作为所述铁电存储计算一体器件的基体,所述铁电存储器的底电极2与所述mosfet晶体管的栅极直接连接;

49.所述铁电存储器的有效工作区域6的尺寸仅由底电极2的厚度方向相对于铁电层3的宽度来确定,以将所述铁电存储器有效工作区6的线宽尺寸限定在亚纳米级别。

50.如图1所示本发明的亚纳米级别的铁电存储计算一体器件,铁电存储器底电极2采用低维材料,3为铁电层,4为顶电极,5为金属电极。铁电存储器底电极2与晶体管栅极左侧部分相连,右侧不相连部分通过隔离层1分开,且隔离层上右半部分呈台阶状,使得铁电存储器有效电场来自底电极层厚度,其有效工作区域为6。通过控制底电极2的层厚度,使得铁电存储器mfm的尺寸达到亚纳米分子或原子尺寸级别,更好与现有cmos晶体管纳米级别工艺技术相匹配,且控制铁电存储器的面积与晶体管mosfet的面积比ar为:ar=1:5到1:20。优选为ar=1:10,实现存储计算一体技术最佳的写入和读出性能。

51.如本发明第一方面的器件,所述铁电存储计算一体器件还包括一台阶状隔离层1,所述铁电存储器与mosfet晶体管的栅极之间被台阶状隔离层1隔离并绝缘,所述台阶状隔离层1的位于所述栅极中间区域上部的所述台阶状隔离层1左侧部分高于所述台阶状隔离层1右侧部分一个预定尺寸。可参见附图3所示。

52.如本发明第一方面的器件,位于所述底电极2和所述台阶状隔离层1之上的所述铁电层3呈凸字形状,所述铁电层3完全覆盖所述台阶状隔离层1和所述底电极2;如附图5所示。

53.所述顶电极4和所述金属电极5仅设置在所述隔离层1右侧部分的台阶下层对应的所述铁电层3之上。如附图6所示。

54.如本发明第一方面的器件,控制铁电存储器的面积与所述mosfet晶体管的面积比ar的取值范围为:1:5到1:20。

55.附图2是用于制作亚纳米级铁电存储计算一体器件的mosfet晶体管结构剖面图,图示为一个典型的mosfet晶体管,其中s为源极,d是漏极,g是栅极。在现有的工艺条件下,mosfet晶体管电极的宽度是大于5-7纳米的,电极宽度还无法做到亚纳米的级别。图中的晶体管的各个电极尺寸都是大于亚纳米级别的。

56.但是使用溅射、气相沉积等工艺,将半导体或金属的淀积层做到亚纳米级别是可以实现的。如附图1所示,所述铁电存储器包括:金属电极5、顶电极4、铁电层3和底电极2;其中作为铁电存储器的两个极板的顶电极4和底电极2之间的铁电层3是垂直方向设置,它们

的有效工作区域6仅由铁电层3的厚度决定。由于铁电存储器的顶电极4、铁电层3和底电极2的厚度均能做到亚纳米级别;因此所述铁电存储器的有效尺寸限定在亚纳米级别。

57.附图7是铁电存储计算一体器件的等效电原理图。所述mosfet晶体管的源极s连接地线gnd,漏极d连接位线bit line,栅极连接铁电存储器mfm的底电极,铁电存储器mfm的金属电极5与字线word line连接。其中带有存储功能的铁电存储器mfm作为数据存储元件,而mosfet晶体管用作计算元件。

58.本发明的第二方面提出一种亚纳米级铁电存储计算一体器件的制备方法,所述制备方法包括以下步骤:

59.步骤1,以纳米级尺寸的金属氧化物场效应晶体管mosfet晶片为基板,在制作铁电存储器之前,对所述mosfet晶片执行清洗和烘干;

60.步骤2,在经步骤1处理的所述mosfet晶片上制备隔离层1,对所述隔离层1执行多次光刻图形化,形成位于mosfet栅极上面的台阶状隔离层1,所述台阶状隔离层1的台阶上层区域的高度高于台阶下层区域一个预定尺寸;所述台阶状隔离层1仅覆盖所述mosfet栅极的右侧部分区域;

61.步骤3,在台阶状隔离层1上制备所述铁电存储器的底电极2层;对所述底电极2层进行光刻图形化,使底电极2层覆盖所述mosfet栅极上没有被台阶状隔离层1覆盖的区域和所述台阶状隔离层1的台阶上层区域,而所述台阶下层区域不被所述底电极2层覆盖;可参见图4所示;

62.步骤4,在步骤3完成后,制备铁电层3,所述铁电层3制成后执行光刻图形化,仅保留位于mosfet栅极之上的铁电层3,将其余的铁电层3刻蚀去除;

63.步骤5,在铁电层3上依次沉积顶电极4层和金属电极5层,对所述顶电极4层和所述金属电极5层执行光刻图形化,仅保留位于所述台阶状隔离层1的台阶下层区域上的顶电极4层和金属电极5层,将顶电极4层和金属电极5层的多余部分刻蚀去除,以构成顶电极4和金属电极5;

64.步骤6,由所述mosfet晶片上由多个mosfet晶体管构成晶体管阵列,将所述晶体管阵列中各个mosfet晶体管的源级互联形成接地线,将所述晶体管阵列的各个mosfet晶体管的漏极互联形成位线,将各个铁电存储器的金属电极5互联形成字线,从而使所述晶体管阵列中的亚纳米级铁电存储计算一体器件同时具备存储和多值计算功能。

65.如本发明第二方面的制备方法,所述台阶状隔离层1采用低介电常数材料三氧化二铝或二氧化硅;所述台阶状隔离层1制备工艺采用以下方法之一:溅射法、原子力沉积法、化学气相沉积法或物理气相沉积法。

66.如本发明第二方面的制备方法,所述底电极2层采用的低维材料从以下材料中择一选用:二维薄膜材料、一维纤维材料或零维量子点材料;所述低维材料的尺度均在纳米级;

67.步骤3中采用所述低维材料湿法转移制备方法制备所述铁电存储器的底电极2层,所述湿法转移制备方法采用以下方法之一:转印、喷涂、旋涂或刮涂;

68.所述顶电极4材料为氮化钛;

69.所述金属电极5材料从以下材料中择一选用:钨、铝、镍或铂;

70.所述顶电极4和所述金属电极5的制备工艺采用以下方法之一:溅射、原子力沉积、

化学气相沉积、物理气相沉积或热蒸镀。

71.如本发明第二方面的制备方法,所述二维薄膜材料从以下材料中择一选用:石墨烯或mos2;所述一维纤维材料采用银纳米线;所述零维量子点材料采用金量子点。

72.如本发明第二方面的制备方法,所述铁电层3薄膜材料包括以下材料之一或它们的混合物:hfo2、zro2、hfxzr

1-x

o2、锆钛酸铅;所述铁电层3的制备工艺采用以下方法之一:溅射、原子力沉积、化学气相沉积或物理气相沉积。

73.如本发明第二方面的制备方法,步骤6还包括在氮气气氛中快速退火使得铁电薄膜结晶。

74.最后应说明的是,以上实施方式仅用以说明本发明实施例的技术方案而非限制,尽管参照以上较佳实施方式对本发明实施例进行了详细说明,本领域的普通技术人员应当理解,可以对本发明实施例的技术方案进行修改或等同替换都不应脱离本发明实施例的技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1