半导体结构及其制造方法、存储器及其操作方法与流程

本公开涉及半导体,涉及但不限于一种半导体结构及其制造方法、存储器及其操作方法。

背景技术:

1、随着当今科学技术的不断发展,半导体存储装置的性能越来越强大,而特征尺寸则越来越小。其中,一次性可编程(one time programmable,otp)存储器是一种非易失性存储器(non-volatile memory,nvm),在失去电源的情况下仍能保持存储的数据。一次性可编程存储器只能进行一次烧录编程,不可以通过电擦除,可应用于程序代码存储器、串行配置存储器、芯片上系统(system-on-chip,soc),并在id识别、存储修复等方面发挥作用。

2、目前,一次性可编程存储器主要采用动态随机存储器(dynamic random accessmemory,dram)相似的结构,其包括一个选择晶体管和一个可击穿的电容(1t1c),由于电容中介质层的击穿是不可逆的,可以通过读取电容的击穿状态获得固化的存储数据。然而,一次性可编程存储器面临存储单元占用面积较大、集成度较低、制造工艺复杂、制造成本较高等问题。

技术实现思路

1、有鉴于此,本公开实施例提供了一种半导体结构及其制造方法、存储器及其操作方法。

2、第一方面,本公开实施例提供了一种半导体结构,包括:

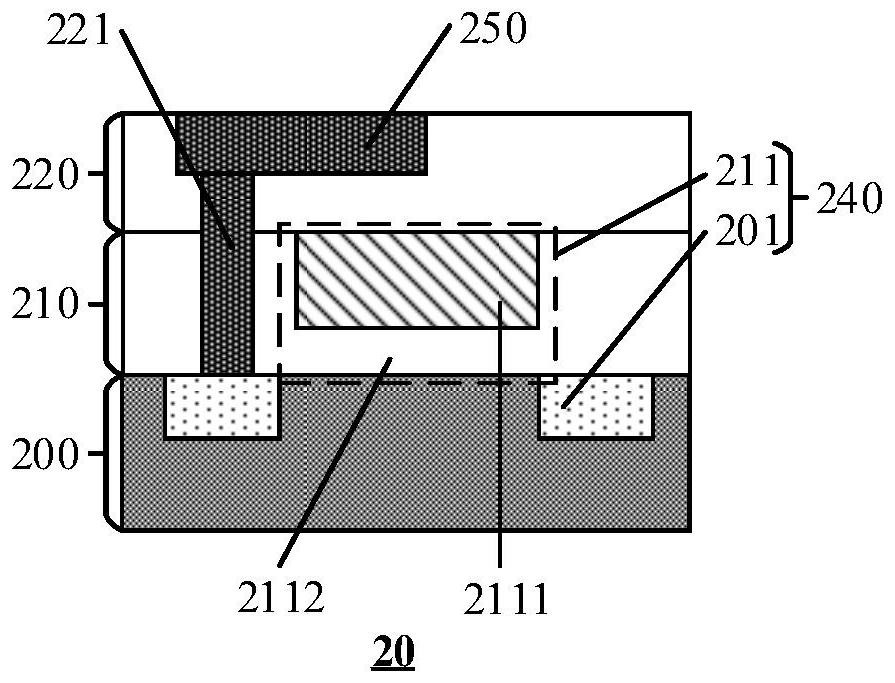

3、衬底,衬底中具有靠近衬底表面的多个有源区;栅极结构,位于衬底上方第一结构层;栅极结构与有源区构成选择晶体管;反熔丝位结构,位于第一结构层上方的第二结构层,且反熔丝位结构通过第一连接结构与一个选择晶体管的有源区连接;反熔丝位结构的击穿状态和非击穿状态用于表示不同的存储数据。

4、在一些实施例中,反熔丝位结构包括:第一电极,第一电极通过第一连接结构与有源区连接;第二电极,第二电极与第一电极位于同一平面内,且第一电极和第二电极所在的平面平行于衬底的表面;反熔丝位介质层,位于第一电极和第二电极之间且连接第一电极和第二电极;其中,击穿状态为反熔丝位介质层被击穿的状态,非击穿状态为反熔丝位介质层未被击穿的状态。

5、在一些实施例中,位于平行于栅极结构的延伸方向上的多个反熔丝位结构的第二电极相互连通。

6、在一些实施例中,第一电极中靠近第二电极的一侧具有凸起结构,第二电极中靠近第一电极的一侧具有与凸起结构对应的凹陷结构。

7、在一些实施例中,反熔丝位结构在衬底上的投影与栅极结构在衬底上的投影至少部分重叠。

8、在一些实施例中,第一结构层还包括至少包围栅极结构的栅电极底面和侧面的第一隔离层;第二结构层还包括至少包围反熔丝位结构底面和侧面的第二隔离层;第一连接结构贯穿第一隔离层和第二隔离层。

9、在一些实施例中,第一隔离层为氧化物材料,其中,栅极结构中的部分第一隔离层用于作为选择晶体管的栅介质。

10、在一些实施例中,有源区包括:具有相同掺杂类型的第一掺杂区和第二掺杂区,第一掺杂区与第二掺杂区分别位于栅极结构的两侧;其中,第一掺杂区通过第一连接结构与反熔丝位结构连接。

11、在一些实施例中,半导体结构还包括:第一金属线,位于第二结构层上方的第三结构层;第一金属线通过第二连接结构与第二掺杂区连接;第一金属线的延伸方向垂直于栅极结构的延伸方向。

12、在一些实施例中,第三结构层还包括至少包围第一金属线底面和侧面的第三隔离层。

13、在一些实施例中,两个相邻的反熔丝位结构对称设置;每两个对称设置的反熔丝位结构连接的选择晶体管共用同一个第二掺杂区。

14、在一些实施例中,半导体结构还包括:隔离结构,位于两个相邻的第一掺杂区之间;其中,两个相邻的第一掺杂区为:相邻且不共用第二掺杂区的两个选择晶体管对应的第一掺杂区。

15、第二方面,本公开实施例提供了一种半导体结构的制造方法,包括:提供衬底,衬底中具有靠近衬底表面的多个有源区;在衬底上方形成包含有栅极结构的第一结构层;栅极结构与栅极结构下方有源区构成选择晶体管;在第一结构层上方形成包含有反熔丝位结构的第二结构层,并形成连接反熔丝位结构和选择晶体管的有源区的第一连接结构;反熔丝位结构的击穿状态和非击穿状态用于表示不同的存储数据。

16、在一些实施例中,在第一结构层上方形成包含有反熔丝位结构的第二结构层,并形成连接反熔丝位结构和选择晶体管的有源区的第一连接结构,包括:在第一结构层上方沉积绝缘材料;绝缘材料用于形成第二结构层中的第二隔离层;在绝缘材料中形成第一沟槽和第二沟槽,并在第一沟槽中形成贯穿第一结构层的第一连接孔;在第一连接孔中填充导电材料,形成第一连接结构;在第一沟槽和第二沟槽中填充导电材料,分别形成第一电极和第二电极;第一电极与第二电极以外的绝缘材料为第二隔离层;第一电极与第二电极之间的部分第二隔离层用于作为反熔丝位结构的反熔丝位介质层;其中,击穿状态为反熔丝位介质层被击穿的状态,非击穿状态为反熔丝位介质层未被击穿的状态。

17、在一些实施例中,第一沟槽和第二沟槽的延伸方向平行于栅极结构的延伸方向。

18、在一些实施例中,在第一沟槽和第二沟槽中填充导电材料,分别形成第一电极和第二电极,包括:在第一沟槽和第二沟槽中填充导电材料;去除至少部分第一沟槽中的导电材料,形成多个相互分离的第一电极,以及位于平行于栅极结构的延伸方向上同一直线的多个反熔丝位结构中相互连通的第二电极。

19、第三方面,本公开实施例提供了一种存储器的操作方法,存储器包括上述实施例任一的半导体结构;方法包括:根据待写入的数据,击穿存储器的反熔丝位结构中的一个目标反熔丝位结构,使目标反熔丝位结构由非击穿状态切换为击穿状态;且保持非目标反熔丝位结构的非击穿状态;其中,非目标反熔丝位结构为目标反熔丝位结构以外的反熔丝位结构。

20、在一些实施例中,击穿存储器的反熔丝位结构中的一个目标反熔丝位结构,使目标反熔丝位结构由非击穿状态切换为击穿状态,包括:对目标反熔丝位结构连接的选择晶体管的栅极结构施加第一电压,以导通选择晶体管;对选择晶体管连接的第一金属线施加第二电压;对目标反熔丝位结构的第二电极施加第三电压,以使目标反熔丝位结构由非击穿状态切换为击穿状态;其中,第二电压与第三电压之间的电压差大于或等于反熔丝位结构的击穿电压。

21、在一些实施例中,保持非目标反熔丝位结构的非击穿状态,包括:对非目标反熔丝位结构连接的选择晶体管的栅极结构施加第一电压,以导通选择晶体管;对选择晶体管连接的第一金属线施加第四电压;对非目标反熔丝位结构的第二电极施加第三电压,以使非目标反熔丝位结构保持非击穿状态;其中,第四电压与第三电压之间的电压差小于反熔丝位结构的击穿电压。

22、在一些实施例中,保持非目标反熔丝位结构的非击穿状态,包括:对非目标反熔丝位结构连接的选择晶体管的栅极结构施加第五电压,以截止选择晶体管,使非目标反熔丝位结构保持非击穿状态。

23、第四方面,本公开实施例提供了一种存储器,包括:存储阵列,存储阵列中包括上述实施例任一的半导体结构;与存储阵列耦接的外围电路。

24、在本公开实施例提供的半导体结构中,栅极结构位于衬底上方的第一结构层,反熔丝位结构位于第一结构层上方的第二结构层,且反熔丝位结构通过第一连接结构与衬底中的有源区连接。如此,反熔丝位结构不需要在水平方向上占用额外的面积,提高了存储器的集成度,且减少了形成反熔丝位结构所需要的掩膜工艺次数,从而简化了制造工艺。

- 还没有人留言评论。精彩留言会获得点赞!