GaNHEMT器件的共源共栅封装结构及方法与流程

gan hemt器件的共源共栅封装结构及方法

技术领域

1.本发明涉及电子器件领域,特别是涉及一种增强型gan hemt器件的共源共栅封装结构及方法。

背景技术:

2.随着通信技术的发展,消费者对手机充电器的要求越来越高,同时电动汽车发展势头也非常迅猛,对充电的需求也越来越高,小体积高效率是消费者的主要诉求,快充技术应运而生,目前的快充技术主要采用的主开关管实现,目前主开关管的主流方案是:使用d-mode gan hemt合封而成的共源共栅器件。采用gan基器件可以充分发挥gan材料耐高温、耐高压、功率密度大、工作频率高的优势,具有非常大的市场潜力。但是现有的共源共栅器件由于陶瓷板的使用,散热性能差而影响开关频率。对此,本发明提出一种增强型gan hemt器件的共源共栅封装结构及方法。

技术实现要素:

3.本发明的目的是提供一种gan hemt器件的共源共栅封装结构及方法,采用耗尽型gan hemt器件和低压si mos器件级联方式,并且采用面板级扇出型先进封装技术,具有无键合、无框架、无基板的优势,可以有效减小寄生参数,提高增强型gan hemt器件的开关频率,降低开关损耗。

4.为实现上述目的,本发明提供了如下方案:一种gan hemt器件的共源共栅封装结构,包括:依次层叠设置的第一布线层、第一包封层、第一器件层、第二包封层和第二布线层以及贯穿所述第一包封层、所述第一器件层和所述第二包封层的第一金属柱;所述第一器件层包括si mos器件和gan hemt器件;所述si mos器件的源极和所述gan hemt器件的源极均设于靠近所述第二包封层的一侧;所述第一包封层设有与所述si mos器件的漏极相对应的第一漏极通孔;所述第二包封层设有与所述si mos器件的源极和栅极分别对应的第一源极通孔和第一栅极通孔;所述第二包封层还设有与所述gan hemt器件的源极、栅极和漏极分别对应的第二源极通孔、第二栅极通孔和第二漏极通孔;所述第一布线层包括第一导通线,所述第一导通线的一端通过所述第一漏极通孔与所述si mos器件的漏极连接,所述第一导通线的另一端与所述第一金属柱的一端连接;所述第二布线层包括第二导通线、第三导通线、第一引出线、第二引出线和第三引出线;所述第二导通线的一端通过所述第一源极通孔与所述si mos器件的源极连接;所述第二导通线的另一端通过所述第二栅极通孔与所述gan hemt器件的栅极连接;所述第三导通线的一端通过所述第二源极通孔与所述gan hemt器件的源极连接,

所述第三导通线的另一端与所述第一金属柱的另一端连接;所述第一引出线的一端通过所述第一源极通孔与所述si mos器件的源极连接;所述第一引出线的另一端作为封装结构的源极引脚;所述第二引出线的一端通过所述第一栅极通孔与所述si mos器件的栅极连接;所述第二引出线的另一端作为所述封装结构的栅极引脚;所述第三引出线的一端通过所述第二漏极通孔与所述gan hemt器件的漏极连接;所述第三引出线的另一端作为所述封装结构的漏极引脚。

5.一种gan hemt器件的共源共栅封装结构,包括:包括:依次层叠设置的第三布线层、第三包封层、第二器件层、第四包封层和第四布线层,贯穿所述第四布线层、所述第四包封层、所述第二器件层和所述第三包封层和所述第三布线层的第二金属柱和第三金属柱;所述第二器件层包括si mos器件和gan hemt器件;所述si mos器件的源极和所述gan hemt器件的衬底侧均设于靠近所述第四包封层的一侧;所述si mos器件的漏极与所述gan hemt器件的源极连接;所述si mos器件的栅极与所述第二金属柱的一端连接;所述第二金属柱的另一端贯穿所述第二器件层、所述第三包封层和所述第三布线层后连接封装结构的栅极引脚的引出线;所述si mos器件的源极通过连通线贯穿所述第四包封层和所述第四布线层与所述第三金属柱的一端连接;所述第三金属柱的另一端贯穿所述第二器件层、所述第三包封层和所述第三布线层后连接所述封装结构的源极引脚的引出线;所述gan hemt器件的栅极与所述第三金属柱的另一端连接;所述gan hemt器件的漏极贯穿所述第三包封层和所述第三布线层后连接所述封装结构的漏极引脚的引出线;所述第三布线层上包括连接所述si mos器件的漏极与所述gan hemt器件的源极的连通线、连接所述gan hemt器件的栅极与所述第三金属柱的另一端的连通线、所述封装结构的栅极引脚的引出线、所述封装结构的源极引脚的引出线和所述封装结构的漏极引脚的引出线;所述第四布线层上包括连接所述si mos器件的源极和所述第三金属柱的连通线。

6.一种gan hemt器件的共源共栅封装方法,包括:将si mos器件和gan hemt器件分别减薄至预设厚度,得到减薄后的si mos器件和减薄后的gan hemt器件;所述减薄后的si mos器件和所述减薄后的gan hemt器件构成第一器件层;在所述减薄后的si mos器件的漏极一侧和所述减薄后的gan hemt器件的硅衬底侧设置第一包封层;在所述减薄后的si mos器件的源极和栅极一侧和所述减薄后的gan hemt器件的源极、栅极和漏极一侧设置第二包封层;在所述第一包封层上设置第一漏极通孔;所述第一漏极通孔用于裸露出所述减薄后的si mos器件的漏极;在所述第二包封层上设置裸露所述减薄后的si mos器件的源极的第一源极通孔、裸露所述减薄后的si mos器件的栅极的第一栅极通孔和分别裸露所述减薄后的gan hemt

器件的源极、栅极和漏极的第二源极通孔、第二栅极通孔和第二漏极通孔;通过打孔、溅射的方式设置贯穿于所述第一包封层、所述第一器件层、所述第二包封层的第一金属柱;在所述第一包封层上,将所述减薄后的si mos器件的漏极与所述第一金属柱的一端连接;在所述第二包封层上,将所述减薄后的si mos器件的源极和所述减薄后的gan hemt器件的栅极通过各自对应的通孔进行连接;所述减薄后的gan hemt器件的源极与所述第一金属柱的另一端连接;将所述减薄后的si mos器件的源极和栅极通过化学镀制备布线的方式引出分别作为封装结构源极引脚和栅极引脚;所述减薄后的gan hemt器件的漏极通过化学镀制备布线的方式引出作为所述封装结构漏极引脚。

7.根据本发明提供的具体实施例,本发明公开了以下技术效果:本发明提供一种gan hemt器件的共源共栅封装结构及方法,其中,使用的是氮化镓器件,寄生电容小,无反向恢复电荷,使得开关速度更快,开关损耗更低;驱动的是低压si mos器件,驱动电压范围宽,可以工作在9v,最大可以工作在20v,驱动电压范围变宽提高了可靠性,降低新风险,可供选择的控制集成芯片和驱动集成芯片多;使用耗尽型gan hemt器件和低压si mos器件级联合封实现高效的高频开关。采用面板级扇出型先进封装的方式,避免合封时使用陶瓷基板造成成本昂贵,器件较厚,散热特性不够优秀的问题,降低了封装成本,减小了器件的厚度,提高了散热性能,面板级扇出型先进封装技术具有无键合、无框架、无基板的优势,可以有效减小寄生参数,实现高效的高频开关。

附图说明

8.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

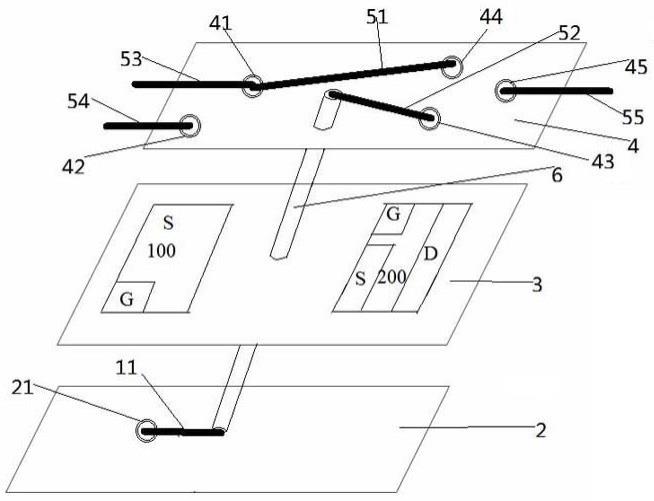

9.图1为本发明实施例1提供的gan hemt器件与si mos器件各金属电极的连接关系第一侧视图;图2为本发明实施例1提供的gan hemt器件与si mos器件各金属电极的连接关系第二侧视图;图3为本发明实施例1提供的gan hemt器件与si mos器件各金属电极的连接关系第一俯视图;图4为本发明实施例1提供的一种gan hemt器件的共源共栅封装结构示意图;图5为本发明实施例2提供的gan hemt器件与si mos器件各金属电极的连接关系第三侧视图;图6为本发明实施例2提供的gan hemt器件与si mos器件各金属电极的连接关系第四侧视图;图7为本发明实施例2提供的gan hemt器件与si mos器件各金属电极的连接关系

第二俯视图;图8为本发明实施例2提供的gan hemt器件与si mos器件各金属电极的连接关系第三俯视图;图9为本发明实施例2提供的gan hemt器件与si mos器件各金属电极的连接关系仰视图;图10为本发明实施例3提供的一种gan hemt器件的共源共栅封装方法流程图。

10.附图标记:100:si mos器件;200:gan hemt器件;11:第一导通线;2:第一包封层;21:第一漏极通孔;3:第一器件层;4:第二包封层;41:第一源极通孔;42:第一栅极通孔;43:第二源极通孔;44:第二栅极通孔;45:第二漏极通孔;51:第二导通线;52:第三导通线;53:第一引出线;54:第二引出线;55:第三引出线;6:第一金属柱;7:第二金属柱;8:第三金属柱;9:第四金属柱;101:第一连通线;102:第二连通线;103:第三连通线;104:第四连通线;105:第五连通线。

具体实施方式

11.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

12.本发明的目的是提供一种gan hemt器件共源共栅封装结构及方法,采用耗尽型gan hemt器件200和低压si mos器件100级联方式,并且采用面板级扇出型先进封装技术,具有无键合、无框架、无基板的优势,可以有效减小寄生参数,提高增强型gan hemt器件200的开关频率,降低开关损耗。

13.本发明提供一种新型的共源共栅封装方案,即共源共栅结构的封装方案,采用面板级扇出型先进封装技术方案实现耗尽型gan hemt器件200和低压si mos器件100级联,si mos器件100的源极s、栅极g、gan hemt器件200的漏极d分别用化学镀制备布线的方式引出,作为封装器件的源极、栅极、漏极,如图1、图2、图3所示。在封装器件布置第一金属柱6,第一金属柱6上方与si mos器件100的漏极d相连,下方与gan hemt器件200的源极s相连。

14.封装步骤为:把si mos器件100、gan hemt器件200减薄到合适厚度后、正面电极化镀后,正面向下贴附在玻璃基板一侧形成的衬底上,对两个器件背面进行布线,然后对两颗器件进行包封,包封层的材料可以是emc(epoxy molding compound,环氧树脂模塑料)等具有较好密封性和易塑封性的材料,然后去除玻璃基板衬底,在通过打孔溅射等方式设置金属柱,并对正面化学镀的电极及金属柱进行布线,设置封装器件的引脚。

15.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

16.实施例1如图1至4所示,本实施例提供一种gan hemt器件的共源共栅封装结构,包括:依次层叠设置的第一布线层、第一包封层2、第一器件层3、第二包封层4和第二布

线层以及贯穿所述第一包封层2、所述第一器件层3和所述第二包封层4的第一金属柱6;所述第一器件层3包括si mos器件100和gan hemt器件200;所述si mos器件100的源极和所述gan hemt器件200的源极均设于靠近所述第二包封层的一侧;为了便于第一金属柱6的设置以及减小器件的体积,可以要求所述si mos器件100和所述gan hemt器件200间隔设置;进一步的,所述第一金属柱6贯穿于所述si mos器件100和所述gan hemt器件200之间。

17.作为另一种可选的实施方式,可以将所述gan hemt器件200的衬底与所述第一金属柱6连接;所述gan hemt器件200的衬底与所述gan hemt器件200的源极、栅极和漏极相连。

18.所述第一包封层2设有与所述si mos器件100的漏极相对应的第一漏极通孔21;所述第二包封层4设有与所述si mos器件100的源极和栅极分别对应的第一源极通孔41和第一栅极通孔42;所述第二包封层4还设有与所述gan hemt器件200的源极、栅极和漏极分别对应的第二源极通孔43、第二栅极通孔44和第二漏极通孔45;所述第一布线层包括第一导通线11,所述第一导通线11的一端通过所述第一漏极通孔21与所述si mos器件100的漏极连接,所述第一导通线11的另一端与所述第一金属柱6的一端连接;所述第二布线层包括第二导通线51、第三导通线52、第一引出线53、第二引出线54和第三引出线55;所述第二导通线51的一端通过所述第一源极通孔41与所述si mos器件100的源极连接;所述第二导通线51的另一端通过所述第二栅极通孔44与所述gan hemt器件200的栅极连接;所述第三导通线52的一端通过所述第二源极通孔43与所述gan hemt器件200的源极连接,所述第三导通线52的另一端与所述第一金属柱6的另一端连接;所述第一引出线53的一端通过所述第一源极通孔41与所述si mos器件100的源极连接;所述第一引出线53的另一端作为封装结构的源极引脚;所述第二引出线54的一端通过所述第一栅极通孔42与所述si mos器件100的栅极连接;所述第二引出线54的另一端作为所述封装结构的栅极引脚;所述第三引出线55的一端通过所述第二漏极通孔45与所述gan hemt器件200的漏极连接;所述第三引出线55的另一端作为所述封装结构的漏极引脚。

19.为了保护si mos器件100的漏极与第一金属柱6的连接线、si mos器件100的源极与gan hemt器件200的栅极的连接线以及gan hemt器件200的源极与第一金属柱6的连接线,可以在所述第一布线层的下面设第一塑封层;所述第二布线层的上面还设有第二塑封层;所述第一塑封层,用于对所述第一导通线11进行塑封;所述第二塑封层,用于对所述第二导通线51和所述第三导通线52进行塑封;所述第一引出线53的另一端贯穿所述第二塑封层作为所述封装结构的源极引脚;所述第二引出线54的另一端贯穿所述第二塑封层作为所述封装结构的栅极引脚;所述第三

引出线55的另一端贯穿所述第二塑封层作为所述封装结构的漏极引脚。

20.本实施例中,使用耗尽型gan hemt器件200和低压硅器件级联合封实现高效的高频开关;驱动方案驱动电压范围宽,可供选择的控制集成芯片和驱动集成芯片多;相比传统的合封方案此方案采用面板级扇出型先进封装可省掉陶瓷基板,成本低廉,同时减小了封装器件厚度,有利于散热;面板级扇出型先进封装技术具有无键合、无框架、无基板的优势,可以有效减小寄生参数,高频性能优秀。

21.实施例2本实施例提供了一种gan hemt器件的共源共栅封装结构,封装结构的各层设置与实施例1相同,均包括两个布线层、两个包封层和一个器件层,具体为依次层叠设置的第三布线层、第三包封层、第二器件层、第四包封层和第四布线层,与实施例1不同的是第二器件层上si mos器件100和gan hemt器件200的放置不同,si mos器件100和gan hemt器件200各极之间实现连接的方式不同,即布线方式不同。

22.封装结构包括:依次层叠设置的第三布线层、第三包封层、第二器件层、第四包封层和第四布线层,贯穿所述第四布线层、所述第四包封层、所述第二器件层和所述第三包封层和所述第三布线层的第二金属柱7和第三金属柱8;如图5至9所示,所述第二器件层包括si mos器件100和gan hemt器件200;所述si mos器件100的源极和所述gan hemt器件200的衬底侧均设于靠近所述第四包封层的一侧;所述si mos器件100的漏极与所述gan hemt器件200的源极连接;可选的,所述si mos器件100的漏极与所述gan hemt器件200的源极通过第四金属柱9连接;所述第四金属柱9设于所述第三布线层上。

23.所述si mos器件100的栅极与所述第二金属柱7的一端连接;所述第二金属柱7的另一端贯穿所述第二器件层、所述第三包封层和所述第三布线层后连接封装结构的栅极引脚的引出线,该引出线即实施例1中的第二引出线54;所述si mos器件100的源极通过连通线贯穿所述第四包封层和所述第四布线层与所述第三金属柱8的一端连接;所述第三金属柱8的另一端贯穿所述第二器件层、所述第三包封层和所述第三布线层后连接所述封装结构的源极引脚的引出线,该引出线即实施例1中的第一引出线53;所述gan hemt器件200的栅极与所述第三金属柱8的另一端连接;所述gan hemt器件200的漏极贯穿所述第三包封层和所述第三布线层后连接所述封装结构的漏极引脚的引出线,该引出线即实施例的第三引出线55;所述第三布线层上包括连接所述si mos器件100的漏极与所述gan hemt器件200的源极的第一连通线101、连接所述gan hemt器件200的栅极与所述第三金属柱8的另一端的第二连通线102、所述封装结构的栅极引脚的引出线、所述封装结构的源极引脚的引出线和所述封装结构的漏极引脚的引出线;所述第四布线层上包括连接所述si mos器件100的源极和所述第三金属柱8的第三连通线103和连接所述si mos器件100的栅极和所述第二金属柱7的第四连通线104。

24.为实现gan hemt器件200的衬底与si mos器件100的源极共电位,可以将所述gan hemt器件200的衬底与所述si mos器件100的源极连接,可以通过图8中的第五连通线105连接。

25.同样的为了保护gan hemt器件200与si mos器件100之间的连接线,可以在第三布线层的下面和第四布线层的上面设置塑封层,可以参考实施例1中的塑封层设置方式。

26.实施例3如图10所示,本实施例提供一种gan hemt器件的共源共栅封装方法,包括:s1:将si mos器件100和gan hemt器件200分别减薄至预设厚度,得到减薄后的si mos器件100和减薄后的gan hemt器件200;所述减薄后的si mos器件100和所述减薄后的gan hemt器件200构成第一器件层3;s2:在所述减薄后的si mos器件100的漏极一侧和所述减薄后的gan hemt器件200的硅衬底侧设置第一包封层2;s3:在所述减薄后的si mos器件100的源极和栅极一侧和所述减薄后的gan hemt器件200的源极、栅极和漏极一侧设置第二包封层4;s4:在所述第一包封层2上设置第一漏极通孔21;所述第一漏极通孔21用于裸露出所述减薄后的si mos器件100的漏极;s5:在所述第二包封层4上设置第一源极通孔41、第一栅极通孔42、第二源极通孔43和第二栅极通孔44和第二漏极通孔45;所述第一源极通孔41用于裸露出所述减薄后的si mos器件100的源极;所述第一栅极通孔42用于裸露出所述减薄后的si mos器件100的栅极;所述第二源极通孔43用于裸露出所述减薄后的gan hemt器件200的源极;所述第二源栅极通孔用于裸露出所述减薄后的gan hemt器件200的栅极;所述第二漏极通孔45用于裸露出所述减薄后的gan hemt器件200的漏极;s6:通过打孔、溅射的方式设置贯穿于所述第一包封层2、所述第一器件层3、所述第二包封层4的第一金属柱6;这里的第一金属柱6还可以是低电阻率通孔,可以在硅片上设置金属通孔;s7:在所述第一包封层2上,将所述减薄后的si mos器件100的漏极与所述第一金属柱6的一端连接;s8:在所述第二包封层4上,将所述减薄后的si mos器件100的源极和所述减薄后的gan hemt器件200的栅极通过各自对应的通孔进行连接;所述减薄后的gan hemt器件200的源极与所述第一金属柱6的另一端连接;将所述减薄后的si mos器件100的源极和栅极通过化学镀制备布线的方式引出分别作为封装结构源极引脚和栅极引脚;所述减薄后的gan hemt器件200的漏极通过化学镀制备布线的方式引出作为所述封装结构漏极引脚。

27.在s8之后还包括:s9:在所述第一包封层2的下侧设置第一塑封层,在所述第二包封层4的上侧设置第二塑封层;s10:在所述第二塑封层上,设置用于裸露所述封装结构源极引脚、栅极引脚和漏极引脚的通孔。

28.需要说明的是,对于实施例2的封装结构的封装方法可以参考该实施例的封装方法,原理基本相同。

29.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

30.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1