显示面板的制作方法

1.本技术涉及显示技术领域,尤其涉及一种显示面板。

背景技术:

2.随着电子产品的不断更新换代,大屏的电子产品越来越受到用户的青睐。目前,市场上的电子产品总会存在或大或小的四周边框,电子产品的发展趋势要求其边框应该越做越窄以致达到无边框的效果。全面屏电子产品凭借其超高的屏占比和极好的用户体验感,成为时下最热门的技术之一。但在实际生产过程中,很难满足无边框的要求,造成屏幕显示区域占机身正面的占比较小,影响用户的体验感。

技术实现要素:

3.本技术实施例提供一种显示面板,用于提高显示面板的正面机身的显示区的占比。

4.本技术实施例提供一种显示面板,所述显示面板包括:

5.信号传输层,位于所述显示区,所述信号传输层包括栅极驱动电路;

6.显示功能层,所述显示功能层包括像素驱动电路层和发光功能层,像素驱动电路层设置在所述信号传输层上,所述发光功能层设置在所述像素驱动电路层远离所述信号传输层的一面。

7.可选的,在本技术提供的一些实施例中,所述显示面板还包括第一信号连接线,所述第一信号连接线位于所述显示区,所述第一信号连接线用于连接所述像素驱动电路层和所述信号传输层。

8.可选的,在本技术提供的一些实施例中,所述第一信号连接线包括连接的第一信号连接段、第二信号连接段和第三信号连接段;所述显示面板包括第一过孔、第二过孔和第三过孔,所述第一信号连接段设置在所述第一过孔内,所述第二信号连接段设置在所述第二过孔内,所述第三信号连接段设置在所述第三过孔内。

9.可选的,在本技术提供的一些实施例中,所述信号传输层还包括多条第一电源走线、多条第二电源走线、多条复位信号走线、阵列测试焊盘和多条扇形走线;其中

10.所述第一信号连接段连接所述栅极驱动电路、所述第一电源走线、所述第二电源走线、所述复位信号走线、所述阵列测试焊盘或所述扇形走线,所述第三信号连接段连接所述像素驱动电路层。

11.可选的,在本技术提供的一些实施例中,所述显示面板还包括第二信号连接线,所述第二信号连接线位于所述显示区,所述第二信号连接线用于连接所述像素驱动电路层和所述信号传输层。

12.可选的,在本技术提供的一些实施例中,所述第二信号连接线包括连接的第四信号连接段、第五信号连接段和第六信号连接段;所述显示面板包括第四过孔、第五过孔和第六过孔,所述第四信号连接段设置在所述第四过孔内,所述第五信号连接段设置在所述第

五过孔内,所述第六信号连接段设置在所述第六过孔内。

13.可选的,在本技术提供的一些实施例中,所述信号传输层还包括多条第一电源走线、多条第二电源走线、多条复位信号走线、阵列测试焊盘和多条扇形走线;其中

14.所述第四信号连接段连接所述栅极驱动电路、所述第一电源走线、所述第二电源走线、所述复位信号走线、所述阵列测试焊盘或所述扇形走线,所述第六信号连接段连接所述像素驱动电路层。

15.可选的,在本技术提供的一些实施例中,所述显示面板还包括第一连接端子和第二连接端子;所述栅极驱动电路包括第一薄膜晶体管,所述第一薄膜晶体管包括第一有源层、第一栅极、第二栅极、第一源极和第一漏极,所述信号传输层还包括:

16.衬底,所述第一有源层设置在所述衬底上;

17.第一栅极绝缘层,设置在所述衬底上,所述第一栅极设置在所述衬底上,且所述第一连接端子和所述第一栅极同层且同材料;

18.第二栅极绝缘层,设置在所述第一栅极绝缘层上,所述第二栅极绝缘层覆盖所述第一栅极和所述第一连接端子,所述第二栅极和所述第二连接端子设置在所述第二栅极绝缘层上,所述第二栅极和所述第二连接端子同层且同材料;

19.第一层间绝缘层,设置在所述第二栅极绝缘层上,且所述第一层间绝缘层覆盖所述第二栅极和所述第二连接端子,所述第一过孔贯穿所述第一层间绝缘层和所述第二栅极绝缘层,所述第一信号连接段通过所述第一过孔与所述第一连接端子连接,所述第四过孔贯穿所述第一层间绝缘层,所述第四信号连接段通过所述第四过孔与所述第二连接端子连接,所述第一源极和所述第一漏极分别通过第一接触孔和第二接触孔和所述第一有源层连接;

20.第二层间绝缘层,设置在所述第一层间绝缘层上,所述第二过孔贯穿所述第二层间绝缘层,所述第二信号连接段通过所述第二过孔和第一信号连接段连接,所述第五过孔贯穿所述第二层间绝缘层,所述第五信号连接段通过所述第五过孔和所述第四信号连接段连接。

21.可选的,在本技术提供的一些实施例中,所述显示面板还包括第三连接端子和第四连接端子;所述像素驱动电路层包括:

22.基底层,设置在所述第二层间绝缘层上;

23.第二有源层,设置在所述基底层上;

24.绝缘层,设置在所述第二有源层远离所述基底层的一面,所述第六过孔贯穿所述绝缘层和基底层,所述第六信号连接段通过所述第六过孔和所述第五信号连接段连接;

25.第三栅极,设置在所述绝缘层远离所述第二有源层的一面,所述第三连接端子和所述第六信号连接段连接且与所述第三栅极同层且同材料;

26.层间介质层,设置在所述第三栅极远离所述绝缘层的一面,所述第三过孔贯穿所述层间介质层、所述绝缘层和所述基底层,所述第三信号连接段通过所述第三过孔和所述第二信号连接段连接;

27.第二源极和第二漏极,所述第二源极和所述第二漏极设置在所述层间介质层上,并分别通过第三接触孔和第四接触孔和所述第二有源层连接,所述第四连接端子和所述第二源极同层且材料,所述第四连接端子和所述第三信号连接段连接;

28.平坦化层,所述平坦化层设置在所述层间介质层上。

29.可选的,在本技术提供的一些实施例中,所述信号传输层还包括遮光层,所述遮光层设置在所述第二层间绝缘层上,所述遮光层通过过孔与所述第一漏极连接,且所述遮光层于所述衬底上的正投影覆盖所述第二有源层于所述衬底上的正投影。

30.可选的,在本技术提供的一些实施例中,所述显示面板还包括第七过孔,所述第七过孔贯穿所述信号传输层的部分绝缘层;所述信号传输层还包括连接走线和连接焊盘,所述连接焊盘设置在所述衬底远离所述第一层间绝缘层的一面,所述连接走线设置在所述第七过孔内,所述连接走线的一端连接所述连接焊盘,所述连接走线的另一端连接所述像素驱动电路层。

31.可选的,在本技术提供的一些实施例中,所述显示面板还包括驱动芯片,所述驱动芯片设置在衬底远离所述第一层间绝缘层的一面,所述驱动芯片和所述连接焊盘连接。

32.可选的,在本技术提供的一些实施例中,所述像素驱动电路层包括像素驱动电路,所述像素驱动电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第一电容、第二电容及有机发光二极管;所述第一晶体管、所述第二晶体管,其中,所述第一晶体管为驱动薄膜晶体管。

33.本技术实施例提供一种显示面板,显示面板包括显示区。显示面板包括信号传输层和显示功能层。其中,信号传输层位于显示区。信号传输层包括栅极驱动电路。显示功能层包括像素驱动电路层和发光功能层。像素驱动电路层设置在信号传输层上。发光功能层设置在像素驱动电路层远离信号传输层的一面。本技术实施例将用于向显示功能层传输信号的信号传输层设置在显示功能层的下方,信号传输层对应于显示区,也就是说,本技术实施例将用于为显示区的像素驱动电路提供信号的金属走线设置在显示区内,因此,信号传输层不占用非显示区域的空间,提高显示面板的显示面的显示区的占比,从而实现窄边框或无边框的设计,提高用户体验。

附图说明

34.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

35.图1为本技术实施例提供的显示面板一种结构示意图;

36.图2为本技术实施例提供的显示面板的一种剖面结构示意图;

37.图3为本技术实施例提供的信号传输层的一种结构示意图;

38.图4为本技术实施例提供的显示功能层的一种结构示意图;

39.图5为本技术实施例提供的像素驱动电路层的一种像素驱动电路的电路图。

40.图6为本技术实施例提供的显示面板的制作方法的示意图。

具体实施方式

41.为了使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术作进一步地详细描述,请参照附图中的图式,其中相同的组件符号代表相同的组件,以下的说明

是基于所示的本技术具体实施例,其不应被视为限制本技术未在此详述的其他具体实施例。本说明书所使用的词语“实施例”意指实例、示例或例证。

42.在本技术的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

43.本技术实施例提供一种显示面板。以下分别进行详细说明。需说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。

44.本技术实施例提供一种显示面板,显示面板包括显示区。显示面板包括信号传输层和显示功能层。其中,信号传输层位于显示区。信号传输层包括栅极驱动电路。显示功能层包括像素驱动电路层和发光功能层。像素驱动电路层设置在信号传输层上。发光功能层设置在像素驱动电路层远离信号传输层的一面。本技术实施例将用于向显示功能层传输信号的信号传输层设置在显示功能层的下方,信号传输层对应于显示区,使得信号传输层不占用非显示区域的空间,提高显示面板的显示面的显示区的占比,从而实现窄边框或无边框的设计,提高用户体验。

45.下面通过具体实施例对本技术提供的显示面板进行详细的阐述。

46.在已知技术中,显示面板的边框区设置有栅极驱动电路及金属走线等,栅极驱动电路及金属走线占据了显示面板的正面屏幕较大的占比,使得显示面板的屏幕的显示区的占比偏小,无法实现真正的窄边框设计。

47.本技术实施例提供一种显示面板,用于提高显示面板的显示面的显示区的占比,从而实现窄边框或无边框的设计,提高用户体验。

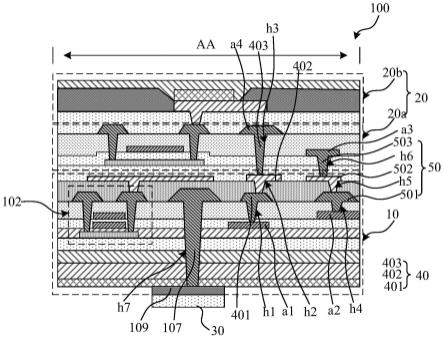

48.请结合图1和图2,图1为本技术实施例提供的显示面板一种结构示意图。图2为本技术实施例提供的显示面板的一种剖面结构示意图。显示面板100包括显示区aa。显示面板100包括信号传输层10、显示功能层20和第一信号连接线40。其中,信号传输层10位于显示区aa。信号传输层10包括栅极驱动电路102。显示功能层20包括像素驱动电路层20a和发光功能层20b,像素驱动电路层20a设置在信号传输层10上方,发光功能层20b设置在像素驱动电路层20a远离信号传输层10的一面。第一信号连接线40用于连接信号传输层10和像素驱动电路层20a。

49.本技术实施例将用于向显示功能层20传输信号的信号传输层10设置在显示功能层20的下方,使得信号传输层10位于显示区aa,因此,信号传输层不占用非显示区域的空间,提高了显示面板100的显示区aa的占比,从而实现窄边框或无边框的设计,提升显示面板100的品味,从而提高用户体验。

50.其中,第一信号连接线40位于显示区aa。

51.在一些实施例中,显示面板100还包括第二信号连接线50,第二信号连接线50位于显示区。第二信号连接线50用于连接像素驱动电路层20a和信号传输层10。

52.具体的,第一信号连接线40包括第一信号连接段401、第二信号连接段402和第三信号连接段403。第二信号连接线50包括连接的第四信号连接段501、第五信号连接段502和第六信号连接段503。

53.显示面板100包括第一过孔h1、第二过孔h2、第三过孔h3、第四过孔h4、第五过孔h5和第六过孔h6。第一信号连接段401设置在第一过孔h1内,第二信号连接段402设置在第二过孔h2内,第三信号连接段403设置在第三过孔h3内。第四信号连接段501设置在第四过孔h4内,第五信号连接段502设置在第五过孔h5内,第六信号连接段503设置在第六过孔h6内。

54.显示面板100还包括第一连接端子a1、第二连接端子a2、第三连接端子a3和第四连接端子a4。其中,第一连接端子a1和第一信号连接段401连接,第四连接端子a4和第三信号连接段403连接,第二连接端子a2和第四信号连接段501连接,第三连接端子a3和第六信号连接段503连接。

55.信号传输层10还包括多条第一电源走线110、多条第二电源走线111、多条复位信号走线113、阵列测试焊盘114和多条扇形走线115。其中,第一信号连接段401连接栅极驱动电路102、第一电源走线110、第二电源走线111、复位信号走线113、阵列测试焊盘114或扇形走线115。第三信号连接段403连接像素驱动电路层20a。具体的,栅极驱动电路102、第一电源走线110、第二电源走线111、复位信号走线113、阵列测试焊盘114或扇形走线115的输出端和第一连接端子a1连接,使得相应信号通过第一信号连接线40传输,而第四连接端子a4和像素驱动电路层20a对应的晶体管或者金属走线连接,从而实现信号传输。

56.在一些实施例中,第四信号连接段501连接栅极驱动电路102、第一电源走线110、第二电源走线111、复位信号走线113、阵列测试焊盘114或扇形走线115。第六信号连接段503连接像素驱动电路层20a。具体的,栅极驱动电路102、第一电源走线110、第二电源走线111、复位信号走线113、阵列测试焊盘114或扇形走线115的输出端和第二连接端子a2连接,使得相应信号通过第二信号连接线50传输,而第三连接端子a3和像素驱动电路层20a对应的晶体管或者金属走线连接,从而实现信号传输。

57.在本技术实施例中,将第一电源走线110、第二电源走线111、复位信号走线113、阵列测试焊盘114和多条扇形走线115均设置与显示功能层20的下方,且均对应于显示区aa,此时,无需设置用于放置金属走线的非显示区域,实现了显示面板100的无边框设计,实现了真正的全面屏,大大提高了用户体验。

58.需要说明的是,在本技术实施例中,扇形走线115可以是用于将像素驱动电路层的数据线引出的金属走线,但不限于此。

59.具体的,请参阅图3,图3为本技术实施例提供的信号传输层的一种结构示意图。栅极驱动电路102包括第一薄膜晶体管结构102a。第一薄膜晶体管结构102a包括第一有源层1021、第一栅极1022、第二栅极1023、第一源极1024和第一漏极1025。信号传输层10还包括衬底101、第一栅极绝缘层103、第二栅极绝缘层104、第一层间绝缘层105和第二层间绝缘层106。

60.第一栅极绝缘层103设置在衬底101上。第一栅极1022设置在衬底101上,且第一连接端子a1和第一栅极1022同层且同材料。

61.第二栅极绝缘层104设置在第一栅极绝缘层103上。第二栅极绝缘层104覆盖第一栅极1022和第一连接端子a1。第二栅极1023和第二连接端子a2设置在第二栅极绝缘层104

上,第二栅极1023和第二连接端子a2同层且同材料。

62.第一层间绝缘层105设置在第二栅极绝缘层104上,且第一层间绝缘层105覆盖第二栅极1023和第二连接端子a2。第一过孔h1贯穿第一层间绝缘层105和第二栅极绝缘层104,第一信号连接段401通过第一过孔h1与第一连接端子a1连接。第四过孔h4贯穿第一层间绝缘层105,第四信号连接段501通过第四过孔h4与第二连接端子a2连接。

63.第一源极1024和第一漏极1025分别通过第一接触孔cnt1和第二接触孔cnt2和第一有源层1021连接。

64.第二层间绝缘层106设置在第一层间绝缘层105上,第二过孔h2贯穿第二层间绝缘层106。第二信号连接段402通过第二过孔h2和第一信号连接段401连接。第五过孔h5贯穿第二层间绝缘层106,第五信号连接段通过所述第五过孔和所述第四信号连接段连接。

65.需要说明的是,在本技术实施例中,栅极驱动电路102的薄膜晶体管可以是底栅型薄膜晶体管、顶栅型薄膜晶体管或双栅型薄膜晶体管,本技术以栅极驱动电路102为双栅型薄膜晶体管为示例进行说明,但不限于此。

66.在一些实施例中,第一有源层1021为低温多晶硅有源层,低温多晶硅(low temperature poly-silicon,ltps)技术是平板显示器领域中的又一新技术,继非晶硅(a-si)之后的下一代技术。低温多晶硅型的显示面板具有电子迁移率更快、薄膜电路面积更小、分辨率更高、功耗更低、稳定性更高等优点。

67.请结合图2和图4,图4为本技术实施例提供的显示功能层的一种结构示意图。像素驱动电路层20a包括基底层201、第二有源层202、第三栅极204绝缘层203、第三栅极204、层间介质层205、第二源极206、第二漏极207和平坦化层208。

68.其中,基底层201设置在第二层间绝缘层106远离第一层间绝缘层105的一面。第二有源层202设置在基底层201远离第二层间绝缘层106的一面,且第二有源层202于衬底101上的正投影位于遮光层108与衬底101上的正投影内。

69.绝缘层203设置在第二有源层202远离基底层201的一面。第六过孔h6贯穿绝缘层203和基底层201,第六信号连接段503通过第六过孔h6和第五信号连接段502连接。

70.第三栅极204设置在绝缘层203远离第二有源层202的一面。第三连接端子a3和第六信号连接段503连接且与第三栅极204同层且同材料。

71.层间介质层205设置在第三栅极204远离绝缘层203的一面。第三过孔h3贯穿层间介质层205、绝缘层203和基底层201,第三信号连接段403通过第三过孔h3和第二信号连接段402连接。

72.像素驱动电路层20a具有第三接触孔cnt3和第四接触孔cnt4。第三接触孔cnt3和第四接触孔cnt4贯穿层间介质层205。

73.第二源极206和第二漏极207设置在层间介质层205上,并分别通过第三接触孔cnt3和第四接触孔cnt4和第二有源层202连接。第四连接端子a4和第二源极206同层且材料,第四连接端子a4和第三信号连接段403连接。

74.平坦化层208设置在所述层间介质层205上,并覆盖第二源极206和第二漏极207。

75.在本技术实施例中,分别对不同的膜层进行打孔,使得在形成金属层的同时不同的过孔内形成对应的连接信号段,由多个信号连接段连接组成信号连接走线。即,本技术实施例的第一信号连接线40和第二信号连接线50均在形成显示面板100所需的金属走线的过

程中形成的,无需再引入额外的制程,降低了显示面板100的生产成本。

76.在一些实施例中,第二有源层202为金属氧化物有源层。其中,第二有源层202的材料可以选自铟镓锌氧化物。

77.金属氧化物半导体具有迁移率大、开态电流高、开关特性更优、均匀性更好的特点,可以适用于需要快速响应和较大电流的应用,如高频、高分辨率、大尺寸的显示器以及有机发光显示器等。

78.发光功能层20b包括阳极210、像素定义层209、发光层211和阴极212。其中,阳极210通过过孔与第二漏极207连接。像素定义层209具有开口,像素定义层209的开口暴露阳极210的表面。发光层211设置在像素定义层209的开口内。阴极212设置在发光层211远离阳极210的一面。

79.在一些实施例中,信号传输层10还包括遮光层108。遮光层108设置在第二层间绝缘层106远离第一层间绝缘层105的一面,且遮光层108通过过孔和第一漏极1025连接。遮光层108于衬底101上的正投影覆盖第二有源层202于衬底101上的正投影。在本技术实施例中,通过设置与第一漏极1025连接的遮光层108,遮光层108可以用于减小信号传输层10对显示功能层20的电磁干扰,且可以遮挡由衬底101一侧射入的外界光,提高显示面板100的稳定性。

80.在一些实施例中,显示面板100还包括第七过孔h7,第七过孔h7贯穿信号传输层10的部分绝缘层。信号传输层10还包括连接走线107和连接焊盘109,连接焊盘109设置在衬底101远离第一层间绝缘层105的一面。连接走线107设置在第七过孔h7内,连接走线h7的一端与连接焊盘109连接,连接走线107的另一端连接像素驱动电路层20a。

81.在一些实施例中,第七过孔h7贯穿第一层间绝缘层106、第二栅极绝缘层104、第一栅极绝缘层103和衬底101。

82.在一些实施例中,连接走线107用于将像素驱动电路层20a上的数据线接入连接焊盘109,但不限于此。

83.显示面板100还包括驱动芯片30。驱动芯片30设置连接焊盘109远离衬底101的一面。驱动芯片30用于驱动显示面板100发光。

84.在本技术实施例中,将驱动芯片30绑定于信号传输层10远离显示功能层20的一面,即将驱动芯片30绑定于背面,与现有技术通过弯折将驱动芯片绑定至显示面板的背面的设置方式相比,进一步减小了显示面板100的边框,提高了显示面板100的显示面的显示区aa的占比。

85.需要说明的是,在一些实施例中,连接焊盘109包括芯片连接焊盘和测试连接焊盘。本技术实施例不限定连接焊盘和测试连接焊盘的排列方式。

86.请继续参阅图1,栅极驱动电路102对应于显示区aa的外边缘。第一电源走线110设置在栅极驱动电路102的外侧。第二电源走线111设置在靠近连接焊盘109的一侧。复位信号走线113设置在栅极驱动电路102的内侧。阵列测试焊盘114设置在第二电源走线111远离连接焊盘109的一侧。扇形走线115设置在第二电源走线111和连接焊盘109之间,用于连接第二电源走线111和连接焊盘109。

87.在一些实施例中,衬底101包括依次层叠设置在的无机层1011、第一柔性衬底层、第一阻挡层1013和第二阻挡层1014。第一有源层1021设置在第二阻挡层1014上。连接焊盘

109设置在无机层1011远离第一柔性衬底层1012的一面。

88.在一些实施例中,第一柔性衬底层1012的材料可以包括pi(聚酰亚胺)、pet(聚二甲酸乙二醇酯)、pen(聚萘二甲酸乙二醇脂)、pc(聚碳酸酯)、pes(聚醚砜)、par(含有聚芳酯的芳族氟甲苯)或pco(多环烯烃)中的至少一种。无机层1011、第一阻挡层1013和第二阻挡层1014由含硅的氮化物、含硅的氧化物或含硅的氮氧化物中的一种或两种及以上的堆栈结构组成。

89.在一些实施例中,像素驱动电路层20a包括像素驱动电路,像素驱动电路可以包括3t1c型像素驱动电路、4t2c型像素驱动电路、5t2c型像素驱动电路或6t1c型像素驱动电路。

90.请参考图5,图5为本技术实施例提供的像素驱动电路层的一种像素驱动电路的电路图。像素驱动电路包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第一电容c1、第二电容c2、及有机发光二极管oled。各个晶体管均为p型薄膜晶体管。第一晶体管t1为驱动薄膜晶体管,第一晶体管t1的栅极经由第一节点(a)电性连接于第一电容(c1)的一端,第一晶体管t1的源极接入第二电源走线111的正电压。第一晶体管t1的漏极电性连接于有机发光二极管oled的阳极。第二晶体管t2的栅极接入该像素驱动电路所在行对应的第n条扫描信号scan(n),第二晶体管t2的源极接入数据信号data,第二晶体管t2的漏极经由第二节点b电性连接于第一电容c1的另一端。第三晶体管t3的栅极接入该像素驱动电路所在行的下一行对应的第n+1条扫描信号scan(n+1),第三晶体管t3的源极电性连接于第二节点b,漏极接入基准参考电压vref。第四晶体管t4的栅极接入该像素驱动电路所在行对应的第n条扫描信号scan(n),第四晶体管t4的源极电性连接于第一节点a,第四晶体管t4的漏极电性连接于有机发光二极管oled的阳极。

91.第一电容c1的一端电性连接于第一节点a,另一端电性连接于第二节b。第二电容c2的一端电性连接于第一节点a,另一端电性连接于第二电源走线111。有机发光二极管oled的阳极电性连接于第一晶体管t1的漏极和第四晶体管t4的漏极,阴极电性连接于第一电源走线110。

92.本发明提供的一种像素驱动电路采用4t2c结构,相比于现有的像素驱动电路,仅需要设置扫描信号来控制相应的薄膜晶体管,既起到了补偿作用,又减少了控制信号数量,且简化了电路结构,降低了成本。

93.相应的,本技术实施例还提供一种显示面板的制作方法,请参考图6。显示面板的制作方法包括以下步骤:

94.步骤b001,提供信号传输层,信号传输层位于显示面板的显示区。

95.其中,提供信号传输层的步骤包括提供一柔性衬底,然后在柔性衬底上设置连接焊盘109。

96.接下来,在柔性衬底1015上依次设置无机层1011、第一柔性衬底层1012。

97.随后,在第一柔性衬底层1012上设置栅极驱动电路102,以此形成信号传输层。

98.在一些实施例中,信号传输层还包括多条第一电源走线、多条第二电源走线、多条复位信号走线、阵列测试焊盘和多条扇形走线。

99.步骤b002,在信号传输层上设置显示功能层,显示功能层包括像素驱动电路层和发光功能层。像素驱动电路层设置在信号传输层上。发光功能层设置在像素驱动电路层远离信号传输层的一面。

100.步骤b003,利用激光剥离、机械剥离、溶解剥离等方法将柔性衬底1015剥离,以此裸露连接焊盘。

101.步骤b003,将驱动芯片绑定于连接焊盘上,以此完成显示面板的制作。

102.综上所述,虽然本技术已以优选实施例揭露如上,但上述优选实施例并非用以限制本技术,本领域的普通技术人员,在不脱离本技术的精神和范围内,均可作各种更动与润饰,因此本技术的保护范围以权利要求界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1