平面栅功率MOSFET抗单粒子烧毁器件及制备方法

平面栅功率mosfet抗单粒子烧毁器件及制备方法

技术领域

1.本发明涉及功率半导体器件抗辐射加固技术,具体地说是一种平面栅功率mosfet抗单粒子烧毁器件结构及制备方法。

背景技术:

2.功率半导体器件具有驱动电流大、击穿电压高、速度快、功耗低、输出功率大等优点,可实现不同范围内的功率控制和转换,广泛应用于消费电子、工业设备与航空航天领域,在空间应用领域具有巨大的开发潜力。功率半导体器件通常具有小尺寸及工作电压高的特点,其的工作稳定性容易受到空间自然辐射环境的影响,特别是单粒子烧毁(single event burnout,seb)效应的触发。seb通常由重离子辐射引发,当重离子垂直入射到关闭状态设备中时,沿入射轨迹会产生大量的电子-空穴对,同时内部存在强电场,使得空穴通过p-body区流向源极金属,电子流向漏极金属。空穴电流触发寄生双极结型晶体管(bipolar junction transistor,bjt),放大器件内部电流,因电流热效应产生更多的热量,并由于热击穿而导致seb。因此,应用于空间领域的功率半导体器件必须具有抗seb的能力。

3.自从seb发现以来,许多seb加固方法被广泛研究并提出。例如,在器件内部进行p

+

源区扩展、在n-漂移区和衬底之间引入缓冲层以及在漂移区引入少子寿命复合中心等方法,都可以有效地提高器件的抗seb能力,但同时也牺牲了器件的基本电学特性。例如,p

+

源区扩展的方法容易引起沟道区载流子浓度的减小,可使器件的正向导通电流密度降低;缓冲层的引入在降低衬底结峰值电场的同时也伴随着正向导通电阻的增加;少子寿命复合中心的引入一定会引起器件反向泄漏电流密度的增加,这将导致功耗的增大,不满足宇航用半导体器件对低功耗的要求。且目前针对功率半导体器件的抗单粒子烧毁加固结构主要集中在槽栅结构上,对于平面栅功率半导体器件的抗单粒子烧毁加固研究较少。

技术实现要素:

4.本发明针对现有半导体功率器件seb加固技术中的不足,提出了一种平面栅功率mosfet抗单粒子烧毁器件结构及制备方法。

5.一种平面栅功率mosfet抗单粒子烧毁器件结构,在半导体功率器件的颈区金属电极下方设有集成二极管;在源(阳)极区域刻蚀一个深沟槽并形成金属电极;n+源区与p-body区之间形成n型源极缓冲层。

6.作为优选,颈区金属电极下方的p型缓冲区域结深为1.2μm,宽度为0.6μm,掺杂2.0

×

10

17

cm-3

,p+区域结深为1.0μm,宽度为0.4μm,掺杂1.0

×

10

19

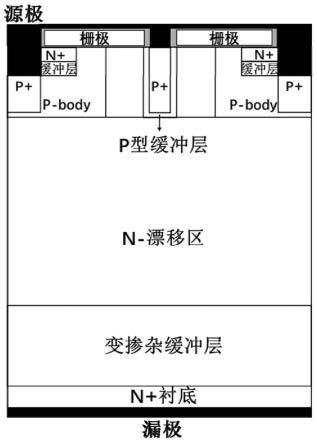

cm-3

。

7.作为优选,n+源极缓冲层的宽度为0.6μm,厚度为0.2μm,掺杂浓度为5.0

×

10

18

cm-3

。

8.作为优选,所述源(阳)极深沟槽刻蚀宽度为1.0μm,刻蚀深度为0.4μm。

9.本发明还提供了一种平面栅功率mosfet抗单粒子烧毁器件结构制备方法,包括:

10.步骤1、制备功率半导体器件衬底区域,在所述衬底区域多次重复外延从下到上依

次形成变掺杂缓冲层结构、n-漂移区与电流扩展层;

11.步骤2、在电流扩展层通过离子注入技术形成p-body区域与p型缓冲区域;

12.步骤3、在p-body区域通过离子注入技术形成高掺杂p型欧姆接触区域、高掺杂n+源区与源极缓冲层;

13.步骤4、利用刻蚀技术在源电极区域制造一个深沟槽并形成金属电极;

14.步骤5、利用热氧化技术生成栅氧化层并沉积多晶硅形成栅电极,组成平面栅功率mosfet抗单粒子烧毁器件结构。

15.本发明的优点在于:提出一种平面栅功率mosfet抗单粒子烧毁器件结构,该结构在颈区金属电极下方设有集成二极管、在源(阳)极区域刻蚀一个深沟槽并形成金属电极,增加了额外载流子流出器件的通道,大大提高了对重离子入射产生的电子-空穴对的吸收效率,使寄生bjt难以导通;同时n+源区与p-body区之间源极缓冲层的引入,可降低器件内部电流密度。从而降低因电流热效应而产生的热量,能够在不牺牲基础电学特性的前提下显著提高器件的抗单粒子烧毁能力。

附图说明

16.图1是带变掺杂缓冲层结构的平面栅功率mosfet器件结构示意图。

17.图2是基于本发明设计的平面栅功率mosfet抗单粒子烧毁器件结构示意图。

18.图3-7是图2所示结构中平面栅功率mosfet抗单粒子烧毁器件结构的制作流程示意图。

19.图8是图1所示结构的seb器件全局温度随时间变化曲线图。

20.图9是图2所示结构的seb器件全局温度随时间变化曲线图。

21.具体实现原理及仿真结果

22.为使本发明的目的、技术方案和优点更加清楚,以下结合附图对本发明进行具体阐述。

23.如图1、2所示,本发明提供一种平面栅功率mosfet抗单粒子烧毁器件结构,适用于平面栅功率mosfet器件,图2与图1不同之处在引入了集成二极管、源极缓冲层与深沟槽源极。具体地,在半导体功率器件的颈区金属电极下方设有集成二极管,在源(阳)极区域刻蚀一个深度为0.4μm的沟槽并形成金属电极,所述源(阳)电极刻蚀宽度为1.0μm;n+源区与p-body区之间形成n+源极缓冲层;所述的n+源极缓冲层的宽度为0.6μm,厚度为0.2μm,掺杂浓度为5.0

×

10

18

cm-3

。

24.颈区金属电极下方p型缓冲区域结深为1.2μm,宽度为0.6μm,掺杂2.0

×

10

17

cm-3

,p+区域结深为1.0μm,宽度为0.4μm,掺杂1.0

×

10

19

cm-3

。

25.本发明平面栅功率mosfet抗单粒子烧毁器件结构,该结构在颈区金属电极下方设有集成二极管、在源(阳)极区域刻蚀一个深沟槽并形成金属电极,增加了额外载流子流出器件的通道,大大提高了对重离子入射产生的电子-空穴对的吸收效率,使寄生bjt难以导通;同时n+源区与p-body区之间源极缓冲层的引入,可降低器件内部电流密度。从而降低因电流热效应而产生的热量,能够在不牺牲基础电学特性的前提下显著提高器件的抗单粒子烧毁能力。

26.本发明还提供了一种平面栅功率mosfet抗单粒子烧毁器件结构制备方法。

27.步骤1、制备功率半导体器件衬底区域,在所述衬底区域多次重复外延形成变掺杂缓冲层结构、漂移区与电流扩展层,如图3所示;

28.步骤2、通过离子注入技术形成p-body区域与p型缓冲区域,如图4所示;

29.步骤3、通过离子注入技术形成高掺杂p型欧姆接触区域与高掺杂n+源区与源极缓冲层,如图5所示;

30.步骤4、利用刻蚀技术在源(阳)电极区域制造一个深沟槽并形成金属电极,如图6所示;

31.步骤5、利用热氧化技术生成栅氧化层并沉积多晶硅形成栅电极,组成平面栅功率mosfet抗单粒子烧毁器件结构,如图7所示;

32.下面采用仿真验证方式对图1与图2所示两种结构进行对比讨论:

33.选用2000v平面栅功率mosfet器件。传统结构元胞宽度为9μm,厚度为24.5μm,漂移区掺杂浓度为3.5

×

10

15

cm-3

;对比结构元胞宽度为9μm,厚度为24.5μm,漂移区掺杂浓度为2.0

×

10

15

cm-3

。

34.入射离子线性能量转移值(linear energy transfer,let)为0.5pc/μm,入射轨迹选取为颈区上方(垂直入射且贯穿整个器件);入射离子产生的电荷密度为高斯分布:轨迹半径为0.05μm,电荷产生的初始时间为4

×

10-12

s,高斯函数的宽度为2

×

10-12

s。

35.根据图8所示仿真结论,当入射离子let值为0.5pc/μm,漏(阴)极电压为1400v,入射位置位于颈区上方且垂直于器件表面时,图1结构的seb器件全局温度最高超过4000k,并随着时间变化温度逐渐升高,远远高于sic的升华温度(2200k),器件发生热击穿。

36.根据图9所示仿真结论,当入射离子let值为0.5pc/μm,漏(阴)极电压为1400v,入射位置位于颈区上方且垂直于器件表面时,图2结构的seb器件全局温度最高可降低至2045k,不高于sic的升华温度(2200k),未发生热击穿。正是由于图2结构通过增加额外载流子流出器件的通道,大大提高了对重离子产生的电子-空穴对的吸收效率,使寄生bjt难以导通;同时n+源区与p-body区之间源极缓冲层的引入,可降低器件内部电流密度。从而降低因电流热效应而产生的热量,能够在不牺牲基础电学特性的前提下显著提高器件的抗单粒子烧毁能力。

37.显然,本领域的技术人员可以对本发明进行各种改动和变形而不脱离本发明的精神和范围。应注意到的是,以上所述仅为本发明的具体实施例,并不限制本发明,凡在本发明的精神和原则之内,所做的调制和优化,皆应属本发明权利要求的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1