一种功率器件的无引线封装结构及封装方法与流程

1.本发明主要涉及功率半导体封装工艺技术领域,具体涉及一种功率器件的无引线封装结构及封装方法。

背景技术:

2.随着功率器件的广泛运用以及迅速发展,其设计与制造趋于高频开关速率、高功率密度、高结温等要求发展,尤其是碳化硅材料的出现,相对于传统的硅基半导体芯片,碳化硅半导体芯片有着高结温(最高有望超过600℃),低导通电阻,高临界击穿场强,高开关频率等性能优势。然而目前由于封装技术受限,碳化硅半导体芯片大多数仍然采用传统的硅基功率半导体器件的封装形式,传统的硅基功率器件封装形式未能完全发挥碳化硅半导体芯片的优势。

3.传统功率器件封装工艺中芯片正面采用的是引线互连技术,通常采用铝线键合。由于铝线电阻率高、屈服强度低等材料本身的局限性,这种连接方式成为功率器件可靠性的短板;另外芯片尤其是碳化硅芯片正面的可连接面积有限,能键合的铝线根数受限,导致芯片的电流通量受限,未能完全发挥碳化硅芯片的优势,因此需要探索一种全新的连接方式。

技术实现要素:

4.本发明要解决的技术问题就在于:针对现有技术存在的问题,本发明提供一种通过金属构件代替铝键合、显著提高芯片通流能力的功率器件的无引线封装结构及封装方法。

5.为解决上述技术问题,本发明提出的技术方案为:

6.一种功率器件的无引线封装结构,包括芯片、金属构件和衬板,所述芯片的背面连接在所述衬板上,所述金属构件的一端与芯片的正面之间通过烧结工艺连接,所述金属构件的另一端与衬板或外部端子之间通过烧结工艺连接。

7.作为上述技术方案的进一步改进:

8.所述金属构件为铜或者cumo30合金制成。

9.所述金属构件呈п型,其中п型金属构件底面的一端与芯片的正面连接,п型金属构件底面的另一端与衬板连接。

10.所述金属构件的一端与芯片的正面之间通过银烧结工艺连接,所述金属构件的另一端与衬板之间通过银烧结工艺连接。

11.所述金属构件的一端和另一端的连接面上设置有nipdau层,所述nipdau层上设有一层银膏。

12.所述芯片为碳化硅芯片。

13.本发明还公开了一种如上所述的功率器件的无引线封装结构的封装方法,包括步骤:

14.在金属构件的两个连接面镀nipdau层,然后在nipdau层上均匀预敷一层银膏;

15.将芯片的背面与衬板连接;

16.将金属构件的两个连接面分别贴在芯片正面与衬板上,在预设温度和预设压力的作用下,将芯片正面与金属构件连接面,以及衬板与金属构件连接面之间进行烧结,形成一层银烧结层,完成金属构件与芯片正面,以及金属构件与衬板之间的连接。

17.作为上述技术方案的进一步改进:

18.将芯片的背面与衬板连接的具体过程为:在加热加压的情况下将芯片背面沾银膜,贴于衬板上,然后在一定压力与温度的条件下进行烧结,实现芯片背面与衬板之间的连接。

19.在芯片的门极和源极信号需要外延时,通过引线将芯片的门极和源极分别与衬板连接。

20.所述引线为铝线。

21.与现有技术相比,本发明的优点在于:

22.本发明采用金属构件来代替铝线键合,实现半导体芯片正面到衬板或者外部端子之间的电性连接,达到无引线连接效果,能显著提高芯片的通流能力,极大的发挥碳化硅芯片的优势;另外金属构件的结构强度、电阻率和导热性等都远高于铝线,能避免产生铝线的工艺缺陷和可靠性问题。

23.本发明的半导体芯片与金属构件之间的连接,以及金属构件与衬板或者外部端子之间的连接均采用银烧结的方式,银烧结材料具有更高的热导率、电导率、机械强度和接近纯银的熔点,能显著提高功率器件的可靠性,是当前最具应用前景的互连技术。

附图说明

24.图1为本发明中的金属构件在实施例的主视结构图。

25.图2为本发明中金属构件的连接面在实施例的结构图。

26.图3为本发明中的金属构件在实施例的立体结构图。

27.图4为本发明的封装结构在实施例的主视结构图。

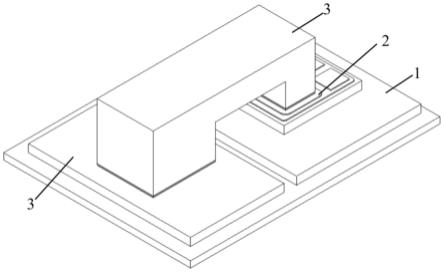

28.图5为本发明的封装结构在实施例的立体结构图。

29.图6为本发明的单面散热模块在实施例的立体结构图。

30.图7为本发明的芯片在实施例的主视结构图。

31.图例说明:1、衬板;2、芯片;201、门极;202、源极;203、漏极;3、金属构件;301、nipdau层;302、银膏;4、铝线。

具体实施方式

32.以下结合说明书附图和具体实施例对本发明作进一步描述。

33.如图4和图5所示,本发明实施例提供了一种功率器件的无引线封装结构,包括芯片2(如碳化硅芯片)、金属构件3和衬板1,芯片2的背面连接在衬板1上,金属构件3的一端与芯片2的正面之间通过烧结工艺(如银烧结)连接,金属构件3的另一端与衬板1或外部端子之间通过烧结工艺(如银烧结)连接。

34.本发明的无引线封装结构,采用金属构件3来代替铝线键合,实现半导体芯片2正

面到衬板1或者外部端子之间的电性连接,达到无引线连接效果,能显著提高芯片2的通流能力,极大的发挥碳化硅芯片2的优势;另外金属构件3的结构强度、电阻率和导热性等都远高于铝线,能避免产生铝线的工艺缺陷和可靠性问题。

35.本发明的半导体芯片2与金属构件3之间的连接,以及金属构件3与衬板1或者外部端子之间的连接均采用银烧结的方式,由于银烧结材料具有更高的热导率、电导率、机械强度和接近纯银的熔点,能显著提高功率器件的可靠性,是当前最具应用前景的互连技术。

36.考虑通流能力、cte与芯片2和衬板1的匹配原则,以及工艺过程的要求等,这种金属构件3的材料可以是纯铜或者cumo30合金,金属构件3的连接面需提前电镀或化学镀nipdau层301,然后均匀预敷一层银膏302,此银膏302为可烧结材料,包含微纳米级别银颗粒;再使用烧结设备使芯片2正面与金属构件3,以及金属构件3与衬板1或者外部端子之间形成一层导电导热的银烧结层。其中金属构件3呈п型,如图1~3所示,п型金属构件3底面的两端形成连接面,分别与芯片2正面和衬板1(或外部端子)连接。

37.本发明实施例还公开了一种如上所述的功率器件的无引线封装结构的封装方法,包括步骤:

38.在金属构件3的两个连接面镀一层nipdau,然后均匀预敷一层银膏302;

39.将芯片2的背面与衬板1连接;

40.将金属构件3的两个连接面分别贴在芯片2正面与衬板1上,在预设温度和预设压力的作用下,将芯片2正面与金属构件3连接面,以及衬板1与金属构件3连接面之间进行烧结,形成一层银烧结层,完成金属构件3与芯片2正面,以及金属构件3与衬板1之间的连接。

41.本发明的封装方法操作简便且易于实现。

42.在一具体实施例中,将芯片2的背面与衬板1连接的具体过程为:在加热加压的情况下将芯片2背面沾银膜,贴于衬板1上,然后在一定压力与温度的条件下进行烧结,实现芯片2背面与衬板1之间的连接。

43.下面结合一完整的具体实施例来对本发明作进一步详细说明:

44.以单面散热模块为实施例进行说明,如图6所示,模块的上下桥分别有三个sic mos芯片2,其中采用cumo30合金为金属构件3的材料;芯片2上的门极201、源极202和漏极203的分布如图7所示。

45.第一阶段实现芯片2背面漏极203与衬板1之间的连接,在加热加压的情况下使用贴片设备将六个芯片2的背面沾银膜,贴于衬板1上,然后使用烧结设备在一定压力与温度的条件下实现六个芯片2背面与衬板1之间的连接;当然,也可以通过其它方式实现芯片2背面与衬板1之间的连接;

46.第二阶段实现金属构件3与芯片2正面源极202,以及金属构件3与衬板1之间的连接,贴片头加热吸取金属构件3,在一定压力作用下放置在指定位置,使金属构件3的一端连接在芯片2正面源极202区域,一端连接在衬板1上,然后使用烧结设备在一定压力与温度的条件下使金属构件3的两个连接面形成一层烧结层,实现金属构件3与芯片2正面源极202,以及金属构件3与衬板1之间的连接。考虑到mos芯片2需要将门极201与源极202信号外延,使用键合设备用铝线4将芯片2的门极201和源极202与衬板1连接。

47.如本公开和权利要求书中所示,除非上下文明确提示例外情形,“一”、“一个”、“一种”和/或“该”等词并非特指单数,也可包括复数。本公开中使用的“第一”、“第二”以及类似

的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。

48.以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1