一种电压匹配的空间用多结太阳电池及其制备方法和应用与流程

1.本发明涉及半导体相关技术领域,尤其是涉及一种电压匹配的空间用多结太阳电池及其制备方法和应用。

背景技术:

2.空间用太阳电池的制备不仅依赖于生长技术(例如:金属有机物化学气相外延沉积,分子数外延生长等),而且受半导体材料自身一些物理特性的限制(例如晶格常数和禁带宽度等)。因此多结空间太阳电池的结构相对固定。从生长结构而言都是堆叠生长结构,即各子电池按照禁带宽度从大到小自上而下依次排列;从工作的电路结构来讲,都是串联结构,即子电池之间用隧道结连接形成串联电路,为了减少能量损失,该结构需要满足电流匹配。

3.串联的电路结构虽然利于生产,但一定程度上限制了空间电池各个子电池的晶格匹配程度和子电池吸收光谱范围。

4.综上所述,需要开发一种光谱吸收范围广的空间用多结太阳电池。

技术实现要素:

5.本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种电压匹配的空间用多结太阳电池,该空间用多结太阳电池的光谱吸收范围广。

6.本发明还提供了上述空间用多结太阳电池的制备方法。

7.本发明还提供了上述空间用多结太阳电池的应用。

8.根据本发明的第一方面提供了一种电压匹配的空间用多结太阳电池,

9.包括依次叠加的:

10.底电池、中电池、栅线和顶电池;

11.所述栅线连接有负极;

12.所述顶电池和底电池上设有正极;

13.所述底电池和中电池串联后与所述顶电池并联。

14.根据本发明空间用多结太阳电池技术方案中的一种技术方案,至少具备如下有益效果:

15.(1)本发明使用并联电路来构建空间用多结太阳电池,可使串联电路中不能匹配的材料满足电流电压匹配条件,空间用多结太阳电池的底电池和中电池为串联,底电池和中电池形成的串联电路和顶电池构成并联电路。具体的:

16.若电池采用并联的工作电路,将需要重新考虑电池的电流匹配和晶格匹配外,此外还需要考虑电压匹配。其中电流的匹配可通过厚度调整,也可通过减反膜的反射光波段调整,调整方法较为多样、简单。但是电压匹配的调整方法较难。

17.由此可知,一些在串联电路中不可能匹配的材料(主要是电压不匹配),将有机会在并联电路(或者混连电路)中满足匹配条件(即满足电流电压匹配)。

18.进一步的可知,本发明通过修改空间用多结太阳电池的工作电路,可以使更多的材料能够满足电池的工作条件(满足电流电压匹配),有效扩充了空间用多结太阳电池的材料库,为创造更高转化效率的电池结构提供了选择方案;也为了选择光谱吸收范围更广的子电池材料提供了思路。

19.(2)本发明为串联电路电池的表面栅线制备在电池内部提供了基础,如此可减低表面栅线对入射光的遮挡,能更加有效的利用光;

20.本发明中底电池、中电池、栅线和顶电池构成了发射区-栅线-发射区的结构;

21.传统技术中,栅线设置在太阳电池上表面,且不透光,因此会遮挡太阳电池接收的太阳光;本发明将栅线埋在中电池和顶之间,这样可以有效增加进入电池的光通量以增加电池的效率。

22.根据本发明的一些实施方式,所述底电池包括ge电池。

23.可以理解的是,所述ge电池包括依次叠加的ge基区、gainp缓冲层和gainp发射区。

24.根据本发明的一些实施方式,所述ge基区的厚度约为140μm。

25.根据本发明的一些实施方式,所述ge基区为p型半导体;可以理解的是,没有进行额外的掺杂。

26.根据本发明的一些实施方式,所述gainp缓冲层为n型半导体。

27.根据本发明的一些实施方式,所述gainp缓冲层为si掺杂gainp缓冲层。

28.根据本发明的一些实施方式,所述si掺杂gainp缓冲层中si掺杂的浓度为5

×

10

17

~9

×

10

17

/cm。

29.根据本发明的一些实施方式,所述gainp缓冲层厚度为5nm~20nm。

30.根据本发明的一些实施方式,所述底电池中,gainp发射区为n型半导体。

31.根据本发明的一些实施方式,所述底电池中,gainp发射区为si掺杂gainp发射区。

32.根据本发明的一些实施方式,所述si掺杂底电池中,gainp发射区中si掺杂的浓度为5

×

10

17

~9

×

10

17

/cm。

33.根据本发明的一些实施方式,所述底电池中,gainp发射区的厚度为450nm~650nm。

34.根据本发明的一些实施方式,所述底电池的带隙为0.4ev~0.8ev。

35.根据本发明的一些优选的实施方式,所述底电池的带隙约为0.66ev。

36.带隙的选择可影响各子电池吸收光的份额,此外在本发明中,带隙的选择还影响所得空间用多结太阳电池是否满足电流匹配和电压匹配,以免电流在所得空间用多结太阳电池内部消耗。所述中电池和顶电池的带隙选择原因也是如此。

37.根据本发明的一些实施方式,所述底电池和中电池之间设有隧道结。

38.可以理解的是,所述隧道结包括自所述底电池始依次叠加的gaas层和algaas层。

39.根据本发明的一些实施方式,所述gaas层为n

++

型半导体。

40.根据本发明的一些实施方式,所述gaas层为te掺杂gaas层。

41.根据本发明的一些实施方式,所述te掺杂gaas层中te掺杂的浓度为1

×

10

19

~5

×

10

19

/cm。

42.根据本发明的一些实施方式,所述gaas层的厚度为5nm~15nm。

43.根据本发明的一些实施方式,所述algaas层为p

++

型半导体。

44.根据本发明的一些实施方式,所述algaas层为c掺杂algaas层。

45.根据本发明的一些实施方式,所述c掺杂algaas层中c掺杂的浓度为1

×

10

19

~5

×

10

19

/cm。

46.根据本发明的一些实施方式,所述algaas层的厚度为2nm~10nm。

47.根据本发明的一些实施方式,所述中电池包括gainp背场、gainas基区、中电池gainp发射区和中电池alinp窗口层。

48.根据本发明的一些实施方式,所述gainp背场为p

+

型半导体。

49.根据本发明的一些实施方式,所述gainp背场为zn掺杂gainp背电场。

50.根据本发明的一些实施方式,所述zn掺杂gainp背场中zn掺杂的浓度为1

×

10

18

~3

×

10

18

/cm。

51.根据本发明的一些实施方式,所述gainp背场的厚度为100nm~200nm。

52.根据本发明的一些实施方式,所述gainas基区为p型半导体。

53.根据本发明的一些实施方式,所述gainas基区为zn掺杂gainas基区。

54.根据本发明的一些实施方式,所述zn掺杂gainas基区中zn掺杂的浓度为5

×

10

16

~9

×

10

16

/cm。

55.根据本发明的一些实施方式,所述gainas基区的厚度为1000nm~2500nm。

56.根据本发明的一些实施方式,所述中电池gainp发射区为n型半导体。

57.根据本发明的一些实施方式,所述中电池gainp发射区为si掺杂中电池gainp发射区。

58.根据本发明的一些实施方式,所述si掺杂中电池gainp发射区中si掺杂的浓度为5

×

10

17

~9

×

10

17

/cm。

59.根据本发明的一些实施方式,所述中电池gainp发射区的厚度为500nm~1000nm。

60.根据本发明的一些实施方式,所述中电池alinp窗口层为n

+

型半导体。

61.根据本发明的一些实施方式,所述中电池alinp窗口层为si掺杂中电池alinp窗口层。

62.根据本发明的一些实施方式,所述si掺杂中电池alinp窗口层中si掺杂的浓度为1

×

10

18

~5

×

10

18

/cm。

63.根据本发明的一些实施方式,所述中电池alinp窗口层的厚度为30nm~50nm。

64.根据本发明的一些实施方式,所述中电池远离所述底电池一侧表面还设有中电池接触层。

65.可以理解的是,所述中电池接触层的材质包括gaas。

66.根据本发明的一些实施方式,所述中电池接触层为n

+

型半导体。

67.根据本发明的一些实施方式,所述中电池接触层为si掺杂中电池接触层。

68.根据本发明的一些实施方式,所述si掺杂中电池接触层中si掺杂的浓度为1

×

10

18

~5

×

10

18

/cm。

69.根据本发明的一些实施方式,所述中电池接触层的厚度为100nm~500nm。

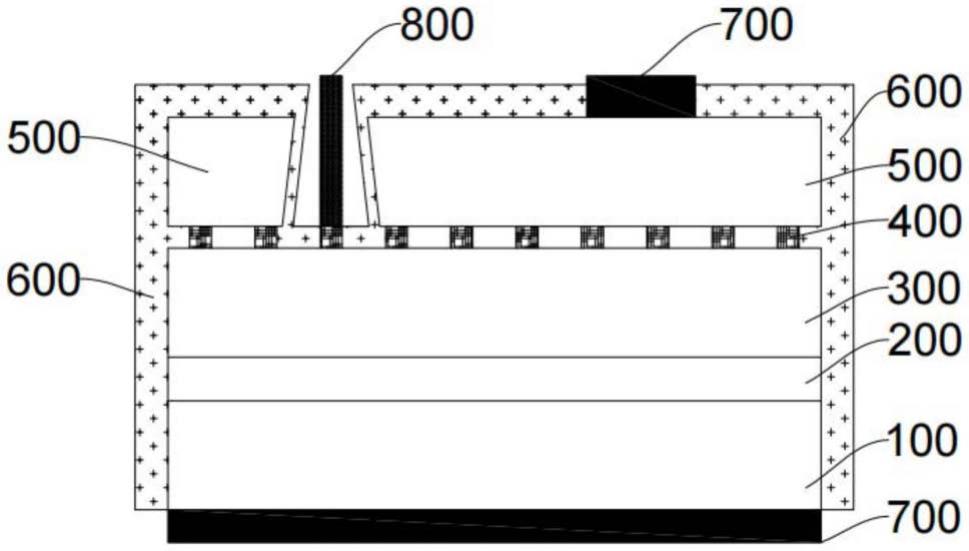

70.根据本发明的一些实施方式,所述中电池的带隙为1.2ev~1.6ev。

71.根据本发明的一些优选的实施方式,所述中电池的带隙约为1.45ev。

72.根据本发明的一些实施方式,所述栅线的厚度为1μm~200μm。

73.根据本发明的一些实施方式,所述栅线的宽度为1μm~200μm。

74.由此可知,所述栅线并未完全占据所述中电池表面。

75.根据本发明的一些实施方式,所述栅线的材质包括augeni、ag和au中的至少一种。

76.根据本发明的一些实施方式,所述栅线包括依次叠加的augeni层、ag层、au层、ag层和augeni层。

77.根据本发明的一些实施方式,所述顶电池包括自所述栅线开始,依次叠加的algainp背场层、ga

0.65

in

0.35

p基区、ga

0.65

in

0.35

p本征层、ga

0.65

in

0.35

p发射区和alinp窗口层。

78.根据本发明的一些实施方式,所述algainp背场层为p

+

型半导体。

79.根据本发明的一些实施方式,所述algainp背场层为zn掺杂algainp背场层。

80.根据本发明的一些实施方式,所述zn掺杂algainp背场层中zn掺杂的浓度为1

×

10

18

~3

×

10

18

/cm。

81.根据本发明的一些实施方式,所述algainp背场层的厚度为40nm~100nm。

82.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p基区为p型半导体。

83.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p基区为zn掺杂ga

0.65

in

0.35

p基区。

84.根据本发明的一些实施方式,所述zn掺杂ga

0.65

in

0.35

p基区中zn掺杂的浓度为5

×

10

16

~9

×

10

16

/cm。

85.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p基区的厚度为300nm~500nm。

86.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p本征层为i型半导体。

87.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p本征层的厚度为400nm~600nm。

88.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p发射区为n型半导体。

89.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p发射区为c掺杂ga

0.65

in

0.35

p发射区。

90.根据本发明的一些实施方式,所述c掺杂ga

0.65

in

0.35

p发射区中c掺杂的浓度为5

×

10

17

~9

×

10

17

/cm。

91.根据本发明的一些实施方式,所述ga

0.65

in

0.35

p发射区的厚度为70nm~120nm。

92.根据本发明的一些实施方式,所述顶电池中,alinp窗口层为n

+

型半导体。

93.根据本发明的一些实施方式,所述顶电池中,alinp窗口层为c掺杂alinp窗口层。

94.根据本发明的一些实施方式,所述c掺杂alinp窗口层中c的掺杂浓度为1

×

10

18

~5

×

10

18

/cm。

95.根据本发明的一些实施方式,所述顶电池中,alinp窗口层的厚度为20nm~30nm。

96.根据本发明的一些实施方式,所述顶电池的带隙为1.8ev~2.2ev。

97.根据本发明的一些实施方式,所述顶电池的带隙约为2.15ev。

98.根据本发明的一些实施方式,所述负极的厚度为1000nm~3000nm。

99.根据本发明的一些实施方式,所述负极为自所述栅线开始依次叠加的au层、ag层和au层。

100.根据本发明的一些实施方式,所述正极的厚度为1000nm~2000nm。

101.根据本发明的一些实施方式,所述正极为依次叠加的au层、ag层和au层。

102.可以理解的是,为避免所述顶电池上设置的正极影响光的透过,设于所述顶电池上的正极尺寸小于设于所述底电池上的正极。

103.根据本发明的一些实施方式,所述顶电池中设有通孔,所述负极穿过所述通孔与所述栅线相连。

104.根据本发明的一些实施方式,所述空间用多结太阳电池还包括绝缘层。

105.根据本发明的一些实施方式,所述绝缘层设于所述空间用多结太阳电池表面,所述正极和负极之外的位置。

106.根据本发明的一些实施方式,所述绝缘层的材质包括二氧化硅和氮化硅中的至少一种。

107.根据本发明的一些实施方式,所述绝缘层的厚度为100nm~1000nm。

108.根据本发明的一些实施方式,所述空间用多结太阳电池还包括外部线路。

109.所述外部线路连通设于所述底电池和顶电池上的正极。

110.所述外部线路连通设于所述顶电池上的正极和所述负极。

111.本发明第二方面提供了上述空间用多结太阳电池的制备方法,包括以下步骤:

112.s1、制备依次叠加的所述底电池、中电池和栅线,得外延片;

113.在临时衬底上生长所述顶电池;

114.s2、将所述外延片,所述栅线所在一侧表面和所述顶电池键合;

115.s3、将所述栅线和所述负极连接;

116.分别在所述顶电池和底电池上形成所述正极;

117.s4、连接外电路,形成所述底电池和中电池串联后与所述顶电池并联的连接方式。

118.根据本发明的一些实施方式,所述栅线的制备方法,包括以下步骤:涂胶、曝光、蒸镀和去胶。

119.可以理解的,所述栅线的蒸镀时长为5~7h;

120.进一步可以理解的是,所述栅线的蒸镀过程中,蒸镀腔室的温度约为100℃;

121.进一步可以理解的是,所述栅线的蒸镀方式包括电子束蒸镀;

122.进一步可以理解的是,所述栅线的制备过程汇总,涂胶和曝光的作用相当于形成了所述蒸镀的掩模。

123.根据本发明的一些实施方式,步骤s1中,所述顶电池生长之前,还包括在所述临时衬底上依次生长缓冲层、刻蚀层和接触层,之后在所述刻蚀层表面生长所述顶电池,所述顶电池的gaas接触层与所述刻蚀层接触。

124.根据本发明的一些实施方式,所述临时衬底的材质包括gaas。

125.根据本发明的一些实施方式,所述临时衬底未进行掺杂,为i型半导体。

126.根据本发明的一些实施方式,所述临时衬底厚度约为625μm。

127.根据本发明的一些实施方式,所述缓冲层的材质为gaas。

128.根据本发明的一些实施方式,所述缓冲层未进行掺杂,为i型半导体。

129.根据本发明的一些实施方式,所述缓冲层的厚度为250-350nm。

130.根据本发明的一些实施方式,所述刻蚀层的材质为alas。

131.根据本发明的一些实施方式,所述刻蚀层未进行掺杂,为i型半导体。

132.根据本发明的一些实施方式,所述刻蚀层的厚度为5~15nm。

133.根据本发明的一些实施方式,和所述刻蚀层相邻的接触层材质为gaas;

134.可以理解的是所述接触层为n+型半导体,其中掺杂了浓度为1

×

10

18

~5

×

10

18

/cm

的c。

135.根据本发明的一些实施方式,所述制备方法还包括去除所述临时衬底。

136.根据本发明的一些实施方式,所述临时衬底的去除时机为步骤s1中,所述顶电池生长完成后。

137.根据本发明的一些实施方式,所述临时衬底的去除时机为步骤s2中,所述键合完成后。

138.根据本发明的一些实施方式,所述临时衬底的去除,方法包括刻蚀所述刻蚀层。

139.可以理解的是,所述刻蚀为干法刻蚀或湿法刻蚀。

140.根据本发明的一些实施方式,步骤s2中,所述键合的温度约为500℃。

141.根据本发明的一些实施方式,步骤s3中,所述制备方法还包括在步骤s2和步骤s3之间,在所述顶电池上形成通孔。

142.根据本发明的一些实施方式,所述通孔的制备方法包括刻蚀。

143.可以理解的是,所述刻蚀为干法刻蚀或湿法刻蚀。

144.根据本发明的一些实施方式,所述制备方法还包括在步骤s2和步骤s3之间设置所述绝缘层。

145.可以理解的是,所述绝缘层的设置在所述通孔形成之后。

146.根据本发明的一些实施方式,所述绝缘层的制备方法为蒸镀。

147.根据本发明的一些实施方式,所述绝缘层的制备方法为化学气相沉积。

148.若无其他特殊说明,本发明中,所述空间用多结太阳电池的各结构均采用mocvd法制备而成。

149.本发明第三方面提供了上述空间用多结太阳电池在空间飞行器中的应用。

150.根据本发明的一些实施方式,所述空间飞行器包括人造地球卫星、空间探测器和载人航天器中的至少一种。

151.若无其他说明,本发明中的“约”表示允许误差范围在

±

2%之间,例如约100表示的含义是100

±

2%

×

100,即98~102。

152.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

附图说明

153.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

154.图1为本发明实施例1所得空间用多结太阳电池的结构示意图;

155.图2为本发明实施例1所得空间用多结太阳电池和外部线路的结构示意图;

156.图3为本发明实施例1所得空间用多结太阳电池形成的电路示意图;

157.图4为本发明实施例2步骤d1所得外延片的结构示意图;

158.图5为本发明实施例2步骤d2所得部件的结构示意图。

159.附图标记:

160.100、底电池;110、ge基区;120、gainp缓冲层;130、gainp发射区;

161.200、隧道结;

162.300、中电池;310、gainp背场;320、gainas基区;330、中电池gainp发射区;340、中电池alinp窗口层;350、中电池接触层;

163.400、栅线;

164.500、顶电池;550、algainp背场层;560、ga

0.65

in

0.35

p基区;570、ga

0.65

in

0.35

p本征层;580、ga

0.65

in

0.35

p发射区;590、alinp窗口层;

165.510、临时衬底;520、缓冲层;530、刻蚀层;540、接触层;

166.600、绝缘层;

167.700、正极;

168.800、负极;

169.900、外部线路。

具体实施方式

170.以下将结合实施例对本发明的构思及产生的技术效果进行清楚、完整地描述,以充分地理解本发明的目的、特征和效果。显然,所描述的实施例只是本发明的一部分实施例,而不是全部实施例,基于本发明的实施例,本领域的技术人员在不付出创造性劳动的前提下所获得的其他实施例,均属于本发明保护的范围。

171.本发明的描述中,参考术语“一个实施例”、“一些实施例”、“示意性实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

172.实施例中未注明具体条件者,按照常规条件或制造商建议的条件进行。所用试剂或仪器未注明生产厂商者,均为可以通过市售购买获得的常规产品。

173.下面详细描述本发明的具体实施例。

174.实施例1

175.本实施例提供了一种空间用多结太阳电池,具体由以下部件组成:

176.依次叠加底电池100、隧道结200、中电池300、栅线400和顶电池500;

177.其中顶电池500中设有通孔(图中未标注),暴露出栅线400;

178.在通孔中,设有负极800,负极800和栅线400连通;

179.顶电池500和底电池100上分别设有正极700,两处正极700之间由外部线路900连通;

180.设于顶电池500上的正极700和负极800经由外部线路900连通。

181.具体结构示意图如图1~2所示,各子电池之间的串并联关系如图3所示。

182.可以理解的是,底电池100的带隙宽度约为0.66ev,由依次叠加的ge基区110、gainp缓冲层120和gainp发射区130组成;

183.进一步可以理解的是:

184.ge基区110为未进行掺杂的p型半导体,厚度约为140μm;

185.gainp缓冲层120为si掺杂浓度为5

×

10

17

~9

×

10

17

/cm的n型半导体,厚度为5nm~20nm;

186.gainp发射区130为si掺杂为5

×

10

17

~9

×

10

17

/cm的n型半导体,厚度为450nm~650nm。

187.可以理解的是,隧道结200由自底电池100而始依次叠加的gaas层和algaas层组成(图中未示出);

188.进一步可以理解的是:

189.gaas层为te掺杂为1

×

10

19

~5

×

10

19

/cm的n

++

型半导体,厚度为5nm~15nm;

190.algaas层为c掺杂的浓度为1

×

10

19

~5

×

10

19

/cm的p

++

型半导体,厚度为2nm~10nm。

191.可以理解的是,中电池300的带隙为1.45ev,由自隧道结200而始依次叠加的gainp背场310、gainas基区320、中电池gainp发射区330和、中电池alinp窗口层340和中电池接触层350组成;

192.进一步可以理解的是:

193.gainp背场310为zn掺杂的浓度为1

×

10

18

~3

×

10

18

/cm的p

+

型半导体,厚度为100nm~200nm;

194.gainas基区320为zn掺杂的浓度为5

×

10

16

~9

×

10

16

/cm的p型半导体,厚度为1000nm~2500nm;

195.中电池gainp发射区330为si掺杂的浓度为5

×

10

17

~9

×

10

17

/cm的n型半导体,厚度为500nm~1000nm;

196.中电池alinp窗口层340为si掺杂的浓度为1

×

10

18

~5

×

10

18

/cm的n

+

型半导体,厚度为30nm~50nm;

197.中电池接触层350为si掺杂的浓度为1

×

10

18

~5

×

10

18

/cm的n

+

型半导体,厚度为100nm~500nm,材质为gaas。

198.可以理解的是,栅线400间隔设于中电池300远离底电池100一侧表面,每个栅线400的厚度为1μm~200μm,宽度为1μm~200μm,由依次叠加的augeni层、ag层、au层、ag层和augeni层组成。

199.可以理解的是,顶电池500的带隙约为2.15ev,由自栅线400而始依次叠加的algainp背场层550、ga

0.65

in

0.35

p基区560、ga

0.65

in

0.35

p本征层570、ga

0.65

in

0.35

p发射区580和alinp窗口层590组成。

200.进一步可以理解的是:

201.algainp背场层550为zn掺杂的浓度为1

×

10

18

~3

×

10

18

/cm的p

+

型半导体,厚度为40nm~100nm;

202.ga

0.65

in

0.35

p基区560为zn掺杂的浓度为5

×

10

16

~9

×

10

16

/cm的p型半导体,厚度为300nm~500nm。

203.ga

0.65

in

0.35

p本征层570为i型半导体,厚度为400nm~600nm;

204.ga

0.65

in

0.35

p发射区580为c掺杂的浓度为5

×

10

17

~9

×

10

17

/cm的n型半导体,厚度为70nm~120nm;

205.alinp窗口层590为c的掺杂浓度为1

×

10

18

~5

×

10

18

/cm的n

+

型半导体,厚度为20nm~30nm。

206.可以理解的是,正极700为依次叠加的au层、ag层和au层(图中未示出),厚度为

1000nm~2000nm;

207.可以理解的是,负极800为依次叠加的au层、ag层和au层(图中未示出),厚度为1000nm~3000nm。

208.可以理解的是,本实施例提供的空间用多结太阳电池还包括绝缘层600,其中绝缘层600设于空间用多结太阳电池表面,除正极700和负极800之外的位置,进一步的,绝缘层的材质选自二氧化硅,厚度为100nm~1000nm。

209.本实施例中,各子电池之间的电压和晶格匹配程度较差,本实施例通过利用串并联电路,很好的规避了该问题,也重新分配了顶电池可吸收的光谱范围。且在该模型中不会出现中电池限制顶电池电流的问题。

210.实施例2

211.本实施例提供了实施例1中空间用多结太阳电池的制备方法,具体步骤为:

212.d1.在mocvd中依次生长底电池100、隧道结200、中电池300和栅线400,形成的外延片结构如图4所示;

213.在mocvd中,以厚度约为625μm的i型gaas作为临时衬底510,在其上依次生长厚度为250-350nm的i型gaas作为缓冲层520、厚度为5~15nm的i型alas为刻蚀层530、c掺杂浓度为1

×

10

18

~5

×

10

18

/cm的n+型gaas作为接触层540,以及顶电池500;其中顶电池500中alinp窗口层590与接触层540接触;

214.d2.将步骤d1所得外延片和包括顶电池500的部件进行键合,具体的是将外延片中栅线400所在一侧表面和顶电池500进行键合(键合温度约为500℃);键合后所得部件的结构示意图如图5所示;

215.d3.刻蚀步骤d2所得部件,具体方法为湿法刻蚀或干法刻蚀,刻蚀位置为刻蚀层530和接触层540,以使顶电池500和临时衬底510之间脱离;

216.d4.在步骤d1所得部件顶电池500表面涂覆光刻胶,显影后露出通孔所在区域,并进行蚀刻(干法或湿法),以形成通孔;

217.d5.将步骤d4所得部件去胶后,再次涂覆光刻胶,显影后覆盖正极700和负极800所在位置,并暴露其他位置;之后蒸镀绝缘层600;

218.d6.对步骤d5所得部件进行去胶后,蒸镀形成正极700和负极800。

219.若有需要还可以外部线路900对底电池100、中电池300和顶电池500进行连接,形成底电池100和中电池300串联后与顶电池500并联的连接结构。

220.顶电池algainp背场层550和中电池接触层350之间的晶格常数相差比较大,本身很难通过grade buffer来直接生长获得整体外延电池。本实施例采用分别生长外延片和顶电池500后再键合的方法,加之结构调整,成功制备得到了空间用多结太阳电池。拓宽了空间用多结太阳电池的材料选择范围。

221.上面结合具体实施方式对本发明实施例作了详细说明,但是本发明不限于上述实施例,在所属技术领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下作出各种变化。此外,在不冲突的情况下,本发明的实施例及实施例中的特征可以相互组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1