滤波电感模块的制作方法

1.本发明涉及电力电子技术领域,具体而言,涉及一种滤波电感模块,以在空间小且具emc需求的条件下,提高空间利用率,减小滤波电感间的近场干扰,同时简化装配制造过程并降低成本。

背景技术:

2.现代电力电子装置作为电力转换的重要组成部分,广泛应用于电力、电子、电机和能源行业。随着快充技术的高速发展,电源模块的体积越来越小,对各组件布局的要求也越来越高。由于电源模块对电磁相容性(electromagnetic compatibility,emc)有特定的要求,滤波器的部分便属不可或缺的组件,其往往会占用比较多的系统体积。因此合理设计滤波器的布局便成为电源模块小型化并提高功率密度的关键。

3.以传统的电源适配器为例,其构成组件中包含有至少两组滤波电感,分别架构于两个独立的线架(bobbin)上。当架构于线架上的至少两组滤波电感再架构于pcb而电连接至电源适配器的其他组件时,往往会占用掉较大的系统空间,且所需耗费的成本也较高。再者,对于极小型化的电源适配器而言,两组滤波电感通过pcb上走线而电连接至其他组件时,则易受到近场干扰,导致emc的效能变差。

4.因此,如何发展一种滤波电感模块及其适用的组装结构,以在空间小且具emc需求的条件下,提高空间利用率,减小滤波电感间的近场干扰,同时简化装配制造过程并降低成本,是为本领域亟需面对的课题。

技术实现要素:

5.本发明的目的在于提供一种滤波电感模块。利用单一线架整合上下堆叠的两个滤波电感。两个滤波电感分别堆叠于单一线架的上方及下方,且通过线架上的线脚实现多种滤波器组合,例如两个共模滤波器的组合或一个共模滤波器与一差模滤波器组合。此外,两个滤波电感的磁件可环绕一中心轴而设置,使两个滤波电感的扼流圈处于同心位置,有效整合emc的效能。另一方面,滤波电感模块进一步结合电路板时,滤波电感模块通过单一线架设置于电路板上方时,线架下方的滤波电感则可通过电路板上的容置开口,至少部分容置于电路板下方,充分利用电路板下方空间进行布局,提高空间利用率。再者,由于线架上方与下方的滤波电感通过线架上的线脚连接,不用通过电路板上的走线(trace)连接,有效降低近场干扰的影响。

6.本发明的另一目的在于提供一种滤波电感模块。通过两个滤波电感共用单一线架,有助于减小滤波电感的磁件空间,更省略额外线架的使用,降低模块成本,提升产品的竞争力。再者,两滤波电感整合于单一线架上的绕线组合方式,于有限空间的电源适配器应用中,可实现大尺寸共模滤波器、小尺寸共模滤波器以及差模滤波器中任两者的组合布局,再通过电路板与其他例如smd器件连接,有利于实现空间应用的最佳化。另一方面,由于滤波电感模块与电路板的装配制造过程简单,两个滤波电感中较小尺寸者可通过电路板上的

开口而部分容置于电路板下方,搭配电路板下方smd器件配置,可以更有效地利用电路板下方的空间,且有助于整体体积小型化,使应用场景灵活,能够满足更小尺寸机种的高功率密度需求。

7.为达前述目的,本发明提供一种滤波电感模块,包括线架、第一滤波电感以及第二滤波电感。线架具有彼此相对设置的第一侧与第二侧以及多个线脚。第一滤波电感设置于线架的第一侧,且具有第一绕组以及第一磁芯,第一绕组绕设于第一磁芯上。第二滤波电感设置于线架的第二侧,且具有第二绕组以及第二磁芯,第二绕组绕设于第二磁芯上,其中第二绕组电性耦接至第一绕组。

附图说明

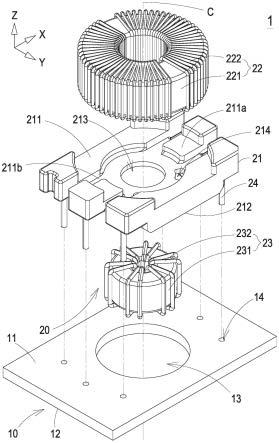

8.图1示意性示出本发明第一实施例的滤波电感模块的组装结构于上方视角的立体图。

9.图2示意性示出本发明第一实施例的滤波电感模块的组装结构于下方视角的立体图。

10.图3示意性示出本发明第一实施例的滤波电感模块的组装结构于上方视角的分解图。

11.图4示意性示出本发明第一实施例的滤波电感模块的组装结构于下方视角的分解图。

12.图5示意性示出本发明第一实施例的滤波电感模块的组装结构的侧面剖面图。

13.图6示意性示出本发明佳实施例的滤波电感模块的组装结构的应用电路拓扑图。

14.图7示意性示出本发明佳实施例的滤波电感模块的组装结构的顶视图。

15.图8示意性示出本发明佳实施例的滤波电感模块的组装结构的底视图。

16.图9示意性示出本发明第二实施例的滤波电感模块的组装结构于上方视角的立体图。

17.图10示意性示出本发明第二实施例的滤波电感模块的组装结构于下方视角的立体图。

18.图11示意性示出本发明第二实施例的滤波电感模块的组装结构于上方视角的分解图。

19.图12示意性示出本发明第二实施例的滤波电感模块的组装结构于下方视角的分解图。

20.图13示意性示出本发明第二实施例的滤波电感模块的组装结构的侧面剖面图。

具体实施方式

21.体现本发明特征与优点的一些典型实施例将在后段的说明中详细叙述。应理解的是本发明能够在不同的方式上具有各种的变化,其皆不脱离本发明的范围,且其中的说明及附图在本质上为当作说明之用,而非用于限制本发明。例如,若是本公开以下的内容叙述了将一第一特征设置于一第二特征之上或上方,即表示其包含了所设置的上述第一特征与上述第二特征是直接接触的实施例,亦包含了还可将附加的特征设置于上述第一特征与上述第二特征之间,而使上述第一特征与上述第二特征可能未直接接触的实施例。另外,本公

开中不同实施例可能使用重复的参考符号及/或标记。这些重复为了简化与清晰的目的,并非用以限定各个实施例及/或所述外观结构之间的关系。再者,为了方便描述附图中一组件或特征部件与另一(复数)组件或(复数)特征部件的关系,可使用空间相关用语,例如“上方”、“下方”、“左侧”、“右侧”及类似的用语等。除了附图所示出的方位之外,空间相关用语用以涵盖使用或操作中的装置的不同方位。所述装置也可被另外定位(例如,旋转90度或者位于其他方位),并对应地解读所使用的空间相关用语的描述。此外,当将一组件称为“连接到”或“耦合到”另一组件时,其可直接连接至或耦合至另一组件,或者可存在介入组件。尽管本公开的广义范围的数值范围及参数为近似值,但尽可能精确地在具体实例中陈述数值。另外,可理解的是,虽然“第一”、“第二”、“第三”等用词可被用于权利要求中以描述不同的组件,但这些组件并不应被这些用语所限制,在实施例中相应描述的这些组件是以不同的组件符号来表示。这些用语是为了分别不同组件。例如:第一组件可被称为第二组件,相似地,第二组件也可被称为第一组件而不会脱离实施例的范围。如此所使用的用语“及/或”包含了一或多个相关列出的项目的任何或全部组合。除在操作/工作实例中以外,或除非明确规定,否则本文中所公开的所有数值范围、量、值及百分比(例如角度、时间持续、温度、操作条件、量比及其类似者的那些百分比等)应被理解为在所有实施例中由用语“大约”或“实质上”来修饰。相应地,除非相反地指示,否则本公开及随附权利要求中陈述的数值参数为可视需要变化的近似值。例如,每一数值参数应至少根据所述的有效数字的数字且借由应用普通舍入原则来解释。范围可在本文中表达为从一个端点到另一端点或在两个端点之间。本文中所公开的所有范围包括端点,除非另有规定。

22.图1示意性示出本发明第一实施例的滤波电感模块的组装结构于上方视角的立体图。图2示意性示出本发明第一实施例的滤波电感模块的组装结构于下方视角的立体图。图3示意性示出本发明第一实施例的滤波电感模块的组装结构于上方视角的分解图。图4示意性示出本发明第一实施例的滤波电感模块的组装结构于下方视角的分解图。图5示意性示出本发明第一实施例的滤波电感模块的组装结构的侧面剖面图。于本实施例中,滤波电感模块的组装结构(以下简称组装结构)1包括电路板10与滤波电感模块20。电路板10具有彼此相对设置的一上表面11与一下表面12、一容置开口13和多个穿孔14。容置开口13与多个穿孔14贯穿上表面11以及下表面12。容置开口13可呈圆形,多个穿孔14排列于容置开口13的外侧。于本实施例中,滤波电感模块20设置于电路板10上而形成组装结构1。其中滤波电感模块20包括线架21、第一滤波电感22以及第二滤波电感23。线架21设置于电路板10的上表面11。线架21具有彼此相对设置的第一侧211与第二侧212以及多个线脚24。滤波电感模块20设置于电路板10上时,线架21的第二侧212面向电路板10的上表面11而彼此贴合。其中多个线脚24于空间上相对于电路板10上的多个穿孔14,且由线架21的第一侧211朝向第二侧212的方向延伸,并通过多个穿孔14贯穿电路板10。于本实施例中,第一滤波电感22设置于线架21的第一侧211。第一滤波电感22可具有第一绕组222以及第一磁芯221,第一绕组222绕设于第一磁芯221上。另外,第二滤波电感23设置于线架21的第二侧212,至少部分通过电路板10的容置开口13而超出电路板10的下表面12。其中第二滤波电感23可具有第二绕组232以及第二磁芯231,第二绕组232绕设于第二磁芯231上。于本实施例中,第一绕组222与第二绕组232对应连接至线架21上的多个线脚24,并通过多个线脚24与电路板10上其他器件(未附图)形成电连接。其中第二绕组232更通过多个线脚24中的一个与第一绕组222形

成电性连接。

23.值得注意的是,本发明利用单一线架21整合上下堆叠的第一滤波电感22与第二滤波电感23。第一滤波电感22与第二滤波电感23分别堆叠于单一线架21的第一侧211(上方)及第二侧212(下方),共用单一线架21,有助于减小滤波电感的磁件空间,更省略额外线架的使用,降低模块成本,提升产品的竞争力。其中线架21第二侧212(下方)的第二滤波电感23则通过电路板10上的容置开口13而超出下表面12,至少部分容置于电路板10下方,充分利用电路板10下方空间进行布局,提高空间利用率。再者,第一滤波电感22与第二滤波电感23通过线架21上的线脚24与电路板10连接,而不用通过电路板10上的走线(trace)连接,可有效降低近场干扰的影响。

24.于本实施例中,组装结构1可应用于电源适配器领域。电路板10的厚度t范围介于0.6mm至2.1mm,与滤波电感模块20组装时即可提供足够机械强度进行结构支撑。当然,于其他实施例中,电路板10的厚度t可视实际应用需求调变,本发明并不以此为限。于本实施例中,电路板10的下表面12上可设置有至少一表面贴装器件(surface mount device,smd)(未附图),其中第二滤波电感23超出电路板10的下表面12的高度d不大于至少一表面贴装器件的高度或其他插件(例如图6所示的cx1)线脚长度。于本实施例中,第二滤波电感23超出电路板10的下表面12的高度d亦可通过线架21容纳高度(未附图)以及电路板10的厚度t来调整。由于一般常见smd器件的厚度最大值约2.44mm,考虑插件类组件有线脚需要过炉,所以一般电路板10下方至少要留有2.5mm的空间。当然,第二滤波电感23超出电路板10的下表面12的高度d可视实际应用需求调整。本发明并不以此为限,且不再赘述。

25.于本实施例中,第一磁芯221与第二磁芯231均为一磁环,且环绕一中心轴c而设置。第一绕组222绕设于第一磁芯221形成的第一滤波电感22设置于线架21的第一侧211。于本实施例中,线架21包括一第一容置座211a,凹设于第一侧211。其中第一滤波电感22通过第一容置座211a设置于线架21的第一侧211。第一容置座211a的形状可视第一滤波电感22的外形而调整,本发明并不以此为限。另外,第二绕组232绕设于第二磁芯231形成的第二滤波电感23设置于线架21的第二侧212。于本实施例中,线架21亦包括一第二容置座212b凹设于第二侧212。其中第二滤波电感23通过第二容置座212b设置于线架21的第二侧212。第二容置座212b的形状可视第二滤波电感23的外形而调整,本发明并不以此为限。另外,于本实施例中,第二滤波电感23的尺寸不大于第一滤波电感22的尺寸。当然,本发明并不以此为限。

26.于本实施例中,线架21包括一中空部213,其可呈圆形,贯穿第一侧211与第二侧212而连通于第一容置座211a与第二容置座212b之间,有助于第一滤波电感22与第二滤波电感23的设置或对准。当第一滤波电感22与第二滤波电感23以贯穿中空部213的中心轴c为中心而设置时,即可使第一滤波电感22与第二滤波电感23形成的两个扼流圈处于同心位置。当然,本发明并不以此为限。于本实施例中,线架21还包括至少一开孔214,邻设于中空部213,且连通于第一侧211与第二侧212之间。其中位于第一侧211的第一绕组222可通过至少一开孔214而对应连接至线架21上的多个线脚24。当然,本发明并不受限于此。

27.图6示意性示出本发明佳实施例的滤波电感模块的组装结构的应用电路拓扑图。于本实施例中,组装结构1可应用于电源适配器领域。以45w及65w电源适配器的拓扑图为例。组装结构1所应用的电源适配器电路9,包括有一输入电压vac、第一共模滤波器fl1、一

第二共模滤波器fl2、一安规电容cx1、一差模滤波器l1、一整流桥bd1、一滤波电容c1、一变压器t1、一开关管q1以及同步整流管q101。其中输入电压vac的范围介于90vac至264vac。第一共模滤波器fl1电连接至输入电压vac,作用为抑制辐射emi。第二共模滤波器fl2与该第一共模滤波器fl1串联连接,作用为抑制共模传导emi。安规电容cx1跨接于第一共模滤波器fl1与第二共模滤波器fl2之间,作用为抑制差模传导emi。差模滤波器l1与第二共模滤波器fl2串联,作用为抑制差模传导emi。整流桥bd1连接至第二共模滤波器fl2与差模滤波器l,作用为将交流输入电压转为直流电压到滤波电容c1。滤波电容c1的容值范围介于82μf至120μf之间。值得注意的是,前述组装结构1的第一滤波电感22与第二滤波电感23可分别比对为电源适配器电路9中第一共模滤波器fl1、第二共模滤波器fl2以及差模滤波器l中任两者。

28.图7示意性示出本发明佳实施例的滤波电感模块的组装结构的顶视图。图8示意性示出本发明佳实施例的滤波电感模块的组装结构的底视图。参考图1至图8。于一实施例中,组装结构1的第一滤波电感22与第二滤波电感23分别比对为电源适配器电路9中第二共模滤波器fl2与第一共模滤波器fl1。即第一滤波电感22与第二滤波电感23为彼此串联的两个共模滤波电感。其中线架21包含的多个线脚24以六个线脚24a~24f作说明,非限制本发明。组装结构1中,位于线架21的第一侧211(上方)的第一滤波电感22的第一绕组222的左侧以线脚24a作为起绕点,绕组终点连接到线脚24b。第一滤波电感22的第一绕组222的右侧以线脚24d作为起绕点,绕组终点连接到线脚24e。而组装结构1中,位于线架21的第二侧212(下方)的第二滤波电感23的第二绕组232的左侧则可以线脚24b作为起绕点,绕组终点连接到线脚24c。第二滤波电感23的第二绕组232的右侧则可以线脚24e作为起绕点,绕组终点连接到线脚24f。第一滤波电感22与第二滤波电感23分别堆叠于线架21的第一侧211(上方)与第二侧212(下方)后,线脚24b和线脚24e为内部过渡线脚,省掉通过电路板10上走线(trace)部分做连接。滤波电感模块20等效为具有四个线脚24a、24c、24d、24f的滤波器组合,且第二滤波电感23更通过电路板10的容置开口13超出下表面12。其中第一滤波电感22与第二滤波电感23分别比对为较大尺寸的第二共模滤波器fl2与较小尺寸的第一共模滤波器fl1,共用线架21进行堆叠绕制。当然,本发明并不以此为限。

29.于另一实施例中,组装结构1的第一滤波电感22与第二滤波电感23分别比对为电源适配器电路9中第二共模滤波器fl2与差模滤波器l1。即第一滤波电感22与第二滤波电感23分别为一共模滤波电感以及一差模滤波电感,彼此串联设置。组装结构1中,位于线架21的第一侧211(上方)的第一滤波电感22的第一绕组222的左侧以线脚24a作为起绕点,绕组终点连接到线脚24b,线脚24c则可悬空。另外,第一滤波电感22的第一绕组222的右侧以线脚24d作为起绕点,绕组终点连接到线脚24e。而组装结构1中,位于线架21的第二侧212(下方)的第二滤波电感23的第二绕组232则可以线脚24e作为起绕点,绕组终点连接到线脚24f。第一滤波电感22与第二滤波电感23分别堆叠于线架21的第一侧211(上方)与第二侧212(下方)后,线脚24e为内部过渡线脚,省掉通过电路板10上走线(trace)部分做连接。滤波电感模块20等效为具有四个线脚24a、24b、24d、24f的滤波器组合,且第二滤波电感23更通过电路板10的容置开口13超出下表面12。其中第一滤波电感22与第二滤波电感23分别比对为较大尺寸的第二共模滤波器fl2与较小尺寸的第一共模滤波器fl1,共用线架21进行堆叠绕制。当然,本发明并不以此为限。

30.换言之,组装结构1的第一滤波电感22与第二滤波电感23可应用于堆叠电源适配器电路9中第一共模滤波器fl1、第二共模滤波器fl2以及差模滤波器l中任两者。以将差模滤波器l1或第一共模滤波器fl1设置于线架21的第二侧212(下方)为佳。由于第一滤波电感22与第二滤波电感23通过多个线脚24中的一个实现内部串联,不用通过电路板10上走线(trace)完成,可有效降低近场干扰的影响。另一方面,对于小尺寸电源适配器电路9而言,其电源布局比较紧凑。以45w/65w电源的尺寸为例,整体体积需维持于65cm3以下。而在紧凑的电源布局中,开关管q1与变压器t1若与第一共模滤波器fl1、第二共模滤波器fl2、安规电容cx1、差模滤波器l1等滤波器架构的距离过近,则可能产生较强的近场干扰。开关管q1即具有较强的电压变化(dv/dt)可产生电场近场干扰,会影响电路板10上的走线。然而本发明通过单一线架21上多个线脚24实现第一滤波电感22与第二滤波电感23的电性连接则可有效地减弱近场干扰的影响。

31.另一方面,线架21上第一容置座211a、理线槽211b、第二容置座212a、中空部213、至少一开孔214的设置均有助于简化第一滤波电感22与第二滤波电感23架构于单一线架21的流程,但其均不是限制本发明的主要技术特征。第一滤波电感22与第二滤波电感23并不限于形成的两个同心的扼流圈。第一容置座211a、理线槽211b、第二容置座212a、中空部213、至少一开孔214的尺寸及形状,可依第一滤波电感22与第二滤波电感23的尺寸及形状而调变或省略。本发明并不以此为限。需说明的是,线架21上线脚24的数量、尺寸、位置及排列方向亦可视实际应用需求而调变。本发明并不以此为限,且不再赘述。

32.于本实施例中,第一滤波电感22与第二滤波电感23可先架构于单一线架21上,之后形成的滤波电感模块20再与电路板10进行组装,以形成应用于电源适配器电路9的组装结构1,可进一步简化滤波电感配装工艺,降低模块成本,提升产品的竞争力。由于滤波电感模块20堆叠于电路板10上表面11时,通过容置开口13使第二滤波电感23的部分超出电路板10的下表面12,搭配电路板10下表面12配置smd等组件,可以更有效地利用电路板10的下方空间,且有助于整体体积小型化,使应用场景灵活,能够满足更小尺寸机种的高功率密度需求。当然,滤波电感模块20与电路板10的组装流程非限制本发明的必要技术特征,于此便不再赘述。

33.图9示意性示出本发明第二实施例的滤波电感模块的组装结构于上方视角的立体图。图10示意性示出本发明第二实施例的滤波电感模块的组装结构于下方视角的立体图。图11示意性示出本发明第二实施例的滤波电感模块的组装结构于上方视角的分解图。图12示意性示出本发明第二实施例的滤波电感模块的组装结构于下方视角的分解图。图13示意性示出本发明第二实施例的滤波电感模块的组装结构的侧面剖面图。于本实施例中,组装结构1a和滤波电感模块20a与图1至图7所示的组装结构1和滤波电感模块20相似,且相同的组件标号代表相同的组件、结构与功能,于此不再赘述。本实施例中,滤波电感模块20a更可架构为一表面贴装器件(surface mount device,smd)。组装结构1包括电路板10a与滤波电感模块20a。电路板10a具有彼此相对设置的一上表面11与一下表面12、一容置开口13以及多个焊盘15。容置开口13贯穿上表面11以及下表面12。容置开口13可呈圆形,多个焊盘15设置于上表面11,且排列于容置开口13的外侧。滤波电感模块20a包括线架21、第一滤波电感22以及第二滤波电感23。线架21设置于电路板10的上表面11。线架21具有彼此相对设置的第一侧211与第二侧212以及多个线脚24。滤波电感模块20a设置于电路板10a上时,线架21

的第二侧212面向电路板10a的上表面11而彼此贴合。于本实施例中,多个线脚24贯穿线架21的第一侧211与第二侧212,于空间上相对于电路板10a上的多个焊盘15。每一线脚24包括一挂线部241以及一表贴部242,分别设置于线架21的第一侧211与第二侧212。于本实施例中,第一绕组222与第二绕组232对应连接至多个线脚24的挂线部241,而多个线脚24的表贴部242则分别对应连接至电路板10a上表面11的焊盘15上,使第一绕组222与第二绕组232通过多个线脚24与电路板10a形成电性连接。

34.需说明的是,于本实施例中,线架21更呈表贴式,其线脚24的挂线部241外露于线架21的第一侧211。第一滤波电感22的第一绕组222可直接对应连接至第一侧211上方的挂线部241,而位于第二侧212的第二滤波电感23的第二绕组232则可通过线架21侧边的缝隙而走线到第一侧211,并挂接至对应的线脚24的挂线部241。于其他实施例中,第二绕组232亦可通过线架21的开孔214与理线槽211b而走线到第一侧211,并挂接至对应的线脚24的挂线部241上面。本发明并不以此为限。另外,滤波电感模块20a则可通过线脚24外露于第二侧212的表贴部242而连接至电路板10a,同时形成电性连接。此时电路板10a不需要开多个穿孔。当然,本发明并不以此为限。

35.值得注意的是,本发明利用单一线架21整合上下堆叠的第一滤波电感22与第二滤波电感23。第一滤波电感22与第二滤波电感23分别堆叠于单一线架21的第一侧211(上方)及第二侧212(下方),共用单一线架21,有助于减小滤波电感的磁件空间,更省略额外线架的使用,降低模块成本,提升产品的竞争力。其中线架21第二侧212(下方)的第二滤波电感23则通过电路板10a上的容置开口13而超出下表面12,至少部分容置于电路板10a下方,充分利用电路板10a下方空间进行布局,提高空间利用率。再者,第一滤波电感22与第二滤波电感23通过线架21上的线脚24与电路板10a连接,而不用通过电路板10a上的走线(trace)连接,可有效降低近场干扰的影响。

36.于本实施例中,组装结构1a亦可应用于电源适配器领域。电路板10a的厚度t范围介于0.6mm至2.1mm,与滤波电感模块20a组装时即可提供足够机械强度进行结构支撑。当然,于其他实施例中,电路板10a的厚度t可视实际应用需求调变,本发明并不以此为限。于本实施例中,电路板10a的下表面12上可设置有至少一表面贴装器件(surface mount device,smd)(未附图)。第二滤波电感23超出电路板10a的下表面12的高度d不大于至少一表面贴装器件的高度或其他插件(例如图6所示的cx1)线脚长度。于本实施例中,第二滤波电感23超出电路板10a的下表面12的高度d亦可通过线架21容纳高度(未附图)以及电路板10a的厚度t来调整。当然,组装结构1a亦可对应电源适配器电路9而应用,其对应的元件及排列顺序相同于组装结构1。但本发明不受限于此,且不再赘述。综上所述,本发明的实施例提供一种滤波电感模块。利用单一线架整合上下堆叠的两个滤波电感。两个滤波电感分别堆叠于单一线架的上方及下方,且通过线架上的线脚实现多种滤波器组合,例如两个共模滤波器的组合或一个共模滤波器与一差模滤波器组合。此外,两个滤波电感的磁件可环绕一中心轴而设置,使两个滤波电感的扼流圈处于同心位置,有效整合emc的效能。另一方面,滤波电感模块进一步结合电路板时,滤波电感模块通过单一线架设置于电路板上方时,线架下方的滤波电感则可通过电路板上的容置开口,至少部分容置于电路板下方,充分利用电路板下方空间进行布局,提高空间利用率。再者,由于线架上方与下方的滤波电感通过线架上的线脚连接,不用通过电路板上的走线(trace)连接,有效降低近场干扰的影响。本发

明通过两个滤波电感共用单一线架,有助于减小滤波电感的磁件空间,更省略额外线架的使用,降低模块成本,提升产品的竞争力。再者,两滤波电感整合于单一线架上的绕线组合方式,于有限空间的电源适配器应用中,可实现大尺寸共模滤波器、小尺寸共模滤波器以及差模滤波器中任两者的组合布局,再通过电路板与其他例如smd器件连接,有利于实现空间应用的最佳化。另一方面,由于滤波电感模块与电路板的装配制造过程简单,两个滤波电感中较小尺寸者可通过电路板上的开口而部分容置于电路板下方,搭配电路板下方smd器件配置,可以更有效地利用电路板下方的空间,且有助于整体体积小型化,使应用场景灵活,能够满足更小尺寸机种的高功率密度需求。

37.本领域技术人员在考虑说明书及公知常识后,将容易想到本发明的其他实施方案。本发明旨在涵盖本发明的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本发明的一般性原理并包括本发明未公开的本技术领域中的公知常识或者惯用技术手段。说明书和实施例仅被视为是示例性的,本发明的真正范围和构思由权利要求指出。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1