半导体结构及其制作方法与流程

本发明涉及半导体,特别涉及一种半导体结构及其制作方法。

背景技术:

1、横向双扩散金属氧化物半导体(laterally-diffused metal-oxidesemiconductor,ldmos)场效应晶体管,是在高压功率集成电路中常见的一种半导体器件,用于满足高压、实现功率控制等方面的需求。ldmos一个突出的优点是与传统cmos工艺高度兼容,业界通常将ldmos器件、互补金属氧化物半导体(cmos)场效应管和双极结型(bjt)晶体管集成在一起提供bcd(bipolar-cmos-dmos)工艺。

2、图1为一种ldmos器件的结构示意图。参考图1,该ldmos器件例如为无外延层的n型器件,d端为漏极区11(drain)的引出端,g端为栅极15(gate)的引出端,s&b端为源极区13(source)和p阱16(bulk)的引出端。漏极区11和栅极15之间有个横向扩散区12,能够承担高电压,进而构成ldmos。这种ldmos器件的好处是栅极15和cmos器件的栅极能够在同一制程中制作,源极区13和漏极区11也能够cmos器件的源漏极区在同一制程中制作,这样只需要在标准cmos工艺的基础上增加横向扩散区12和体区14的注入就能集成ldmos器件。

3、随着集成电路工艺的发展和集成度的提高,器件沟道长度越来越小。上述的ldmos器件暴露出一个明显的缺点,ldmos器件的p阱16为了与cmos器件的阱区在同一制程中形成,p阱16需要在制作栅极15之前形成,p阱16和栅极15的相对对准误差较大,导致器件的均匀性较差,如图2所示,表现为ldmos器件阈值电压(vt)的分布范围较大,且随着器件沟道长度的缩短,阈值电压的分布范围越大。

4、针对上述ldmos器件的均匀性较差、阈值电压分布范围较大的问题,目前业界有两种主流的解决办法。一种是直接升级设备,通过更好设备和耗材改善p阱16和栅极15的相对对准精度;但该方法带来生产成本的显著增加,而且通常在新产线建立和旧产线扩产时才便于实施,已有产线很难抛弃现存的昂贵光刻机设备。另一种是改进ldmos器件的设计,ldmos器件的p阱16不再与cmos器件的阱区在同一制程中制作,而是利用与栅极15配合的自对准工艺来制作ldmos器件的p阱16;但如此工艺开发难度增加,导致工艺层次和整体成本的明显增加。

技术实现思路

1、本发明的目的之一是提供一种半导体结构及其制作方法,基于现有机台的工艺能力,在不更改器件设计,不增加工艺层次,不增加生产成本的情况下,解决了ldmos器件均匀性差的问题,有利于提高ldmos器件的稳定性。

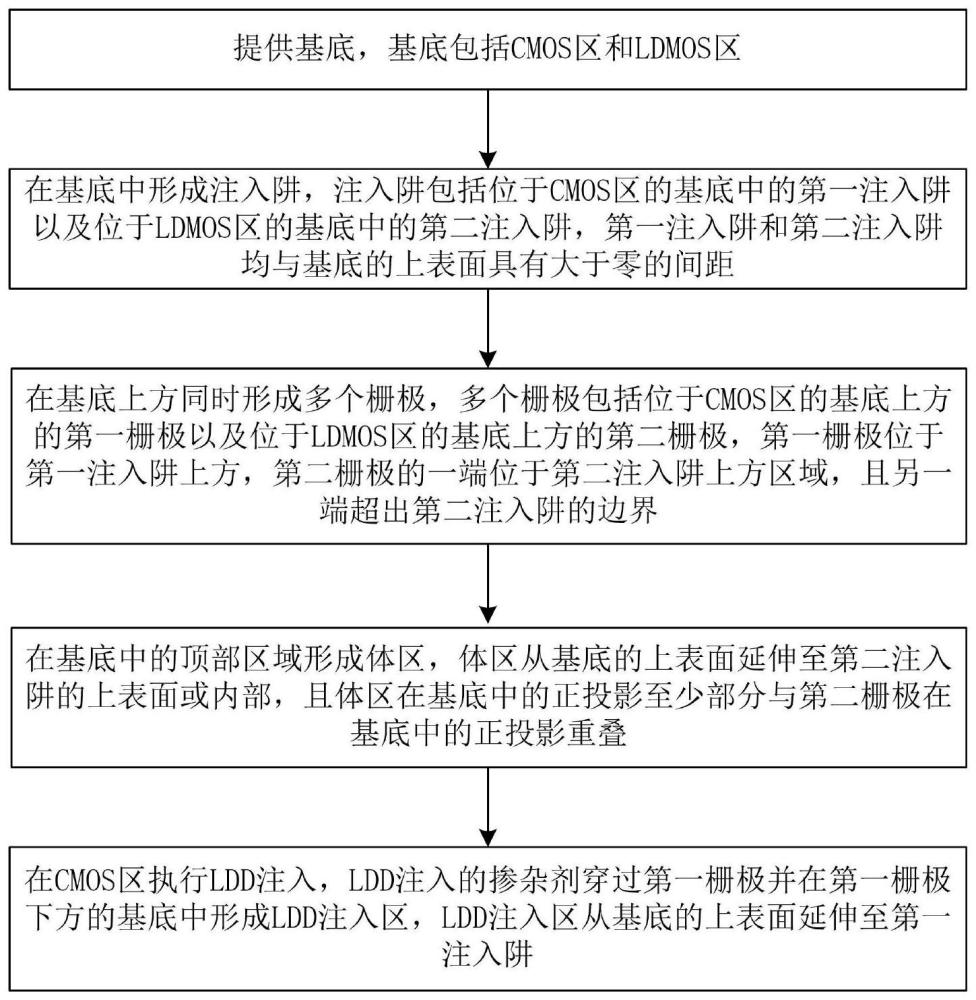

2、为了实现上述上述目的,本发明提供一种半导体结构的制作方法。所述制作方法包括:

3、提供基底,所述基底包括cmos区和ldmos区;

4、在所述基底中形成注入阱,所述注入阱包括位于所述cmos区的基底中的第一注入阱以及位于所述ldmos区的基底中的第二注入阱,所述第一注入阱和所述第二注入阱均与所述基底的上表面具有大于零的间距;

5、在所述基底上方同时形成多个栅极,所述多个栅极包括位于所述cmos区的基底上方的第一栅极以及位于所述ldmos区的基底上方的第二栅极,所述第一栅极位于所述第一注入阱上方,所述第二栅极的一端位于所述第二注入阱上方区域,且另一端超出所述第二注入阱的边界;

6、在所述基底中的顶部区域形成体区,所述体区从所述基底的上表面延伸至所述第二注入阱的上表面或内部,且所述体区在所述基底中的正投影至少部分与所述第二栅极在所述基底中的正投影重叠;以及

7、在所述cmos区执行ldd注入,所述ldd注入的掺杂剂穿过所述第一栅极并在所述第一栅极下方的基底中形成ldd注入区,所述ldd注入区从所述基底的上表面延伸至所述第一注入阱。

8、可选的,所述提供基底,包括:在所述ldmos区的基底中形成深阱;所述深阱的顶部与所述第二注入阱的底部相连接。

9、可选的,所述提供基底,包括:在所述ldmos区的基底中的顶部区域形成横向扩散区,所述横向扩散区位于所述第二注入阱的侧边并与所述第二注入阱具有设定间距;所述第二栅极的一端位于所述第二注入阱上方,所述第二栅极的另一端位于所述横向扩散区上方。

10、可选的,所述制作方法包括:所述在所述cmos区执行ldd注入之后,在所述第一栅极两侧的基底中形成第一源极区和第一漏极区,在所述第二栅极两侧的基底中形成第二源极区和第二漏极区;所述第一源极区和所述第一漏极区位于所述第一注入阱上方,且部分延伸进入所述第一注入阱内的顶部区域;所述第二源极区位于所述第二注入阱上方且部分延伸进入所述第二注入阱内的顶部区域,所述第二漏极区位于所述横向扩散区内的顶部区域。

11、可选的,所述制作方法包括:所述在所述cmos区执行ldd注入之后,在所述第一注入阱和所述第二注入阱上方形成引出区,所述引出区与对应的所述第一注入阱或所述第二注入阱相连接。

12、可选的,所述cmos区用于形成n型cmos器件,所述ldd注入的掺杂剂为硼;或者,所述cmos区用于形成p型cmos器件,所述ldd注入的掺杂剂为磷。

13、可选的,所述ldd注入的能量根据所述第一栅极的厚度设置。

14、可选的,所述在所述基底中的顶部区域形成体区的步骤中,向所述基底中的顶部区域注入的掺杂剂量补偿所述基底中的顶部区域由于所述第二注入阱上表面与所述基底的上表面具有大于零的间距而减少的掺杂剂量。

15、可选的,位于所述cmos区和所述ldmos区相接处的所述第一注入阱和所述第二注入阱相连接。

16、本发明的另一方面提供一种半导体结构,所述半导体结构包括基底以及位于所述基底上方的第一栅极和第二栅极;所述基底包括cmos区和ldmos区;所述基底中形成有注入阱、体区和ldd注入区;所述注入阱包括在同一步骤中形成第一注入阱和第二注入阱,所述第一注入阱位于所述cmos区的基底中,所述第二注入阱位于所述ldmos区的基底中,所述第一注入阱和所述第二注入阱均与所述基底的上表面具有大于零的间距;所述第一栅极形成在所述cmos区的基底上方,所述第二栅极形成在所述ldmos区的基底上方;所述第一栅极位于所述第一注入阱上方;所述第二栅极的一端位于所述第二注入阱上,且另一端超出所述第二注入阱的边界;所述体区形成在所述基底中的顶部区域,从所述基底的上表面延伸至所述第二注入阱的上表面或内部,且所述体区在所述基底中的正投影至少部分与所述第二栅极在所述基底中的正投影重叠;所述ldd注入区形成在所述第一栅极下方的基底中,且从所述基底的上表面延伸至所述第一注入阱。

17、本发明还提供一种半导体结构。所述半导体结构包括基底以及位于所述基底上方的第一栅极和第二栅极;所述基底包括cmos区和ldmos区,所述基底中形成有注入阱、横向扩散区、体区、ldd注入区、第一源极区、第一漏极区、第二源极区和第二漏极区;所述注入阱包括位于所述cmos区的基底中的第一注入阱以及位于所述ldmos区的基底中的第二注入阱;所述横向扩散区形成在所述ldmos区的基底中的顶部区域,位于所述第二注入阱的侧边并与所述第二注入阱具有设定间距;所述第一栅极形成在所述cmos区的基底上方,所述第二栅极形成在所述ldmos区的基底上方,所述第一栅极位于所述第一注入阱上方,所述第二栅极的一端位于所述第二注入阱上方区域,且另一端位于所述横向扩散区上方区域;所述体区形成在所述基底中的顶部区域,从所述基底的上表面延伸至所述第二注入阱的上表面或内部,且所述体区在所述基底中的正投影至少部分与所述第二栅极在所述基底中的正投影重叠;所述ldd注入区形成在所述第一栅极下方的基底中,且从所述基底的上表面延伸至所述第一注入阱;所述第一源极区和所述第一漏极区位于所述cmos区,所述第二源极区和所述第二漏极区位于所述ldmos区。

18、与现有技术相比,本发明的半导体结构及其制作方法具有以下优势:(1)本技术基于现有机台的工艺能力、不更改器件设计、不增加工艺层次、不增加生产成本的情况下,通过使得第一注入阱和第二注入阱均与基底的上表面具有大于零的间距,再通过体区来调制ldmos器件的阈值电压,通过位于第一栅极下方的ldd注入区来调整cmos器件的阈值电压,也就是说,本技术通过工艺流程的改变避免了第二注入阱和第二栅极的相对对准偏差对ldmos器件的影响,解决了ldmos器件沟道长度缩短导致的器件均匀性变得更差的问题,即解决了ldmos器件均匀性差的问题,有利于提高ldmos器件的稳定性,且不需要变更机台、耗材和设计,工艺开发难度小,所需要的开发时间短,极大地节省了制造成本同时降低了开发风险;(2)通过体区来调制ldmos器件的阈值电压,不会给ldmos器件带来额外风险;(3)通过位于第一栅极下方的ldd注入区来调整cmos器件的阈值电压,能够使得cmos器件的阈值电压和现有技术保持一致,即不会影响cmos器件的阈值电压。

- 还没有人留言评论。精彩留言会获得点赞!