一种具有选通与多比特存储功能的阵列集成器件及其制备方法

1.本发明涉及半导体技术领域,具体涉及一种具有选通与多比特存储功能的阵列集成器件及其制备方法。

背景技术:

2.阻变存储器、相变存储器、铁电存储器等新兴的非易失性存储器具有存储数据信息的功能,保证计算机在断电后数据不丢失,在集成电路领域扮演着重要角色。其中,阻变存储器具有易于集成的两端交叉结构、高擦写速度、低转变功耗、优异的耐久性与保持特性,成为下一代非易失性存储器的发展核心。虽然阻变存储器通过交叉阵列的结构可以实现高密度的集成,但是集成过程中不可避免地遇到串扰电流的应用,限制了器件的大规模集成。需要开发具有选通功能的器件并将其与阻变存储器件集成,共同实现对不同通道器件的电压精准施加,从而避免串扰电流对器件信号采集的影响。

3.在选通器件与存储器件集成的过程中,电流匹配、材料匹配、工艺匹配以及电压匹配等方面的高标准要求增加了器件的集成难度。选取具有相同工作电流范围、兼容材料体系、兼容制备工艺以及匹配的工作电压使得构建完全匹配的选通器件与存储器件难以实现。因此,开发一种同时具有选通功能以及存储功能的电子器件,将完美解决这一难题,使得其完成同源集成,极大程度地提高了器件的可集成性并降低了生产成本。

4.考虑到选通器件与存储器件的最终目标是提高器件的集成度,实现高密度存储,可以在同一器件单元实现多态存储将从单个硬件的角度实现整体的存储容量提升。因此,发展具有多比特存储的新型存储器件在构建阵列集成的高密度存储芯片方面具有重要应用前景。

技术实现要素:

5.本发明利用活性金属原子掺杂的方式构建浓度渐变的功能层以制备具有选通与多比特存储功能的阵列集成器件,借助活性金属原子扩散实现器件状态的可控调节,在同一器件单元实现选通的效果以及多比特存储的功能,并利用同一器件结构实现选通器与存储器的高密度交叉集成,解决集成阵列中的串扰电流问题、误读问题与集成过程中的电流匹配问题,提高了器件的可集成度与存储容量。

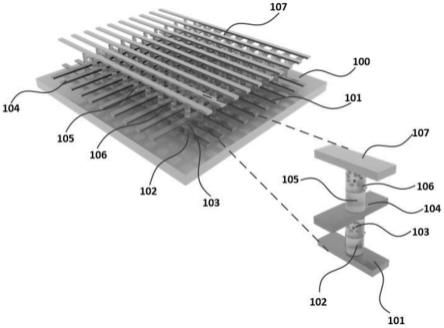

6.具体而言,本发明的具有选通与多比特存储功能的阵列集成器件,包括:衬底;线状底层电极,多根线状底层电极相互间隔,平行排列,形成在所述衬底上;第一氧化物薄膜层,形成在所述线状底层电极上;第一掺杂活性金属的氧化物薄膜层,形成在所述第一氧化物薄膜层上;线状中间层电极,多根线状中间层电极相互间隔,平行排列,且其延伸方向与所述线状底层电极的延伸方向垂直,形成在所述第一掺杂活性金属的氧化物薄膜层上;第二氧化物薄膜层,形成在所述线状中间层电极上;第二掺杂活性金属的氧化物薄膜层,形成在所述第二氧化物薄膜层上;线状顶层电极,多根线状顶层电极相互间隔,平行排列,且其

延伸方向与线状中间层电极的延伸方向垂直,形成在所述第二掺杂活性金属的氧化物薄膜层上,对器件线状顶层电极施加电压时,通过顶层器件的选通作用,实现对直接相连的存储器的激励效果,获得器件的多态存储功能。

7.本发明的具有选通与多比特存储功能的阵列集成器件中,优选为,所述第一氧化物薄膜层和所述第二氧化物薄膜层为hfo2,zro2,zno。

8.本发明的具有选通与多比特存储功能的阵列集成器件中,优选为,所述第一掺杂活性金属的氧化物薄膜层和所述第二掺杂活性金属的氧化物薄膜层为ag或cu掺杂的hfo2,zro2,zno。

9.本发明的具有选通与多比特存储功能的阵列集成器件中,优选为,所述线状中间层电极的材料为ag,cu。

10.本发明的具有选通与多比特存储功能的阵列集成器件中,优选为,所述线状底层电极和所述线状顶层电极的材料为au,pt,pd,al。

11.本发明还公开一种具有选通与多比特存储功能的阵列集成器件制备方法,包括以下步骤:在衬底上形成多根相互间隔,平行排列的线状底层电极;在所述线状底层电极上形成第一氧化物薄膜层;在所述第一氧化物薄膜层上形成第一掺杂活性金属的氧化物薄膜层;在第一掺杂活性金属的氧化物薄膜层上形成多根相互间隔,平行排列的线状中间层电极,且其延伸方向与所述线状底层电极的延伸方向垂直;在所述线状中间层电极上形成第二氧化物薄膜层;在所述第二氧化物薄膜层上形成第二掺杂活性金属的氧化物薄膜层;线状顶层电极,在所述第二掺杂活性金属的氧化物薄膜层上形成多根相互间隔,平行排列的线状顶层电极,且其延伸方向与线状中间层电极的延伸方向垂直,对器件线状顶层电极施加电压时,通过顶层器件的选通作用,实现对直接相连的存储器的激励效果,获得器件的多态存储功能。

12.本发明的具有选通与多比特存储功能的阵列集成器件制备方法中,优选为,所述第一氧化物薄膜层和所述第二氧化物薄膜层为hfo2,zro2,zno。

13.本发明的具有选通与多比特存储功能的阵列集成器件制备方法中,优选为,所述第一掺杂活性金属的氧化物薄膜层和所述第二掺杂活性金属的氧化物薄膜层为ag或cu掺杂的hfo2,zro2,zno。

14.本发明的具有选通与多比特存储功能的阵列集成器件制备方法中,优选为,所述线状中间层电极的材料为ag,cu。

15.本发明的具有选通与多比特存储功能的阵列集成器件制备方法中,优选为,所述线状底层电极和所述线状顶层电极的材料为au,pt,pd,al。

16.有益效果:

17.(1)打破传统的器件工作模式,在同一器件构建基于活性金属原子的浓度差,使得器件同时实现选通的功能以及存储的功能,增加了器件的功能性和可重构能力。

18.(2)采用同一结构的同源器件实现选通与存储器件的交叉阵列集成,完美解决电流匹配、材料匹配、工艺匹配以及电压匹配等问题,降低了器件集成的成本,避免了不同器件集成过程中的排异性。

19.(3)构建了具有多比特存储功能的集成器件,在同一器件实现多值存储功能,从存储器的角度提高了存储密度,进一步增加了器件的高密度存储能力。

附图说明

20.图1是具有选通与多比特存储功能的阵列集成器件制备方法的流程图。

21.图2~图6是具有选通与多比特存储功能的阵列集成器件制备方法各阶段的结构示意图。

22.图7是具有选通与多比特存储功能的阵列集成器件各阻态的示意图。

具体实施方式

23.为了使本发明的目的、技术方案及优点更加清楚明白,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

24.在本发明的描述中,需要说明的是,术语“上”、“下”、“垂直”“水平”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。

25.此外,在下文中描述了本发明的许多特定的细节,例如器件的结构、材料、尺寸、处理工艺和技术,以便更清楚地理解本发明。但正如本领域的技术人员能够理解的那样,可以不按照这些特定的细节来实现本发明。除非在下文中特别指出,器件中的各个部分可以由本领域的技术人员公知的材料构成,或者可以采用将来开发的具有类似功能的材料。

26.图1是具有选通与多比特存储功能的阵列集成器件制备方法的流程图。如图1所示,具有选通与多比特存储功能的阵列集成器件制备方法包括以下步骤:

27.步骤s1,准备硅片衬底100,用于制备具有选通与多比特存储功能的阵列集成器件。衬底还可以是sic、玻璃、gan等。

28.步骤s2,利用光刻和磁控溅射法在衬底100上制备厚度为50nm~100nm的线状底层电极pt101,如图2所示。多根线状底层电极pt101相互间隔,平行排列。底层电极的材料还可以是au,pd,al等惰性金属;线状底层电极的线宽优选为50μm,范围可取10μm~100μm;线长优选为500μm,范围可取200μm~500μm。

29.步骤s3,利用磁控溅射法在底层电极上生长厚度为50nm的氧化物薄膜hfo2102,如图3所示。氧化物薄膜还可以是zro2,zno等;厚度范围可取20nm~70nm。

30.步骤s4,利用多源磁控共溅射法在氧化物薄膜hfo2102上生长厚度为30nm的ag掺杂的zno薄膜103,如图4所示。其中,掺杂金属还可以是cu等活性金属;氧化物薄膜还可以是zro2,hfo2等;厚度范围可取10nm~40nm。

31.步骤s5,利用磁控溅射法在ag掺杂的zno薄膜103上生长厚度为70nm的线状中间层电极ag104,使得器件实现ag原子按浓度扩散分布的结构,完成底层存储器件的制备,如图5所示。线状中间层电极的宽度为50μm,长度为500μm。多根线状中间层电极ag104相互间隔,平行排列,且线状中间层电极的延伸方向与线状底层电极的延伸方向垂直,以实现单层的交叉阵列结构。线状中间层电极的材料还可以是cu等活性金属;厚度范围可取50nm~

100nm;线宽范围可取10μm~100μm;线长范围可取200μm~500μm。

32.步骤s6和步骤s7,重复步骤s3和步骤s4的方法,在中间层电极104上一次形成hfo2薄膜105和ag掺杂的zno薄膜106,完成顶层选通器件的制备。

33.步骤s8,在上述结构上形成线状顶层电极au107,获得pt101/hfo2102/zno-ag103/ag104/hfo2105/zno-ag106/au107的器件结构,完成具有选通与多比特存储功能的阵列集成器件制备。多根线状顶层电极au107相互间隔,平行排列,且线状顶层电极的延伸方向与线状中间层电极的延伸方向垂直,如图6所示。线状顶层电极厚度优选为70nm,线宽优选为50μm,长度优选为500μm。但是本发明不限定于此,电极材料还可以是pt,pd,al等惰性金属;厚度范围可取50nm~100nm;线宽范围可取10μm~100μm;线长范围可取200μm~500μm。

34.如图7所示,对器件顶层电极施加电压时,通过顶层器件的选通作用,实现对直接相连的存储器的激励效果,获得器件的多态存储功能,满足高密度存储阵列的需求。具体而言,未施加电压时,器件首先处于初始阻态,对应于阻态1。当对顶电极施加电压时,顶层的器件首先达到导通状态,实现选通效果,随即底层器件中形成较弱的导电通道,器件的阻态降低,器件处于阻态2。继续对顶电极施加电压,底层器件的导电通道加强,器件的阻态继续降低,器件处于阻态3。继续对顶电极施加电压,底层器件的导电通道达到最强,器件的阻态进一步降低,器件处于阻态4。

35.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1