一种芯片及晶圆的制作方法

1.本发明涉及芯片标识技术领域,尤其涉及一种芯片及晶圆。

背景技术:

2.在晶圆制作中,为了辨识芯片在晶圆上的相对位置,以及对各芯片相互之间进行区分,通常需要制作芯片标识(die id)。

3.目前,现有技术中的芯片标识的结构形式有诸多种。图1是现有的一种芯片标识的示意图,图2是现有的另一种芯片标识的示意图。参考图1,芯片标识采用十进制或十六进制数和/或字母呈现。这种方式,如果以晶圆的左下角为零点,芯片在晶圆的相对位置可以用x,y坐标表示。根据常见的6寸、8寸的晶圆尺寸和芯片的大小,通常可以采用三位数表示x坐标以及三位数表示y坐标,那么芯片标识需要六位数。如果根据常见的数字,字母芯片标识尺寸,宽4个像素结构,高4个像素结构,而六位数对应至少九十六个像素结构。通常的芯片标识是由接触式曝光机制作,分辨率通常能在3-5微米一个像素。九十六个像素结构所占面积较大,降低了芯片有效的面积。

4.参考图2,芯片标识采用二维码或条形码呈现。通过对芯片的x,y坐标的六个字符做图形编码,一个二维码通常需要8乘以8个像素结构表示。六十多个像素结构所占面积仍然较大,芯片有效的面积被降低。

技术实现要素:

5.本发明提供了一种芯片及晶圆,以降低芯片标识的面积,提高芯片的有效面积。

6.根据本发明的一方面,提供了一种芯片,所述芯片包括功能区和标识区;

7.在所述标识区内,所述芯片的表面包括第一像素结构和/或第二像素结构;所述第一像素结构和所述第二像素结构分别表示数字0和1或者1和0;所述标识区内的所有所述第一像素结构及所述第二像素结构组成所述芯片的标识信息;

8.其中,所述芯片的标识信息由所述芯片的原始标识信息经过转换得到,转换方式包括二分法、斐波那契查找法或者二进制转换。

9.可选地,所述第一像素结构或所述第二像素结构包括凹槽,相应的,所述第二像素结构或所述第一像素结构包括所述芯片的表面本身;

10.或者,所述第一像素结构或所述第二像素结构包括凸起,相应的,所述第二像素结构或所述第一像素结构包括所述芯片的表面本身。

11.可选地,所述芯片的上表面包括所述第一像素结构和/或所述第二像素结构;

12.所述第一像素结构在所述芯片的下表面的垂直投影,与所述第二像素结构在所述芯片的下表面的垂直投影相同。

13.可选地,在所述标识区内,所述芯片的表面还包括边框;

14.所述第一像素结构和所述第二像素结构均设置于所述边框内;所述边框用于限制所述第一像素结构和所述第二像素结构的总数量,为目标像素结构数量。

15.可选地,所述标识区包括多个标识子区;多个所述标识子区分散在所述功能区的周围;所述第一像素结构和所述第二像素结构位于至少一个所述标识子区。

16.可选地,所述标识区内的所有所述第一像素结构及所述第二像素结构按至少一行和/或至少一列依次排布。

17.可选地,在所述标识区内,所述芯片的表面还包括识别位结构,所述识别位结构用于规定所述标识信息的读取方向。

18.可选地,所述第一像素结构和/或所述第二像素结构在所述芯片的下表面上的垂直投影面积为(1~10μm)

×

(1~10μm)。

19.可选地,相邻两个所述第一像素结构之间的间距、相邻两个所述第二像素结构之间的间距以及相邻的所述第一像素结构和所述第二像素结构之间的间距均为零。

20.根据本发明的另一方面,提供了一种晶圆,包括衬底和多个如上一方面所述的芯片;所述芯片设置于所述衬底之上,各个所述芯片的标识信息不同。

21.本发明实施例的技术方案,通过在芯片的标识区内的表面上,形成第一像素结构和/或第二像素结构,第一像素结构和第二像素结构分别表示数字0和1或者1和0,进而采用标识区内的所有第一像素结构及第二像素结构组成芯片的标识信息;相较于采用十进制数和/或字母、或者采用二维码或条形码呈现芯片标识而言,芯片的标识信息对应的所有像素结构所占面积被降低,从而提高了芯片有效面积,也即提高了芯片的功能区的面积。

22.应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

附图说明

23.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

24.图1是现有的一种芯片标识的示意图;

25.图2是现有的另一种芯片标识的示意图;

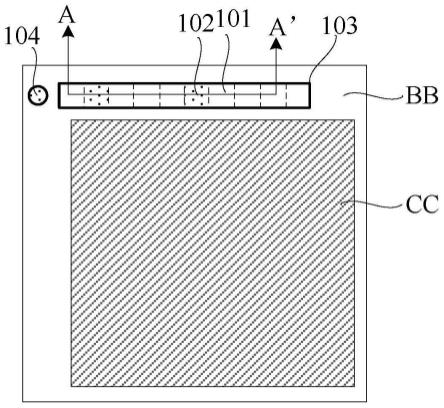

26.图3是本发明实施例提供的一种芯片的结构示意图;

27.图4是本发明实施例提供的另一种芯片的结构示意图;

28.图5是图3沿剖面线aa’的剖面结构示意图;

29.图6是本发明实施例提供的另一种芯片的结构示意图。

具体实施方式

30.为了使本技术领域的人员更好地理解本发明方案,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分的实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明保护的范围。

31.需要说明的是,本发明的说明书和权利要求书及上述附图中的术语“第一”、“第

二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

32.图3是本发明实施例提供的一种芯片的结构示意图。参考图3,芯片包括:功能区cc和标识区bb;在标识区bb内,芯片的表面包括第一像素结构101和/或第二像素结构102;第一像素结构101和第二像素结构102分别表示数字0和1或者1和0;标识区bb内的所有第一像素结构101及第二像素结构102组成芯片的标识信息;其中,芯片的标识信息由芯片的原始标识信息经过转换得到,转换方式包括二分法、斐波那契查找法或者二进制转换。

33.具体地,芯片的功能区cc用于形成芯片器件结构,标识区bb可以是除功能区cc以外的空白区域。一般芯片包括层叠设置的多层金属层、多层介质层和多层半导体层,故芯片的表面既可以是金属层表面、介质层表面与可以是半导体层表面,还可以部分区域为金属层表面而部分区域为介质层表面以及部分区域为半导体层表面,取决于实际情况,不作具体限定。此外,为了方便较为直观地看到芯片标识,一般芯片标识设置在芯片的上表面(或称顶面),芯片的下表面与上表面相对,下表面也即芯片的底面。

34.像素结构包括第一像素结构101或第二像素结构102。芯片的原始标识信息可以是采用十进制或十六进制数/字母表示的标识信息,芯片的标识信息是由芯片的原始标识信息经过转换得到,转换方式包括二分法、斐波那契查找法或者二进制转换。即,采用十进制数对芯片编码一个标识信息,构成芯片的原始标识信息;进而将芯片的原始标识信息经过二分法、斐波那契查找法或者二进制转换,转换为芯片的标识信息,此时芯片的标识信息为一串包括多个数字1和/或多个数字0的数;最终采用第一像素结构101和/或第二像素结构102将芯片的标识信息呈现在芯片的表面。

35.二进制转换方法例如为:将一个十进制的数转换为二进制数。比如,将十进制数249转换为二进制数为11111001。

36.二分法转换方法例如为:将一个十进制的数通过二分查找的方法转换为逻辑判断数字0和/或1。示例性的,预先已知要转换十进制数x的最大范围区间[a,b),然后将要转换十进制的数x与当前判断范围区间的中间数int((a+b)/2)比较(“int()”为取整操作),若x≥int((a+b)/2),则逻辑判断数字记为1,得到新的范围区间[int((a+b)/2),b);若x<int((a+b)/2),则逻辑判断数字记为0,得到新的范围区间[a,int((a+b)/2));以此类推,通过不断缩小一半的范围区间,直到范围区间只剩数x为止。例如,可以取要转换十进制数x的最大范围区间为[0,1000),则十进制数249用二分法转换为逻辑判断数字0011111111。

[0037]

斐波那契查找法转换方法例如为:将一个十进制的数通过斐波那契查找的方法转换为逻辑判断数字0和/或1。示例性的,假设需要查找的十进制数字为x,其所属查找数组为g0=[0,1,2,

…

,m-1,m],构建斐波那契数组f=[1,1,2,3,5,

…

,f(n-2),f(n-1),f(n)],其中,f(n)=f(n-1)+f(n-2),f(n)≥m+1;然后将查找数组g的数组大小补齐到f(n),可选的,补齐规则可以是最大值补齐或自然数组补齐等。例如,已知x为一个三位数,则构建斐波那契数组f(17)=1597,f=[1,1,2,3,5,8,13,

…

,610,987,1597],按自然数组构建补齐后的

查找数组为g=[0,1,2,3,4,

…

,g(m),

…

,1595,1596],其中g(m)为当前查找数组序号m对应的十进制数,m为自然数。

[0038]

定义中间数g(mid)与逻辑判断数字0和/或1转换规则为:假设当前查找数组g=[g(low),

…

,g(mid),

…

,g(high)],mid=low+f(n-2),若x》g(mid),则逻辑判断数码记为1,新的查找数组为g=[g(low),

…

,g(mid),

…

,g(high)],low=mid+1,n=n-2;若x≤g(mid),则逻辑判断数码记为0,新的查找数组为g=[g(low),

…

,g(mid),

…

,g(high)],low=mid,n=n-1。以此类推,直至最新的查找数组仅剩十进制x为止。例如,假设待查找数x=249,则用斐波那契查找法转换为逻辑判断数字0100011100。

[0039]

在二分法中,搜索的区域是1:1。在斐波那契查找法中,搜索的区域比列接近黄金分割点,即为1:1.618。这是两个算法的最大的不同。针对于数字的查找,斐波那契查找法相较于二分法而言,具有更高的效率,不需要用到乘除法。本发明实施例中,具体采用二进制转换、斐波那契查找法或者是二分法将芯片的原始标识信息转换为芯片的标识信息,可根据实际需要进行选择,本实施例对其不作具体限定,保证所转换到的数由数字0和1组成且可以采用第一像素结构101和第二像素结构102进行呈现即可。

[0040]

示例性地,芯片的原始标识信息为十进制数的266,将266经过二分法转换得到芯片的标识信息为0100010000;若第一像素结构101表示0且第二像素结构102表示1,则芯片的标识信息在芯片表面上的呈现可如图3所示意。其中,采用二分法进行转换的具体过程包括:

[0041]

该数字是否大于或等于500;否,记录0,确认数字在0至499之间。该数字是否大于或等于250;是,记录1,确认数字在250至499之间。该数字是否大于或等于375;否,记录0,确认数字在250至374之间。该数字是否大于或等于312;否,记录0,确认数字在250至311之间。该数字是否大于或等于281;否,记录0,确认数字在250至280之间。该数字是否大于或等于266;是,记录1,确认数字在266至280之间。该数字是否大于或等于273;否,记录0,确认数字在266至272之间。该数字是否大于或等于269;否,记录0,确认数字在266至269之间。该数字是否大于或等于268;否,记录0,确认数字在266至268之间。该数字是否大于或等于267;否,记录0,确认数字为266。由此,得到逻辑判断为0100010000,将该逻辑判断作为芯片的标识信息。

[0042]

继续采用二分法,若芯片的原始标识信息为十进制数的688,则芯片的标识信息为1010110000;若第一像素结构101表示0且第二像素结构102表示1,则芯片的标识信息在芯片表面上的呈现可如图4所示意,图4是本发明实施例提供的另一种芯片的结构示意图。

[0043]

基于上述,比图1、图2以及图3可见,本发明实施例采用第一像素结构101和/或第二像素结构102呈现芯片的标识信息,其中第一像素结构101和第二像素结构102分别表示数字0和1或者1和0,相较于采用十进制数和/或字母、或者采用二维码或条形码呈现芯片标识而言,使得芯片的标识信息所用的像素结构的数量较少,从而芯片的标识信息对应的所有像素结构所占面积被降低,进而提高了芯片有效面积,也即提高了芯片的功能区cc的面积。

[0044]

本发明实施例中,第一像素结构101和第二像素结构102的具体结构、形状可以是多种,保证第一像素结构101和第二像素结构102均能够表示一种像素结构,并且第一像素结构101和第二像素结构102分别表示的像素结构相互之间可以区分即可,本发明实施例对

此不作具体限定。

[0045]

在上述技术方案的基础上,可选地,结合图3与图5,图5是图3沿剖面线aa’的剖面结构示意图,第一像素结构101或第二像素结构102包括凹槽,相应的,第二像素结构102或第一像素结构101包括芯片的表面本身。

[0046]

具体地,图5示例性示意出芯片包括层叠设置的两层金属层(111和112)和三层介质层(121、122和123),第一介质层121、第一金属层111、第二介质层122、第二金属层112以及第三介质层123由下至上依次设置,此时,第三介质层123背离第二金属层112的表面作为芯片的上表面,第一介质层111背离第一金属层111的表面作为芯片的下表面。

[0047]

图5还示例性示意出,第一像素结构101为芯片的表面,即第一像素结构101为实心结构,无需对芯片的表面进行刻蚀,而第二像素结构102为芯片表面上的凹槽,为空心结构,即对芯片的表面进行刻蚀而得到。当然,也可以是第一像素结构101为实心结构而第二像素结构102为空心结构,本实施例对此不作具体限定。另外,凹槽可以是如图5示例性示意的矩形凹槽,也可以是圆形凹槽,保证能够区分第一像素结构101和第二像素结构102即可,对此不作具体限定。

[0048]

本发明实施例中设置像素结构为芯片的表面本身或者为芯片表面的凹槽,使得第一像素结构101和第二像素结构102的结构简单,易于制作,实用性较强,耗费成本也不高。

[0049]

除此之外,可选地,本发明实施例的技术方案还可以是第一像素结构101或第二像素结构102包括凸起,相应的,第二像素结构102或第一像素结构101包括芯片的表面本身。

[0050]

其中,凸起可以是凸起的金属块,相邻的两个凸起之间形成一个凹槽结构,凹槽的底为芯片的表面本身。即具体可以是采用光刻工艺在芯片的表面形成凸起,凸起可以作为第一像素结构101或者第二像素结构102。

[0051]

本发明实施例中,第一像素结构101和第二像素结构102所占的芯片表面的面积可以相同也可以不同。

[0052]

在上述技术方案的基础上,可选地,结合图3与图5,芯片的上表面包括第一像素结构101和/或第二像素结构102;第一像素结构101在芯片的下表面的垂直投影,与第二像素结构102在芯片的下表面的垂直投影相同。这样设置,有利于使得第一像素结构101和第二像素结构102的外围轮廓相同,同时第一像素结构101和第二像素结构102所占的芯片表面的面积相同,从而有利于芯片的标识信息对应的所有像素结构所占芯片表面的面积较小,进而提高芯片的有效面积。

[0053]

在上述技术方案的基础上,可选地,结合图3与图5,第一像素结构101和/或第二像素结构102在芯片的下表面上的垂直投影面积为(1~10μm)

×

(1~10μm),也即像素结构的大小为(1~10μm)

×

(1~10μm)。这样设置,可以避免像素结构太大从而占用芯片表面的面积较大降低芯片的有效面积,还可以避免像素结构太小不能够有效地呈现芯片的标识信息。

[0054]

在上述技术方案的基础上,可选地,参考图3,在芯片的标识区bb内,芯片的表面(例如上表面)还包括边框103;第一像素结构101和第二像素结构102均设置于边框103内,边框103用于限制第一像素结构101和第二像素结构102的总数量为目标像素结构数量。边框103的形状不限于是规则矩形。

[0055]

具体地,目标像素结构数量为芯片的标识信息对应的所有像素结构的总数量,即

以目标像素结构数量可以呈现芯片的目标标识信息。设置边框103将第一像素结构101和第二像素结构102的总数量限制为目标像素结构数量,以利于基于边框103,准确地读取到边框103内由第一像素结构101和第二像素结构102所呈现的芯片的标识信息。换言之,边框103内的所有第一像素结构101和第二像素结构102才为芯片的标识信息对应的所有像素结构;边框103之外的,则不作为芯片的标识信息。这样可以避免芯片的标识信息的误读取。

[0056]

在上述技术方案的基础上,可选地,结合图3与图5,相邻两个第一像素结构101之间的间距、相邻两个第二像素结构102之间的间距以及相邻的第一像素结构101和第二像素结构102之间的间距均为零。这样设置,使得第一像素结构101和第二像素结构102紧凑排列,可以进一步降低芯片的标识信息对应的所有像素结构对芯片表面面积的占用,从而进一步提高芯片的有效面积。其中,在读取标识信息时,可以基于像素结构的面积大小来划分相邻的第一像素结构101,以及划分相邻的第二像素结构102。

[0057]

在上述技术方案的基础上,作为本发明的一种实施方式,可选地,参考图6,图6是本发明实施例提供的另一种芯片的结构示意图,标识区bb包括多个标识子区bb’;多个标识子区bb’分散在功能区cc的周围;第一像素结构101和第二像素结构102位于至少一个标识子区bb’。其中,芯片的标识信息的读取方向可预先规定。

[0058]

具体地,如图3所示例性示意,标识区bb可以是规则区域,此时功能区cc也是规则区域。当然,标识区bb也可以是不规则的,此时功能区cc也是不规则区域。继续参考图6,由多个标识子区bb’构成标识区bb,多个标识子区bb’均匀或者不均匀分散在功能区cc的周围,各标识子区bb’可以是规则的也可以是不规则的。

[0059]

基于此,本实施例的技术方案,可以是第一像素结构101和第二像素结构102位于至少一个标识子区bb’,从而可以高效利用芯片的功能区cc之外的空白区。即,在芯片的标识信息对应的第一像素结构101和第二像素结构102的总数量较多,而一个标识子区bb’不能容纳时,便可以设置在多个标识子区bb’。这样设置,不仅实现了芯片的标识信息的呈现,同时所占用的芯片的表面积较少,而且灵活、充分地利用了芯片的功能区cc之外的空白区。

[0060]

图6示例性示意出四个标识子区bb’,且图3中的标识信息0100010000对应的第一像素结构101和第二像素结构102分布在其中的两个标识子区bb’内,并且每个标识子区bb’内的第一像素结构101和第二像素结构102均设置于边框103内,该两个标识子区bb’内的第一像素结构101和第二像素结构102的总数量为芯片的标识信息对应的像素结构的总数量。通过将该两个标识子区bb’内的第一像素结构101和第二像素结构102所共同表示的标识信息0100010000,采用二分法、斐波那契查找法或者二进制转换进行解码,即可得到芯片的原始标识信息。

[0061]

可选地,参考图3以及图6,标识区bb内的所有第一像素结构101及第二像素结构102按至少一行和/或至少一列依次排布,以利于在实现芯片的标识信息的呈现,同时所占用的芯片的表面积较少的基础上,进一步灵活、充分地利用芯片的功能区cc之外的空白区。其中,每一列或者每一行的像素结构均位于对应的边框103内。如标识信息0100010000在图3中整体呈一行,且位于同一个边框内,而在图6中呈四行六列(一个标识子区bb’有两行、三列),且位于四个边框内。

[0062]

在上述技术方案的基础上,作为本发明的一种实施方式,可选地,参考图6,图6是本发明实施例提供的另一种芯片的结构示意图,在标识区bb内,芯片的表面还包括识别位

结构104,识别位结构104用于规定标识信息的读取方向。即,在芯片的表面设置第一像素结构101和第二像素结构102后,为了便于标识信息的高效、准确读取,在标识信息对应的第一位像素结构或最后一位像素结构的之前或者之后,设置识别位结构104以作为标识信息读取的起始位。识别位结构104可以是区别于第一像素结构101和第二像素结构102的圆点图形、三角形图形或者其它规则或不规则图形,保证能够规定芯片上标识信息的读取方向即可。

[0063]

本发明实施例还提供一种晶圆,晶圆包括衬底和多个如上述任意技术方案所提供的芯片;多个芯片均设置于衬底之上,各个芯片的标识信息不同;基于芯片的标识信息可以辨识芯片在晶圆上的相对位置,以及对各芯片相互之间进行区分。本发明实施例提供的晶圆与芯片,两者属于相同的发明构思,能够实现相同的技术效果,重复内容此处不再赘述。

[0064]

上述具体实施方式,并不构成对本发明保护范围的限制。本领域技术人员应该明白的是,根据设计要求和其他因素,可以进行各种修改、组合、子组合和替代。任何在本发明的精神和原则之内所作的修改、等同替换和改进等,均应包含在本发明保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1