芯片及其制备方法、电子设备与流程

本技术涉及半导体,尤其涉及一种芯片及其制备方法、电子设备。

背景技术:

1、随着半导体技术的发展,电子设备中的芯片的集成度逐渐提高,有利于实现芯片的小尺寸化和轻薄化。

2、通常,芯片中包括电阻器件,电阻器件例如包括配阻(high resistance,简称hir)层。芯片中还包括覆盖配阻层的介质层、第一接触结构和第二接触结构,第一接触结构贯穿介质层与配阻层的一端连接,第二接触结构贯穿介质层与配阻层的另一端连接。

3、然而,随着芯片的小尺寸化,芯片中配阻层的尺寸也随之减小,这给第一接触结构和第二接触结构与配阻层之间的互连带来较大的挑战,且在制备芯片的过程中,现有的工艺易造成配阻层的损伤,导致第一接触结构和第二接触结构与配阻层之间接触不良,进而导致电阻器件的阻值失准。

技术实现思路

1、本技术的一些实施例提供了一种芯片及其制备方法、电子设备,旨在提高芯片中电阻器件的阻值的准确性。

2、为达到上述目的,本技术的实施例采用如下技术方案:

3、第一方面,提供了一种芯片,该芯片可以是裸芯片,也可以是经过封装的芯片,封装的芯片中可包括一个或多个裸芯片。

4、上述芯片包括配阻层、设置于配阻层上的至少一个介质层、及多个第一接触柱和多个第二接触柱。其中,配阻层包括第一端和第二端,该第一端和第二端为配阻层沿第一方向的相对两端,第一方向平行于配阻层的延展面。多个第一接触柱贯穿至少一个介质层与第一端电连接,多个第二接触柱贯穿至少一个介质层与第二端电连接。

5、本技术的上述实施例所提供的芯片,通过设置多个第一接触柱与配阻层的第一端电连接,多个第二接触柱与配阻层的第二端电连接。基于此,在制备芯片的过程中,需要在介质层中形成多个第一接触孔和多个第二接触孔,第一接触孔用于形成第一接触柱,第二接触孔用于形成第二接触柱。

6、本技术的实施例中第一接触柱和第二接触柱均为柱状,第一接触孔和第二接触孔均为孔状,相较于长沟槽状的接触孔,第一接触孔和第二接触孔的开口面积减小,这样,在刻蚀介质层的过程中,第一接触孔和第二接触孔的刻蚀深度易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

7、在一些实施例中,多个第一接触柱呈阵列式排布,和/或,多个第二接触柱呈阵列式排布。

8、通过上述设置方式,可提高多个第一接触柱和多个第二接触柱在平面内排布的均匀性。

9、并且,在制备芯片的过程中,刻蚀介质层以形成多个第一接触孔和多个第二接触孔,然后在第一接触孔内形成第一接触柱,在第二接触孔内形成第二接触柱。因此,在多个第一接触柱呈阵列式排布,多个第二接触柱呈阵列式排布的情况下,多个第一接触孔也呈阵列式排布,多个第二接触孔也呈阵列式排布,可提高多个第一接触孔和多个第二接触孔在平面内排布的均匀性,这样,在刻蚀介质层的过程中,使第一接触孔和第二接触孔的刻蚀深度更易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

10、在一些实施例中,多个第一接触柱包括沿第一方向排列的多列,以及沿第二方向排列的多行,第一方向与第二方向相交叉。和/或,多个第二接触柱包括沿第一方向排列的多列,以及沿第二方向排列的多行,第一方向与第二方向相交叉。

11、通过上述设置方式,可进一步提高多个第一接触柱和多个第二接触柱在平面内排布的均匀性。因此,在制备芯片的过程中,可进一步提高多个第一接触孔和多个第二接触孔在平面内排布的均匀性,这样,在刻蚀介质层的过程中,使第一接触孔和第二接触孔的刻蚀深度更易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

12、在一些实施例中,沿第一方向的相邻两个第一接触柱之间的间距,与沿第二方向的相邻两个第一接触柱之间的间距相等,第一方向与第二方向相交叉。和/或,沿第一方向的相邻两个第二接触柱之间的间距,与沿第二方向的相邻两个第二接触柱之间的间距相等,第一方向与第二方向相交叉。

13、通过上述设置方式,也可进一步提高多个第一接触柱和多个第二接触柱在平面内排布的均匀性。因此,在制备芯片的过程中,也可进一步提高多个第一接触孔和多个第二接触孔在平面内排布的均匀性,这样,在刻蚀介质层的过程中,使第一接触孔和第二接触孔的刻蚀深度更易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

14、在一些实施例中,第一接触柱沿第一方向的径向尺寸为第一尺寸,第一接触柱沿第二方向的径向尺寸为第二尺寸,第一尺寸与第二尺寸相等,第一方向与第二方向相交叉。和/或,第二接触柱沿第一方向的径向尺寸为第三尺寸,第二接触柱沿第二方向的径向尺寸为第四尺寸,第三尺寸与第四尺寸相等,第一方向与第二方向相交叉。

15、通过上述设置方式,可提高第一接触柱和第二接触柱的平面尺寸的均匀性,也有利于提高多个第一接触柱和多个第二接触柱在平面内排布的均匀性。因此,在制备芯片的过程中,可提高多个第一接触孔和多个第二接触孔在平面内排布的均匀性,这样,在刻蚀介质层的过程中,使第一接触孔和第二接触孔的刻蚀深度更易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

16、在一些实施例中,多个第一接触柱包括沿第一方向排列的多列,以及沿第二方向排列的多行,第一方向与第二方向相交叉,多个第一接触柱的列数范围为2~20,多个第一接触柱的行数范围为1~20。和/或,多个第二接触柱包括沿第一方向排列的多列,以及沿第二方向排列的多行,第一方向与第二方向相交叉,多个第二接触柱的列数范围为2~20,多个第二接触柱的行数范围为1~20。

17、在一些实施例中,第一接触柱的形状为四棱柱、四棱台、圆柱、和圆台中的一种,和/或,第二接触柱的形状为四棱柱、四棱台、圆柱、和圆台中的一种。

18、在一些实施例中,至少一个介质层包括层叠设置的第一介质层和第二介质层,芯片还包括第二导电图案和第三导电图案,第二导电图案设置于第二介质层远离配阻层的一侧,多个第一接触柱的远离配阻层的一端与第二导电图案电连接,以实现配阻层与第二导电图案的互联。第三导电图案设置于第二介质层远离配阻层的一侧,多个第二接触柱的远离配阻层的一端与第三导电图案电连接,以实现配阻层与第三导电图案的互联。

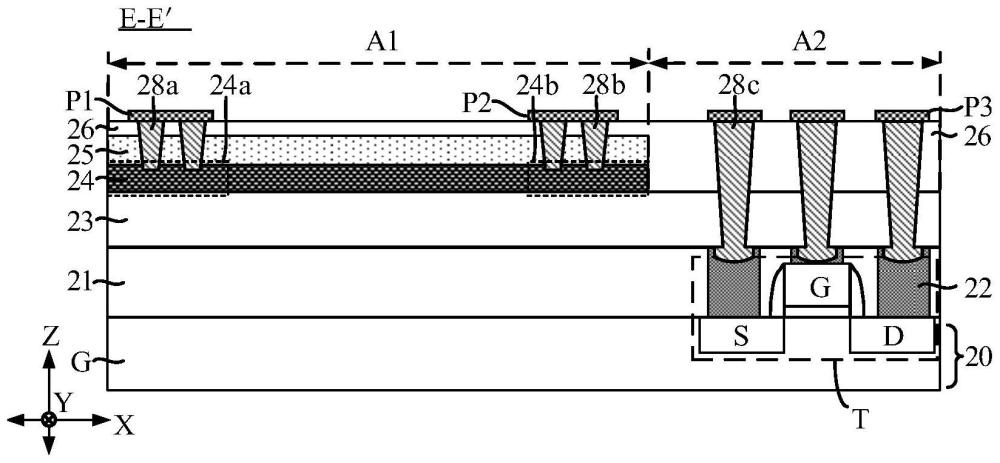

19、在一些实施例中,芯片包括配阻区和器件区,配阻层和第一介质层位于配阻区,第二介质层位于配阻区和器件区。

20、芯片还包括第一导电图案、第三介质层和第三接触柱,其中,第一导电图案位于器件区,第三介质层设置于第一导电图案上,且位于配阻区和器件区。第三介质层位于第二介质层靠近第一导电图案的一侧。第三接触柱贯穿第二介质层和第三介质层,且一端与第一导电图案电连接,以实现第一导电图案与第三接触柱的互联。

21、在一些实施例中,第一接触柱、第二接触柱和第三接触柱的材料相同,即三者可以采用同一成膜工艺制备。

22、在一些实施例中,芯片还包括第四导电图案,第四导电图案设置于第二介质层远离第一导电图案的一侧,第三接触柱远离第一导电图案的一端与第四导电图案电连接,以实现第一导电图案与第四导电图案的互联。

23、第二方面,提供了一种芯片的制备方法,该制备方法包括:形成配阻层和至少一个介质层,至少一个介质层位于配阻层上,配阻层包括第一端和第二端,第一端和第二端为配阻层沿第一方向的相对两端。在至少一个介质层中形成多个第一接触孔和多个第二接触孔,多个第一接触孔暴露第一端,多个第二接触孔暴露第二端。在第一接触孔内形成第一接触柱,并在第二接触孔内形成第二接触柱,第一接触柱与第一端电连接,第二接触柱与第二端电连接。

24、本技术的上述实施例所提供的制备方法,在介质层中形成多个第一接触孔和多个第二接触孔,然后在第一接触孔内形成第一接触柱,在第二接触孔内形成第二接触柱,第一接触柱与配阻层的第一端电连接,第二接触柱与配阻层的第二端电连接。

25、本技术的实施例中第一接触孔和第二接触孔均为孔状,相较于长沟槽状的接触孔,第一接触孔和第二接触孔的开口面积减小,这样,在刻蚀介质层的过程中,第一接触孔和第二接触孔的刻蚀深度易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

26、在一些实施例中,芯片包括配阻区和器件区。

27、形成配阻层和至少一个介质层,包括:依次形成配阻薄膜和第一介质薄膜。去除第一介质薄膜位于配阻区外的部分,及配阻薄膜位于配阻区外的部分,形成配阻层和覆盖配阻层的第一介质层。形成第二介质层,第二介质层位于配阻区和器件区,且位于第一介质层远离配阻层的一侧。

28、在一些实施例中,形成配阻层和至少一个介质层之前,还包括:依次形成第一导电图案和第三介质层,第一导电图案位于器件区,第三介质层位于配阻区和器件区。

29、在一些实施例中,形成多个第一接触孔和多个第二接触孔,包括:刻蚀第二介质层和第一介质层,形成多个第一接触孔和多个第二接触孔。在刻蚀第二介质层和第一介质层的过程中,还刻蚀第二介质层和第三介质层,形成第三接触孔,第三接触孔暴露第一导电图案。

30、上述实施例中,多个第一接触孔和多个第二接触孔均为孔状,第一接触孔和第二接触孔的开口面积减小,这样,在刻蚀第二介质层和第一介质层的过程中,第一接触孔和第二接触孔的刻蚀深度易于控制,通过控制刻蚀停止于配阻层的表面,避免配阻层因过刻蚀而体积减小,从而保证配阻层的阻值精准。

31、并且,在刻蚀第二介质层和第一介质层的过程中,还刻蚀第二介质层和第三介质层,形成第三接触孔,该第三接触孔暴露第一导电图案。

32、在一些实施例中,形成第三接触孔之后,还包括:经第三接触孔的底部,刻蚀第一导电图案,以在第一导电图案内形成空腔,第三接触孔包括与空腔相连的开口,开口在第一导电图案上的正投影,位于空腔在第一导电图案上的正投影的范围内。

33、上述实施例中,由于第一接触孔和第二接触孔的开口面积减小,在对第一导电图案进行刻蚀的过程中,可减弱甚至避免刻蚀气体或刻蚀液经由第一接触孔和第二接触孔与配阻层接触,避免配阻层因刻蚀而体积减小,从而保证配阻层的阻值精准。

34、并且,由于开口在第一导电图案上的正投影,位于空腔在第一导电图案上的正投影的范围内,第三接触孔与空腔连通形成外形类似“铆钉”的腔体,因此,在该腔体内形成第三接触柱后,第三接触柱外形也类似“铆钉”,在后续研磨的过程中,若研磨液沿第三接触柱与第三接触孔侧壁的缝隙渗入,第三接触柱的“钉帽”可起到阻挡研磨液的作用,避免研磨液接触并腐蚀第一导电图案。

35、在一些实施例中,采用选择性沉积工艺,在第一接触孔内形成第一接触柱,并在第二接触孔内形成第二接触柱的过程中,还在第三接触孔内形成第三接触柱,第三接触柱与第一导电图案电连接,选择性沉积工艺所形成的接触柱内不会形成空隙,有利于减小接触柱的电阻。

36、在一些实施例中,形成第一接触柱和第二接触柱之后,还包括:对至少一个介质层进行离子注入。

37、上述实施例中,对介质层进行离子注入,可使介质层膨胀,以减小第一接触孔、第二接触孔和第三接触孔的孔径,从而缩小相应的孔与接触柱之间的缝隙,在后续研磨工艺的过程中,可改善研磨液经孔与接触结构之间的缝隙下渗的问题,以减弱研磨液腐蚀第一导电图案和配阻层的现象。

38、并且,由于第一接触孔和第二接触孔的开口面积减小,在离子注入的过程中,减小了离子经孔与接触柱之间的缝隙进入的概率,从而避免离子注入配阻层而引起配阻层的阻值失准的问题。

39、在一些实施例中,形成第一接触柱和第二接触柱之后,还包括:依次形成保护层和牺牲层,保护层和牺牲层覆盖至少一个介质层、第一接触柱和第二接触柱。研磨牺牲层、保护层和至少一个介质层的远离配阻层一侧的部分,以暴露第一接触柱和第二接触柱的远离配阻层的端部。

40、上述实施例中,在配阻区内设置多个第一接触柱和多个第二接触柱,有利于提高配阻区的表面各处的强度均一性,从而提高配阻区的表面研磨的均一性,避免第一接触柱和第二接触柱的顶部产生“碟形”损伤,保证第一接触柱和第二接触柱的顶面平坦且完全暴露,以便于在第一接触柱和第二接触柱的上方形成导电图案后,有利于导电图案与第一接触柱和第二接触柱的稳定接触。

41、第三方面,提供了一种电子设备,提供了一种电子设备,该电子设备例如为消费性电子产品、家居式电子产品、车载式电子产品、金融终端产品、通信电子产品。该电子设备包括上述任一实施例所述的芯片,以及与芯片电连接的电路板。

42、可以理解地,本技术的上述实施例所提供的电子设备,其所能达到的有益效果可参考上文中芯片的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!