半导体结构及其形成方法与流程

1.本揭露是关于一种半导体结构及其形成方法。

背景技术:

2.半导体集成电路(integrated circuit,ic)行业经历了指数级增长。ic材料 及设计的技术进步已经产生数代ic,其中每一代比上一代具有更小且更复杂 的电路。在ic演进过程中,功能密度(即,每晶片面积的互连装置数目)通 常增大,而几何大小(即,可使用制造工艺产生的最小组件(或线路))已减 少。此种按比例缩小的过程通常通过提高生产效率及降低相关联成本来提供益 处。此种按比例缩小亦增大了处理及制造ic的复杂性。

技术实现要素:

3.本揭露的一个态样是关于一种半导体结构。半导体结构包括一基板及在基 板之上的一第一超晶格结构及一第二超晶格结构。第二超晶格结构安置在第一 超晶格结构之上。第一超晶格结构及第二超晶格结构中的每一者包括垂直堆叠 的交替的一第一半导体材料的第一纳米片及不同于第一半导体材料的一第二 半导体材料的第二纳米片。半导体进一步包括围绕第一超晶格结构及第二超晶 格结构中的每一者的一通道区的栅极堆叠及在栅极堆叠的相对侧上的源极/漏 极结构。源极/漏极结构接触第一超晶格结构及第二超晶格结构的侧壁。

4.本揭露的另一态样是关于一种用于形成一半导体结构的方法。方法包括在 一基板上形成含有垂直堆叠的交替超晶格层及牺牲层的一鳍结构。超晶格层中 的每一者包括交替的一第一半导体材料的第一层及不同于第一半导体材料的 一第二半导体材料的第二层。方法进一步包括形成横跨鳍结构的一部分的一牺 牲栅极结构。牺牲栅极结构包括一牺牲栅极堆叠及位于牺牲栅极堆叠的侧壁上 的栅极间隔物。方法进一步包括:移除鳍结构的未由牺牲栅极结构覆盖的部分 以提供包含垂直堆叠的交替超晶格结构及牺牲结构的一鳍区段;在鳍区段的端 壁上形成源极/漏极结构;在源极/漏极结构上沉积一介电质层;移除牺牲栅极 堆叠以提供一栅极腔体;移除牺牲结构;以及形成围绕超晶格结构中的每一者 的一栅极堆叠。

5.本揭露的又一态样是关于一种半导体结构。半导体结构包括自一基板向上 延伸的一超晶格结构。超晶格结构包括垂直于基板对准的交替的一第一半导体 材料的第一纳米片及一第二半导体材料的第二纳米片。第一半导体材料不同于 第二半导体材料。半导体结构进一步包括横向接触超晶格结构的一通道区的一 栅极结构及围绕超晶格结构的一顶部部分的一掺杂磊晶区。

附图说明

6.当结合附图阅读时,根据以下详细描述可最佳地理解本揭露的态样。注意, 根据行业中的标准实务,各种特征未按比例绘制。实际上,为了论述的清楚起 见,可任意地增大

或减小各种特征的尺寸。

7.图1为说明根据一些实施例的形成具有垂直堆叠的超晶格通道的半导体 结构的实例方法的处理流程图;

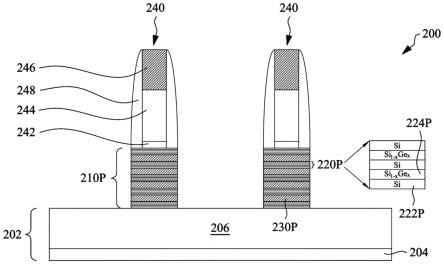

8.图2a至图2k为根据一些实施例的在图1的制造工艺的各个阶段的半导 体结构的横截面图;

9.图3为说明根据一些实施例的形成具有横向超晶格通道的半导体结构的 实例方法的处理流程图;

10.图4a至图4k为根据一些实施例的在图3的制造工艺的各个阶段的半导 体结构的横截面图。

11.【符号说明】

12.100:方法

13.102:操作

14.104:操作

15.106:操作

16.108:操作

17.110:操作

18.112:操作

19.114:操作

20.116:操作

21.118:操作

22.120:操作

23.122:操作

24.200:半导体结构

25.202:基板

26.204:基础基板

27.206:绝缘体层

28.210:多层堆叠

29.210f:鳍结构

30.210p:鳍区段

31.220:超晶格层

32.220p:超晶格结构

33.222:第一层

34.222p:第一纳米片

35.224:第二层

36.224p:第二纳米片

37.230:牺牲层

38.230p:牺牲结构

39.240:牺牲栅极结构

40.242:牺牲栅极堆叠

41.244:牺牲栅极导体

42.246:牺牲栅极盖

43.248:栅极间隔物

44.250:凹部

45.252:内部间隔物

46.254:源极/漏极结构

47.260:ild层

48.262:栅极腔体

49.264:纳米结构

50.266:间隙

51.268:凹部

52.272:栅极堆叠

53.274:栅极堆叠

54.300:方法

55.302:操作

56.304:操作

57.306:操作

58.308:操作

59.310:操作

60.312:操作

61.314:操作

62.316:操作

63.318:操作

64.320:操作

65.322:操作

66.400:半导体结构

67.402:基板

68.402a:掺杂半导体区

69.410:第一磊晶层

70.420:心轴结构

71.422:间隔物

72.430:超晶格结构

73.432a:第一纳米片

74.432b:第三纳米片

75.434a:第二纳米片

76.440:绝缘体层

77.450:栅极结构

78.452:栅极介电质层

79.452p:栅极介电质

80.454:栅电极层

81.454p:栅电极

82.460:介电间隔物层

83.470:掺杂磊晶区

具体实施方式

84.以下揭示内容提供用于实施所提供主题的不同特征的许多不同实施例或 实例。下文描述组件及配置的特定实例以简化本揭露。当然,此等仅为实例而 非限制性的。举例而言,在下文的描述中,在第二特征之上或上的第一特征的 形成可包括其中第一特征与第二特征直接接触地形成的实施例,且亦可包括其 中在第一特征与第二特征之间形成额外特征,使得第一特征与第二特征可不直 接接触的实施例。另外,本揭露可在各个实例中重复参考数字及/或字母。此 重复是出于简单及清楚的目的,且其本身并不指示所论述的各种实施例及/或 组态之间的关系。

85.此外,为了便于描述,在本文中可使用诸如“下方”、“在...下方”、“下 部”、“在上方”、“上部”等的空间相对术语,以便于描述一个元件或特征 与另一(些)元件或特征的关系,如图所示。除了在图中描述的定向之外,空 间相对术语亦意欲涵盖装置在使用或操作中的不同定向。设备可以其他方式定 向(旋转90度或以其他定向),且本文中使用的空间相对描述语可同样地被 相应地解释。

86.随着半导体行业发展至纳米技术节点以追求更高的装置密度、更高的效能 及更低的成本,来自制造及设计问题的挑战已导致三维设计的发展,诸如栅极 全包围(gate-all-around,gaa)场效晶体管(field effect transistor,fet)。 在gaa fet中,栅极环绕在通道周围。通过栅极在通道上的全包围式覆盖, 可达成更佳的栅极控制及更佳的短通道效能。

87.然而,当例如ge或sige的单一半导体材料的纳米片用作gaa fet中的 通道时,由于纳米片上存在大量表面缺陷,gaa fet会遭受低载流子迁移率 及高漏电流。此外,随着通道尺寸不断减小以实现更佳栅极控制,由ge或sige 制成的纳米片通道不具备足够的机械强度,且在gaa fet的制造期间容易断 裂。

88.在本揭露的实施例中,为了最小化表面缺陷且增大通道的机械强度,构建 具有作为通道的超晶格结构的gaa fet。超晶格结构包括交替堆叠的不同半 导体材料的纳米片,平行或垂直于基板而对准。控制纳米片的厚度,以减少表 面缺陷且增大所得超晶格结构的机械强度。因此,超晶格结构有助于提高载流 子迁移率且减少漏电流。结果,装置效能得以提高。

89.图1为根据一些实施例的用于制造半导体结构200的方法100的流程图。 图2a至图2k为根据一些实施例的在方法100的各个阶段的半导体结构200 的横截面图。下文参考半导体结构200详细论述方法100。该流程图仅说明半 导体结构200的整个制造工艺的相关部分。可理解,可在图1所示的操作之前、 期间及之后提供额外的操作,且对于该方法的额外实施例,可替换或消除下文 描述的操作中的一些。操作/过程的次序可为可互换的。

90.在操作102处,根据一些实施例,方法100(图1)在基板202上形成多 层堆叠210。图2a为根据一些实施例的在基板202上形成多层堆叠210之后 的半导体结构200的横截面图。

91.参考图2a,基板202包括基础基板204及绝缘体层206。基板202可由 绝缘体上半导体(semiconductor-on-insulator,soi)基板或整个包括体半导体 材料的体半导体基板形成。在一些实施例中,且如图2a所示,基板202由soi 基板形成,自下至上包括基础基板204、绝缘体层206及构成多层堆叠210的 最底层的顶部半导体层。在一些其他实施例中,且当基板202由体半导体基板 形成时,体半导体基板的上部部分构成多层堆叠210的最底层。

92.基础基板204为上覆结构提供机械支撑,诸如内埋绝缘体层206及多层堆 叠210。在一些实施例中,基础基板204可包括:iv族半导体材料,诸如硅(si)、 锗(ge)、硅锗(sige)、碳掺杂硅(sic)、硅锗碳(sigec);或iii-v族 化合物半导体,诸如砷化镓(gaas)、磷化镓(gap)、磷化铟(inp)、砷 化铟(inas)、锑化铟(insb)、磷化砷化镓(gaasp),砷化铝铟(alinas)、 砷化铝镓(algaas)、砷化镓铟(gainas)、磷化镓铟(gainp)或磷化砷化 铟镓(gainasp)。在一些其他实施例中,基础基板204包括绝缘材料,诸如 玻璃。

93.绝缘体层206安置在基础基板204上。绝缘体层206将基础基板204与顶 部半导体层彼此电隔离。在一些实施例中,绝缘体层206包括介电材料,诸如 二氧化硅、氮化硅、氮氧化硅、氮化硼或其组合。在一些实施例中,内埋绝缘 体层206是通过沉积工艺形成,诸如化学气相沉积(chemical vapor deposition, cvd)、电浆增强化学气相沉积(plasma enhanced chemical vapor deposition, pecvd)或物理气相沉积(physical vapor deposition,pvd)。在一些其他实 施例中,绝缘体层206是使用热生长工艺(诸如热氧化)以转换基础基板204 的表面部分来形成。在一些另外的实施例中,绝缘体层206是通过将氧原子植 入至体半导体基板,随后对体半导体基板进行退火而形成。

94.顶部半导体层可包括如上文所提及用于基础基板204的任何半导体材料。 举例而言,在一些实施例中,顶部半导体层包括si、ge、sige、sic、sigec; 或iii-v族化合物半导体,包括gaas、gap、inp、inas、insb、gaasp、alinas、 algaas、gainas、gainp或gainasp。在一些实施例中,顶部半导体层由单 晶半导体材料组成,诸如单晶si。在一些实施例中,顶部半导体层是通过诸如 cvd或pecvd的沉积工艺形成,或其可表示体半导体基板的最上部分,其 中用于形成绝缘体层206的氧原子被植入其中。或者,顶部半导体层可最初形 成在载体基板上,接着自绝缘体层206侧接合至基板202。顶部半导体层可减 薄至所需厚度,以便用作多层堆叠210的最底层,例如通过平坦化、研磨、蚀 刻或氧化继之以氧化物蚀刻。顶部半导体层可减薄至范围自约1nm至约10nm 的厚度。在一些其他实施例中,顶部半导体层的厚度可在约3nm至约5nm的 范围内。

95.多层堆叠210安置在基板202上。在一些实施例中,多层堆叠210包括多 个垂直堆叠的超晶格层220及将超晶格层220彼此分开的牺牲层230。应注意, 尽管图示五个超晶格层220,但可设想任何数目个超晶格层220。

96.在一些实施例中,超晶格层220中的每一者包括第一半导体材料的第一层 222与第二半导体材料的第二层224的交替层。第二半导体材料不同于第一半 导体材料。分别用于第一层222及第二层224中的不同材料允许第一层222 与第二层224之间的不同应变以便提高载流子迁移率。在一些实施例中,第一 层222与第二层224独立地由iv族半导体材料构成,诸如si、ge、sige、sigec、 sic等;iii-v族化合物半导体材料,诸如gaas、gap、gaasp、alinas、algaas、 gainas、inas、gainp、inp、insb、gainasp等。在一些实施例中,第一层222 由si构成,而第二层224由sige或ge构成。调整sige中ge的中心化以控 制载流子迁移率及

蚀刻选择性。在一些实施例中,sige中ge的浓度按原子重 量%计可为约1%至约90%。在某些实施例中,sige中ge的浓度按原子重量% 计可为约20%至约40%。若ge浓度过高,则sige层可能存在大量缺陷,导 致载流子能力低下。若ge浓度过低,则sige层可能不具有相对于牺牲层足 够的蚀刻选择性。

97.每一超晶格层220可包括任意数目个第一层222(例如si层)及任意数目 个第二层224(例如sige层)。在一些实施例中,且如图2a所说明,超晶格 层220包括三个第一层222(例如si层)及两个第二层224(例如sige层)。

98.在一些实施例中,牺牲层230包括不同于第一半导体材料及第二半导体材 料的第三半导体材料,以使得可针对第一层222及第二层224选择性地移除牺 牲层230。第一层222包括si,且第二层224包括sige,牺牲层230可包括 ge。在一些实施例中,在第一层222包括si且第二层224包括ge的情况下, 牺牲层230可包括sige。

99.在一些实施例中,第一层222(例如,si层)、第二层224(例如,sige 层)及牺牲层230(例如,ge层)中的每一者利用磊晶生长(或沉积)工艺 在其下方的层上生长。术语“磊晶生长及/或沉积”及“磊晶形成及/或生长

”ꢀ

意谓在半导体材料的沉积表面上生长半导体材料,其中正在生长的半导体材料 具有与沉积表面的半导体材料相同的晶体特性。在磊晶沉积工艺中,控制由源 气体提供的化学反应物,且设定系统参数,以使得沉积原子以足够的能量到达 半导体材料的沉积表面,以在表面上移动且使其自身定向至沉积表面的原子的 晶体配置。因此,通过磊晶沉积工艺形成的磊晶半导体材料具有与其所形成于 的沉积表面相同的晶体特性。举例而言,沉积在{100}晶体表面上的磊晶半导 体材料将呈现{100}定向。因此,多层堆叠210中的每一层与下方的半导体材 料层具有磊晶关系,即晶体定向相同。因此,当soi基板的顶部半导体层或体 半导体基板的上部部分(即最底部的第一层222)是由单晶半导体材料构成时, 在其上形成的多层堆叠210中的第一层222及第二层224以及牺牲层230中的 每一者是由单晶半导体材料构成。在一些实施例中,多层堆叠210中的第一层 222及第二层224以及牺牲层230中的每一者可通过例如快速热化学气相沉积 (rapid thermal chemical vapor deposition,rtcvd)、低能量电浆沉积 (low-energy plasma deposition,lepd)、超高真空化学气相沉积(ultra-highvacuum chemical vapor deposition,uhvcvd)、常压化学气相沉积(atmosphericpressure chemical vapor deposition,apcvd)、分子束磊晶(molecular beamepitaxy,mbe)或金属有机cvd(metal-organic cvd,mocvd)形成。在一 些实施例中,在多个沉积之间不破坏真空的情况下执行多层堆叠210中的各个 层222、224、230的磊晶生长。在一些实施例中,在各种沉积中的任一者之间 破坏真空。第一层222及第二层224以及牺牲层230中的每一者的厚度被控制 为小于对应的临界厚度,高于该临界厚度便会发生缺陷。多层堆叠210中的特 定层的临界厚度取决于用于特定层及下方层的材料选择。在一些实施例中,第 一层222、第二层224及牺牲层230中的每一者的厚度范围自约1nm至约10nm。 若第一层222、第二层224及牺牲层230中的每一者的厚度过大,则缺陷可能 形成于各别第一层222、第二层224及牺牲层230中。若第一层222、第二层 224及牺牲层230中的每一者的厚度过小,则各别第一层222、第二层224及 牺牲层230可能不具有用于装置制造的足够机械强度。在一些实施例中,第一 层222、第二层224及牺牲层230中的每一者的厚度范围自约3nm至约5nm。

100.在操作104处,根据一些实施例,方法100(图1)蚀刻多层堆叠210以 形成多个鳍结

构210f。图2b为根据一些实施例的在蚀刻多层堆叠210以形成 多个鳍结构210f之后的图2a的半导体结构200的横截面图。

101.在图2b中,鳍结构210f自基板202向上延伸,其中超晶格层220平行 于基板202对准。应注意,尽管说明五个鳍结构210f,但在本揭露中可设想 任何数目个鳍结构210f。

102.可通过任何合适的方法蚀刻多层堆叠210以提供鳍结构210f。举例而言, 在一些实施例中,鳍结构210f可通过首先在多层堆叠210的最上表面之上施 加光阻剂层且光微影图案化光阻剂层以提供覆盖将形成鳍结构210f的区域的 图案化光阻剂层来形成。接着使用图案化光阻剂层作为蚀刻遮罩通过非等相性 蚀刻来蚀刻多层堆叠210。在一些实施例中,非等相性蚀刻为诸如反应离子蚀 刻(reactive ion etch,rie)的干式蚀刻、湿式蚀刻或其组合。在一些实施例 中,蚀刻在绝缘体层206的表面处停止。在一些实施例中,蚀刻进行至绝缘体 层206中。在鳍结构210f形成之后,利用诸如灰化的抗蚀剂剥离工艺移除图 案化光阻剂层。

103.可使用两个或更多个光微影工艺,包括双重图案化或多重图案化工艺来图 案化多层堆叠210。通常,双重图案化或多重图案化工艺组合光微影及自对准 工艺,从而允许产生具有例如比原本使用单一直接光微影工艺可获得的间距更 小的间距的图案。

104.或者,可利用侧壁影像转印(sidewall image transfer,sit)工艺来图案化 多层堆叠210。举例而言,在一些实施例中,牺牲层形成在多层堆叠210之上, 且使用光微影工艺图案化。使用自对准工艺在图案化牺牲层旁边形成间隔物。 接着移除牺牲层,且接着可使用剩余的间隔物来图案化多层堆叠210。

105.在操作106处,根据一些实施例,方法100(图1)在鳍结构210f之上形 成多个牺牲栅极结构240。图2c为根据一些实施例的在鳍结构210f之上形成 多个牺牲栅极结构240之后的图2b的半导体结构200的横截面图。

106.参考图2c,牺牲栅极结构240中的每一者包括横跨对应鳍结构210f的一 部分的牺牲栅极堆叠(242、244、246)及在牺牲栅极堆叠(242、244、246) 的侧壁上的栅极间隔物248。“横跨”意谓在鳍结构的顶部且沿着其侧壁形成 牺牲栅极堆叠。本文使用的术语“牺牲栅极堆叠”是指用于随后形成的栅极堆 叠的占位结构,其用于经由电场或磁场控制半导体装置的输出电流(即,通道 中的载流子流动)。应注意,尽管说明两个牺牲栅极结构,但在本揭露中可设 想任何数目个牺牲栅极结构。

107.牺牲栅极堆叠(242、244、246)中的每一者自下至上包括牺牲栅极介电 质242、牺牲栅极导体244及牺牲栅极盖246。在一些实施例中,省略牺牲栅 极介电质242。在一些实施例中,通过首先在鳍结构210f及基板202之上提 供自底部至顶部包括牺牲栅极介电质层(若存在牺牲栅极介电质242)、牺牲 栅极导体层及牺牲栅极盖层的牺牲材料堆叠(未展示)来形成牺牲栅极堆叠 (242、244、246),且随后图案化牺牲材料堆叠。

108.若存在,则在一些实施例中,牺牲栅极介电质层包括氧化硅、氮化硅或氮 氧化硅。在一些实施例中,牺牲栅极介电质层是利用诸如cvd或pvd的沉积 工艺形成。在一些实施例中,通过利用热氧化或氮化来转化鳍结构210f的表 面部分来形成牺牲栅极介电质层。

109.在一些实施例中,牺牲栅极导体层包括多晶硅。在一些实施例中,牺牲栅 极导体层是利用诸如cvd或pecvd的沉积工艺形成。

110.在一些实施例中,牺牲栅极盖层包括诸如氧化物、氮化物或氮氧化物的介 电材

料。举例而言,在一些实施例中,牺牲栅极盖层包括氮化硅。在一些实施 例中,牺牲栅极盖层是利用诸如cvd或pecvd的沉积工艺形成。

111.在一些实施例中,牺牲栅极材料堆叠通过光微影及蚀刻而图案化。举例而 言,光阻剂层(未展示)施加在牺牲材料堆叠的最上表面之上,且通过光微影 曝光及显影而经光微影图案化。通过至少一种非等相性蚀刻将光阻剂层中的图 案依次转印至牺牲材料堆叠中。非等相性蚀刻为例如rie的干式蚀刻、湿式蚀 刻或其组合。若未完全消耗掉,则例如通过灰化移除在形成牺牲栅极堆叠(242、 244、246)之后剩余的光阻剂层。

112.在一些实施例中,栅极间隔物248包括介电材料,诸如氧化物、氮化物、 氮氧化物或其组合。在一些实施例中,栅极间隔物248包括氮化硅。在一些实 施例中,栅极间隔物248是通过首先在牺牲栅极堆叠(242、244、246)、鳍 结构210f及基板202的曝露表面上沉积共形栅极间隔物材料层(未展示), 接着蚀刻栅极间隔材料层以移除栅极间隔材料层的水平部分而形成。在一些实 施例中,例如通过cvd、pecvd或原子层沉积(atomic layer deposition,ald) 来沉积栅极间隔物材料层。在一些实施例中,栅极间隔物材料层通过诸如rie 的干式蚀刻来蚀刻。存在于牺牲栅极堆叠(242、244、246)的侧壁上的栅极 间隔物材料层的垂直部分构成栅极间隔物248。

113.在操作108处,根据一些实施例,方法100(图1)蚀刻鳍结构210f以形 成多个鳍区段210p。图2d为根据一些实施例的在形成多个鳍区段210p之后 的图2c的半导体结构200的横截面图。

114.参考图2d,鳍结构210f的未由牺牲栅极结构240覆盖的部分经移除以在 牺牲栅极结构240下方提供鳍区段210p。鳍区段210p中的每一者包括交替堆 叠的超晶格结构220p(其为超晶格层220的剩余部分)及牺牲结构230p(其 为对应鳍结构210f中的牺牲层230在蚀刻之后的剩余部分)。超晶格结构220p 中的每一者包括交替的第一纳米片222p(其为第一层222的剩余部分)及第 二纳米片(其为第二层224在蚀刻之后的剩余部分)。

115.在一些实施例中,使用非等相性蚀刻移除鳍结构210f的由牺牲栅极结构 240曝露的部分,该非等相性蚀刻蚀刻提供各别第一层222及第二层224的半 导体材料及提供牺牲层230的材料,而实质上不影响周围结构,包括基板202、 牺牲栅极盖246及栅极间隔物248。在一些实施例中,非等相性蚀刻为干式蚀 刻,诸如rie。在蚀刻之后,鳍区段210p的侧壁(即超晶格结构220p及牺牲 结构230p的侧壁)与牺牲栅极结构240的侧壁(即栅极间隔物248的侧壁) 实质上对准。

116.在操作110处,方法100(图1)在鳍区段210p中形成凹部250。图2e 为根据一些实施例的在鳍区段210p中形成凹部250之后的图2d的半导体结 构200的横截面图。

117.参考图2e,例如通过横向蚀刻来蚀刻栅极间隔物248下方的鳍区段210p 中的每一牺牲结构230p的端部以形成凹部250。横向蚀刻相对于在超晶格结 构220p中提供各别第一纳米片222p及第二纳米片224p的半导体材料及提供 基板202、牺牲栅极盖246及栅极间隔物248的介电材料选择性地移除提供牺 牲结构230p的第三半导体材料。在一些实施例中,执行等相性蚀刻,诸如湿 式蚀刻。在一些实施例中,过氧化氢(即h2o2)用于选择性地底切牺牲结构 230p。横向蚀刻经控制以使得凹部250的横向尺寸不大于栅极间隔物248的宽 度。

118.在操作112处,方法100(图1)在凹部250中形成内部间隔物252。图 2f为根据一些实施例的在凹部250中形成内部间隔物252之后的图2e的半导 体结构200的横截面图。

119.参考图2f,形成内部间隔物252以填充凹部250。内部间隔物252中的每 一者具有与对应栅极间隔物248的外侧壁垂直对准的外侧壁。在一些实施例中, 内部间隔物252包括介电材料,诸如氮化硅、碳氮化硅或氧氮化硅。

120.可通过使用诸如cvd或ald的合适共形沉积方法在半导体结构200的 曝露表面上沉积内部间隔物层来形成内部间隔物252。继续共形沉积工艺,直 至凹部250由内部间隔物层填充及夹断。执行蚀刻工艺,诸如非等相性蚀刻, 以移除内部间隔物层的安置在鳍区段210p中的凹部250外部的部分。非等相 性蚀刻可为诸如rie的干式蚀刻或湿式蚀刻。内部间隔物层的剩余部分(例如, 安置在鳍区段210p中的凹部250内部的部分)形成内部间隔物252。

121.在操作114处,方法100(图1)在鳍区段210p的曝露部分上形成源极/ 漏极结构254。图2g为根据一些实施例的在鳍区段210p的曝露部分上形成源 极/漏极结构254之后的图2f的半导体结构200的横截面图。

122.参考图2g,源极/漏极结构254形成于牺牲栅极结构240的相对侧上。源 极/漏极结构254为高掺杂半导体区。在一些实施例中,源极/漏极结构254具 有自约1

×

10

19

原子/cm3至约1

×

10

22

原子/cm3的掺杂剂浓度,但亦可设想更小 或更大的掺杂剂浓度。

123.源极/漏极结构254允许源极/漏极结构254在fet通道中施加应力。对于 n型及p型fet,用于源极/漏极结构254的材料可不同,使得一种类型的材料 用于n型fet以在通道中施加拉伸应力,而另一种类型的材料用于p型fet 以在通道中施加压缩应力。举例而言,可使用sip或sic来形成n型fet,且 可使用sige或ge来形成p型fet。然而,可使用任何合适的材料。对于p 型fet,源极/漏极结构254掺杂有p型掺杂剂,而对于n型fet,源极/漏极 结构254掺杂有n型掺杂剂。p型掺杂剂的实例包括但不限于硼(b)、铝(al)、 镓(ga)或铟(in)。n型掺杂剂的实例包括但不限于磷(p)、砷(as)或 锑(sb)。在一些实施例中,源极/漏极结构254包括用于n型fe的掺磷sic。 在一些实施例中,源极/漏极结构254包括用于p型fet的掺硼sige。

124.在一些实施例中,源极/漏极结构254可通过自曝露的半导体表面(诸如 超晶格结构220p中的第一纳米片222p及第二纳米片224p的表面)而非自介 电表面(诸如绝缘体层206、牺牲栅极盖246、栅极间隔物248及内部间隔物 252的表面)磊晶生长半导体材料而形成。在一些实施例中,当存在多个鳍区 段210p时,磊晶生长工艺继续,直至所沉积的半导体材料与相邻的鳍区段210p 合并。

125.提供源极/漏极结构254的半导体材料可沉积为本征半导体材料,或可用 原位掺杂来沉积。若半导体材料沉积为本征半导体材料,则源极/漏极结构254 可随后利用离子植入、气相掺杂或掺杂剂自牺牲掺杂剂源材料的向外扩散来掺 杂(异位)。

126.在一些实施例中,在形成源极/漏极结构254之后及/或在随后的掺杂工艺 之后,可进一步对源极/漏极结构254进行退火工艺以激活源极/漏极结构254 中的掺杂剂。在一些实施例中,源极/漏极结构254中的掺杂剂是通过热退火 工艺激活,包括快速热退火工艺、激光退火工艺或炉退火工艺。

127.在操作116处,根据一些实施例,方法100(图1)在基板202及源极/ 漏极结构254之上沉积层间介电质(interlevel dielectric,ild)层260。图2h 为根据一些实施例的在基板202及源极/漏极结构254之上沉积ild层260之 后的图2g的半导体结构200的横截面图。

128.参考图2h,ild层260经沉积以填充牺牲栅极结构240之间的空间。在 一些实施例中,ild层260包括氧化硅。或者,在一些实施例中,ild层260 包括介电常数(k)小于4的低k介电材料。在一些实施例中,低k介电材料 具有约1.2至约3.5的介电常数。在一些实施例中,ild层260包括由以下各 者形成的氧化硅:正硅酸四乙酯(tetraethylorthosilicate,teos)氧化物、未 掺杂硅酸盐玻璃或掺杂硅酸盐玻璃,诸如硼磷硅酸盐玻璃(borophosphosilicateglass,bpsg)、氟硅玻璃(fluorosilica glass,fsg)、磷硅酸盐玻璃(phosphosilicateglass,psg)、掺硼硅玻璃(boron doped silicon glass,bsg)及/或其他合适 的介电材料。在一些实施例中,ild层260是通过cvd、pecvd、pvd或旋 涂而沉积。在一些实施例中,ild层260经沉积以具有在牺牲栅极结构240的 最上表面(例如,牺牲栅极盖246的顶表面)上方的顶表面。ild层260随后 经平坦化,例如通过cmp及/或使用牺牲栅极盖246作为抛光及/或蚀刻停止 的凹部蚀刻。在平坦化之后,ild层260具有与牺牲栅极结构240的最上表面 实质上共面的顶表面。

129.在操作118处,根据一些实施例,方法100(图1)移除牺牲栅极堆叠(242、 244、246)以提供栅极腔体262。图2i为根据一些实施例的在移除牺牲栅极堆 叠(242、244、246)以提供栅极腔体262之后的图2h的半导体结构200的 横截面图。

130.参考图2i,通过至少一种蚀刻相对于提供超晶格结构220p及牺牲结构 230p的各别第一纳米片222p及第二纳米片224p的半导体材料及提供各别栅 极间隔物248、内部间隔物252及ild层260的介电材料选择性地移除牺牲栅 极堆叠(242、244、246)的各别组件。在一些实施例中,该至少一种蚀刻为 诸如rie的干式蚀刻、诸如氨蚀刻的湿式蚀刻或其组合。每一栅极腔体262 占据对应牺牲栅极堆叠(242、244、246)被移除的体积且由对应栅极间隔物 248的内侧壁横向限制。在移除牺牲栅极堆叠(242、244、246)之后,包括 超晶格结构220p及牺牲结构230p的鳍区段210p中的各种组件的侧壁由栅极 腔体262实体曝露。

131.在操作120处,根据一些实施例,方法100(图1)形成多个纳米结构264, 每一纳米结构包括多个垂直堆叠的超晶格结构220p。图2j为根据一些实施例 的在形成各自包括多个垂直堆叠的超晶格结构220p的多个纳米结构264之后 的图2i的半导体结构200的横截面图。

132.参考图2j,纳米结构264可通过移除鳍区段210p中的牺牲结构230p来 形成。在一些实施例中,通过蚀刻工艺移除牺牲结构230p。在一些实施例中, 该蚀刻为相对于超晶格结构220p选择性地移除牺牲结构230p的等相性蚀刻。 牺牲结构230p的移除在超晶格结构220p之间形成间隙266。间隙266中的每 一者占据对应牺牲结构230p被移除的体积且由对应内部间隔物252横向限制。 在每一纳米结构264内,垂直堆叠的超晶格结构220p通过对应间隙266彼此 间隔开。

133.随后,执行另一蚀刻工艺以蚀刻绝缘体层206的部分。蚀刻工艺形成凹部 268,使得纳米结构264中的最底部超晶格结构220p可悬浮在基板202之上。 在一些实施例中,蚀刻工艺为等相性蚀刻,其可为诸如rie的干式蚀刻或湿式 蚀刻。蚀刻移除绝缘体层206,而实质上不影响超晶格结构220p。

134.在操作122处,方法100(图1)在各别纳米结构264之上形成多个栅极 堆叠(272、274)。图2k为根据一些实施例的在各别纳米结构264之上形成 多个栅极堆叠(272、274)之后的图2i的半导体结构200的横截面图。

135.参考图2k,栅极堆叠(272、274)中的每一者形成于对应栅极腔体262、 对应纳米结构264中的相邻超晶格结构220p之间的间隙266及最底部超晶格 结构220p与基板202之间的凹部268内。栅极堆叠(272、274)中的每一者 环绕对应纳米结构264中的垂直堆叠的超晶格结构220p,从而形成栅极全包 围(gate all around,gaa)fet。在一些实施例中,栅极堆叠(272、274)中 的每一者包括在对应纳米结构264中的超晶格结构220p的曝露表面之上的栅 极介电质272及在栅极介电质272之上的栅电极274。栅极堆叠(272、274) 及横向围绕栅极堆叠(272、274)的对应栅极间隔物248共同界定栅极结构(272、 274、248)。

136.栅极堆叠(272、274)中的每一者包括在对应栅极腔体262内的第一部分 及在对应间隙266及凹部268内的第二部分。在栅极腔体262中,栅极介电质 272为u形的,具有与对应纳米结构264中的最上部超晶格结构220p的上表 面直接接触的水平部分及位于横向围绕栅极腔体262的栅极间隔物248的曝露 侧壁上的垂直部分。在间隙266及凹部268内,栅极介电质272围绕栅电极274。

137.在一些实施例中,栅极介电质272包括介电常数大于氧化硅的高k介电材 料。例示性高k介电材料包括但不限于氧化铪(hfo2)、氧化锆(zro2)、氧 化镧(la2o3)、氧化铝(al2o3)、氧化钛(tio2)、氧化钛锶(srtio3)、 氧化铝镧(laalo3)及氧化钇(y2o3)。在一些实施例中,形成包含不同栅 极介电材料(例如氧化硅及高k栅极介电质)的多层栅极介电结构。在一些实 施例中,栅电极274包括导电金属,诸如钨(w)、铜(cu)、铝(al)、钴 (co)或其合金。

138.为了形成栅极堆叠(272、274),在ild层260的曝露表面、栅极腔体 262、间隙266及凹部268之上沉积栅极介电质层。在一些实施例中,栅极介 电质层是通过诸如cvd或ald合适共形沉积工艺的沉积。接着在栅极介电 质层之上沉积导电材料层以填充栅极腔体体262、间隙266及凹部268。在一 些实施例中,导电材料层是通过cvd、pecvd或pvd沉积。执行平坦化工 艺,诸如cmp,以自介电质层的顶表面移除导电材料层及栅极介电质层的部 分。栅极腔体262、间隙266及凹部268内的导电材料层的剩余部分构成栅电 极274,且栅极腔体262、间隙266、且凹部268内的栅极介电质层的剩余部 分构成栅极介电质272。

139.由此形成gaa fet。gaa fet中的每一者包括多个垂直堆叠且垂直间隔 开的超晶格结构220p、环绕在多个垂直堆叠且垂直间隔开的超晶格结构220p 周围的栅极堆叠(272、274),及在栅极堆叠的相对侧上的源极/漏极结构。 多个垂直堆叠且垂直间隔开的超晶格结构220p中的每一者包括交替的第一半 导体材料的第一纳米片222p及不同于第一半导体材料的第二半导体材料的第 二纳米片224p。与使用单一半导体材料的纳米片作为gaa fet的通道相比, 使用包含不同半导体材料的纳米片的超晶格结构作为gaa fet中的通道有助 于提高载流子迁移率,且由于超晶格结构中的表面缺陷减少而减少漏电流。结 果,装置效能得到提高。

140.包括多个垂直对准的半导体纳米结构(例如,纳米片)作为通道的垂直 gaa fet已经开发,以在上覆基板的小布局区域中实现大的有效导电宽度。 典型的垂直gaa fet使得能够经由通过栅极介电质及栅电极对半导体纳米结 构的通道区的完整包围来增强对沿半导体纳米结构纵向方向的电荷载流子的 控制。由于通道区由栅电极包围,垂直gaa fet具有减小的短通道效应,从 而可减小源极/漏极结构对通道区电场的影响。在本揭露的实施例中,形成具 有垂直对准超晶格结构作为fet通道的垂直fet以进一步提高装置效能。

141.图3为根据一些实施例的用于制造半导体结构400的方法300的流程图。 图4a至图4j为根据一些实施例的在方法300的各个阶段的半导体结构400 的横截面图。下文参考半导体结构400详细论述方法300。该流程图仅说明半 导体结构400的整个制造工艺的相关部分。可理解,可在图3所示的操作之前、 期间及之后提供额外的操作,且对于该方法的额外实施例,可替换或消除下文 描述的操作中的一些。操作/过程的次序可为可互换的。

142.在操作302处,根据一些实施例,方法300(图3)在第一磊晶层410之 上形成多个心轴结构(mandrel structure)420。图4a为根据一些实施例在第一磊 晶层410之上形成多个心轴结构420之后的半导体结构400的横截面图。

143.参考图4a,提供基板402。在一些实施例中,基板402为体半导体基板。 在一些实施例中,体半导体基板包括半导体材料或半导体材料的堆叠,诸如 si、ge、sige、sic、sigec;或iii-v族化合物半导体,诸如gaas、gap、inp、 inas、insb、gaasp、alinas、algaas、gainas、gainp或gainasp。在一些 实施例中,体半导体基板包括单晶半导体材料,诸如单晶si。在一些实施例中, 取决于设计要求对体半导体基板进行掺杂。在一些实施例中,体半导体基板的 上部部分掺杂有p型掺杂剂或n型掺杂剂以形成掺杂半导体区402a。例示性 p型掺杂剂包括但不限于b、al、ga及in。例示性n型掺杂剂包括但不限于p、 as及sb。掺杂半导体区402a具有低电阻率(即重掺杂),掺杂浓度范围为 1.0

×

10

19

原子/cm3至1.0

×

10

22

原子/cm3,但掺杂浓度可更大或更小。在一些实 施例中,掺杂半导体区402a用作随后形成的垂直fet的底部源极/漏极结构。

144.在一些实施例中,基板402为soi基板的顶部半导体层。顶部半导体层 包括上述半导体材料,诸如si、ge、sige、sic、sigec;或iii-v族化合物半 导体,包括gaas、gap、inp、inas、insb、gaasp、alinas、algaas、gainas、 gainp或gainasp。

145.第一磊晶层410安置在基板402上。第一磊晶层410可包括如上文针对基 板402提交的任何半导体材料。在一些实施例中,第一磊晶层410包括与提供 基板402的半导体材料相同的半导体材料。举例而言,第一磊晶层410与基板402两者皆可由si构成。在一些其他实施例中,第一磊晶层410包括与提供基 板402的半导体材料不同的半导体材料。举例而言,在一些实施例中,第一磊 晶层410由sige或ge构成,而基板402由si构成。

146.第一磊晶层410形成为具有至少100ω

·

cm的高电阻率。在一些实施例中, 第一磊晶层410为本征的(即,未掺杂的)。在其他实施例中,第一磊晶层 410可轻掺杂有n型或p型掺杂剂,且具有在1.0

×

10

12

原子/cm3至1.0

×

10

14

原 子/cm3范围内的掺杂剂浓度。高电阻率有助于降低寄生电容,从而允许装置更 紧密地封装在基板402上。

147.第一磊晶层410是通过诸如mbe或mocvd的磊晶生长工艺形成。因此, 第一磊晶层410具有与下伏基板402相同的晶体定向。若经掺杂,则可在沉积 提供第一磊晶层410的半导体材料时,即在磊晶生长工艺期间引入掺杂剂。或 者,在一些实施例中,可在磊晶生长工艺之后将掺杂剂引入至第一磊晶层410 中,例如通过离子植入。

148.心轴结构420安置在第一磊晶层410之上。应注意,在本揭露中可设想任 何数目个心轴结构420。为了简单起见,仅说明及描述单一心轴结构420。心 轴结构420可包括可相对于第一磊晶层410选择性移除的任何材料(例如,半 导体、介电或导电材料)。在一些实施例中,心轴结构420包括非晶si、多晶 硅、非晶或多晶ge、非晶或多晶sige、无定形碳、类金刚石碳或有机硅玻璃。

149.在一些实施例中,通过首先使用诸如cvd或pecvd的沉积工艺在第一 磊晶层410上沉积心轴层来形成心轴结构420。随后,心轴层通过光微影及蚀 刻而经图案化。心轴层的图案化是例如通过在心轴层上方施加光阻剂层、光微 影图案化光阻剂层及通过非等相性蚀刻将光阻剂层中的图案转印至心轴层中 来执行。非等相性蚀刻可为诸如rie的干式蚀刻或湿式蚀刻。心轴层在光微影 图案化之后的剩余部分构成心轴结构420。在心轴结构420形成之后,例如通 过灰化移除图案化光阻剂层。

150.在操作304处,根据一些实施例,方法300(图3)在心轴结构420的侧 壁上形成多个间隔物422。图4b为根据一些实施例的在心轴结构420的侧壁 上形成多个间隔物422之后的图4a的半导体结构400的横截面图。

151.参考图4b,间隔物422可包括具有与心轴结构420不同的蚀刻选择性的 任何材料,从而可相对于间隔物422选择性地移除心轴结构420。在一些实施 例中,间隔物422包括诸如氧化硅的介电氧化物或诸如氮化硅的介电氮化物。 在一些实施例中,通过在心轴结构420及第一磊晶层410之上共形地沉积间隔 物层,随后移除间隔物层的水平部分来形成间隔物422。在一些实施例中,执 行可为诸如rie的干式蚀刻或湿式蚀刻的非等相性蚀刻以移除间隔物层的水 平部分。存在于心轴结构420的侧壁上的间隔物层的剩余垂直部分构成间隔物 422。

152.在操作306处,根据一些实施例,方法300(图3)移除心轴结构420。 图4c为根据一些实施例的在移除心轴结构420之后的图4b的半导体结构400 的横截面图。

153.参考图4c,通过蚀刻相对于间隔物422及第一磊晶层410选择性地移除 心轴结构420。该蚀刻可为诸如rie的干式蚀刻或湿式蚀刻。在一些实施例中, 诸如缓冲氢氟酸的基于氢氟酸(hydrofluoric acid,hf)的蚀刻剂用于移除心 轴结构420,而不蚀刻间隔物422及第一磊晶层410。

154.在操作308处,根据一些实施例,方法300(图3)蚀刻第一磊晶层410 以形成多个第一纳米片432a。图4d为根据一些实施例的在蚀刻第一磊晶层 410以形成多个第一纳米片432a之后的图4c的半导体结构400的横截面图。

155.参考图4d,使用间隔物422作为蚀刻遮罩蚀刻第一磊晶层410。在一些 实施例中,执行非等相性蚀刻以移除第一磊晶层410的未由间隔物422覆盖的 部分。在一些实施例中,非等相性蚀刻为诸如rie的干式蚀刻或湿式蚀刻。第 一磊晶层410的剩余部分构成第一纳米片432a。第一纳米片432a中的每一 者的厚度被控制为小于临界厚度以最小化随后在其上形成的磊晶层中的缺陷 形成。在一些实施例中,第一纳米片432a中的每一者的厚度范围自约1nm 至约10nm。若第一纳米片432a的厚度过大,则其上随后形成的磊晶层中可 能会形成缺陷。若第一纳米片432a的厚度过小,则各别第一纳米片432a可 能不具有用于装置制造的足够机械强度。在一些实施例中,第一纳米片432a 中的每一者的厚度范围自约3nm至约5nm。

156.在操作310处,根据一些实施例,方法300(图3)在第一纳米片432a 的侧壁上形成多个第二纳米片434a。图4e为根据一些实施例的在第一纳米片 432a的侧壁上形成多个第二纳米片434a之后的图4d的半导体结构400的横 截面图。

157.参考图4e,第二纳米片434a包括与第一纳米片432a不同的半导体材料。 在一些实施例中,第二纳米片434a包括:iv族半导体材料,诸如si、ge、 sige、sigec、sic等;iii-v族

化合物半导体材料,诸如gaas、gap、gaasp、 alinas、algaas、gainas、inas、gainp、inp、insb、gainasp等。在一些实 施例中且当第一纳米片432a由si构成时,第二纳米片434a由sige或ge构 成。

158.在一些实施例中,通过在基板402及第一纳米片432a的曝露表面上磊晶 生长第二磊晶层来形成第二纳米片434a。在一些实施例中,通过诸如cvd、 ald或mbe的共形沉积工艺沉积第二磊晶层。第二磊晶层的厚度被控制为小 于各别临界厚度,高于该临界厚度便会出现缺陷。在一些实施例中,第二磊晶 层的厚度范围为约1nm至约10nm。若第二磊晶层的厚度过大,则可能在第 二磊晶层中形成缺陷。若第二磊晶层的厚度过小,则所得第二纳米片434a可 能不具有用于装置制造的足够机械强度。在一些实施例中,第二磊晶层的厚度 范围为约3nm至约5nm。随后,例如通过非等相性蚀刻移除位于基板402及 第一纳米片432a的顶表面上的第二磊晶层的水平部分。非等相性蚀刻可为诸 如rie的干式蚀刻或湿式蚀刻。第二磊晶层的保留在第一纳米片432a的侧壁 上的垂直部分构成第二纳米片434a。

159.在一些实施例中,继续第二磊晶层的磊晶生长,直至第二磊晶层填充第一 纳米片432a之间的空间。在执行cmp工艺以平坦化第二磊晶层使得第二磊 晶层的顶表面与第一纳米片432a的顶表面共面之后,蚀刻第二磊晶层以提供 第二纳米片434a。

160.在操作312处,根据一些实施例,方法300(图3)在第二纳米片434a 的侧壁上形成多个第三纳米片432b。图4f为根据一些实施例的在第二纳米片 434a的侧壁上形成多个第三纳米片432b之后的图4e的半导体结构400的横 截面图。

161.参考图4f,第三纳米片432b适于与对应的第一纳米片432a及第二纳米 片434a形成超晶格结构。因此,第三纳米片432b包括与第一纳米片432a 相同的半导体材料。举例而言,在一些实施例中,第一纳米片432a及第三纳 米片432b两者皆包括si。

162.在一些实施例中,通过在基板402、第一纳米片432a及第二纳米片434a 的曝露表面上磊晶生长第三磊晶层来形成第三纳米片432b。在一些实施例中, 通过诸如cvd、ald或mbe的共形沉积工艺沉积第三磊晶层。第三磊晶层 的厚度被控制为小于各别临界厚度,高于该临界厚度便会出现缺陷。在一些实 施例中,第三磊晶层的厚度范围为约1nm至约10nm。若第三磊晶层的厚度 过大,则第三磊晶层中可能形成缺陷。若第三磊晶层的厚度过小,则所得第三 纳米片432b可能不具有用于装置制造的足够机械强度。在一些实施例中,第 三磊晶层的厚度范围为约3nm至约5nm。随后,例如通过非等相性蚀刻移除 位于基板402、第一纳米片432a及第二纳米片434a的顶表面上的第三磊晶 层的水平部分。该非等相性蚀刻可为诸如rie的干式蚀刻或湿式蚀刻。第三磊 晶层的保留在第二纳米片434a的侧壁上的垂直部分构成第三纳米片432b。

163.在一些实施例中,继续第三磊晶层的磊晶生长,直至第三磊晶层填充第二 纳米片434a之间的空间。在执行cmp工艺以平坦化第三磊晶层使得第三磊 晶层的顶表面与第一纳米片432a及第二纳米片434a的顶表面共面之后,蚀 刻第三磊晶层以提供第三纳米片432b。

164.由此形成自基板402向上延伸的多个超晶格结构430。在一些实施例中, 超晶格结构430中的每一者包括在横向方向上堆叠的第一半导体材料的三个 纳米片(即,一个第一纳米片432a及一对第三纳米片432b)及第二半导体 材料的两个纳米片(即,一对第二纳米片434a))。第二半导体材料的纳米 片434a将第一半导体材料的纳米片432a、432b彼此分开。应注意,形成各 别第二纳米片434a及第三纳米片432b的操作310及312可重复以按替代

组 态形成第一半导体材料的纳米片及第二半导体材料的纳米片。因此,超晶格结 构430可由在横向方向上的堆叠的任意数目个交替的第一半导体材料的纳米 片及第二半导体材料的纳米片形成。

165.在操作314处,根据一些实施例,方法300(图3)在基板402之上形成 绝缘体层440。图4g为根据一些实施例的在基板402之上形成绝缘体层440 之后的图4f的半导体结构400的横截面图。

166.参考图4g,绝缘体层440经形成以围绕超晶格结构430中的每一者的底 部部分。在一些实施例中,绝缘体层440包括介电材料,诸如氮化硅、siocn 或sibcn。在一些实施例中,绝缘体层440是通过使用诸如cvd或pvd的 沉积工艺在超晶格结构430之上及之间沉积介电材料、通过诸如cmp的平坦 化技术平坦化所沉积的介电材料,且回蚀所沉积的介电材料而形成。可使用诸 如rie的非等相性蚀刻来相对于超晶格结构430的半导体材料选择性地回蚀绝 缘体层440的介电材料。

167.在操作316,根据一些实施例,方法300(图3)在绝缘体层440及超晶 格结构430之上沉积栅极材料堆叠。图4h为根据一些实施例的在绝缘体层440 及超晶格结构430之上沉积栅极材料堆叠之后的图4g的半导体结构400的横 截面图。

168.参考图4h,栅极材料堆叠包括沉积在绝缘体层440及超晶格结构430的 曝露表面上的栅极介电质层452及沉积在栅极介电质层452上的栅电极层454。 栅电极层454填充超晶格结构430之间的空间。

169.在一些实施例中,栅极介电质层452包括高k介电材料,诸如hfo2、zro2、 la2o3、al2o3、tio2、srtio3、laalo3或y2o3。在一些实施例中,栅极介电 质层452可具有包含不同栅极介电材料(例如二氧化硅)及高k栅极介电材料 的多层结构。在一些实施例中,栅极介电质层452是利用诸如cvd或ald 的共形沉积工艺形成。

170.栅电极层454可包含任何导电金属。在一些实施例中,栅电极层454包括 w、cu、al、co或其合金。在一些实施例中,栅电极层454是利用包括例如 cvd、pecvd或pvd的沉积工艺形成。

171.在一些实施例中,在沉积栅电极层454的前,可在栅极介电质层452上形 成可选的包括tin或tan的功函数金属层以调谐所得栅极结构的功函数。

172.在操作318处,根据一些实施例,方法300(图3)形成横向接触各别超 晶格结构430的通道区的侧壁的栅极结构450。图4i为根据一些实施例的在形 成横向接触各别超晶格结构430的通道区的侧壁的栅极结构450之后的图4h 的半导体结构400的横截面图。

173.参考图4i,栅极结构450中的每一者包括栅极介电质452p及栅电极454p。 栅极结构450可通过首先通过蚀刻使栅电极层454凹陷来形成。该蚀刻可为诸 如rie的干式蚀刻或湿式蚀刻,其相对于提供栅极介电质层452的介电材料选 择性地移除提供栅电极层454的导电金属。在使栅电极层454凹陷之后,栅电 极层454的剩余部分具有在超晶格结构430的顶表面的下的顶表面。接下来, 通过光微影及蚀刻移除位于相邻超晶格结构430之间的栅电极层454的剩余部 分的部分,从而提供栅电极454p。举例而言,光阻剂层施加在栅电极层454 的剩余部分之上且经光微影图案化,使得图案化光阻剂层覆盖栅电极层454 的剩余部分的将形成栅电极454p的部分。接着执行非等相性蚀刻以移除栅电 极层454的剩余部分的未由图案化光阻剂层覆盖的部分以提供栅电极454p。 该非等相性蚀刻可为诸如rie的干式

蚀刻或湿式蚀刻。随后可例如通过灰化移 除图案化光阻剂层。

174.接下来,通过非等相性蚀刻移除栅极介电栅极层452的未由栅电极454p 覆盖的部分。非等相性蚀刻可为诸如rie的干式蚀刻或湿式蚀刻,其相对于提 供超晶格结构430的半导体材料选择性地移除提供栅极介电质层452的介电材 料。在栅电极454p下方的栅极介电质层452的剩余部分构成栅极介电质452p。 栅极介电质452p接触各别超晶格结构430的通道区的侧壁。栅极介电质层452 的蚀刻曝露绝缘体层440的顶表面。

175.在操作320处,根据一些实施例,方法300(图3)在栅极结构450及绝 缘体层440之上沉积介电间隔物层460。图4j为根据一些实施例的在栅极结 构450及绝缘体层440之上沉积介电间隔物层460之后的半导体结构400的横 截面图。

176.参考图4j,介电间隔物层460存在于栅电极454p上,用于将栅电极454p 与随后形成的垂直fet的顶部源极/漏极结构分开。介电间隔物层460亦存在 于相邻的栅极结构450之间以将栅极结构450彼此电隔离。在一些实施例中, 介电间隔物层460包括介电材料,诸如氧化硅或氮化硅。在一些实施例中,介 电间隔物层460是通过诸如cvd或pvd的沉积工艺来沉积。在一些实施例中, 介电间隔物层460经沉积以具有在超晶格结构430的顶表面之下的顶表面,从 而曝露超晶格结构430中的每一者的顶部部分。

177.在操作322处,根据一些实施例,方法300(图3)在超晶格结构430中 的每一者的顶部部分周围形成掺杂磊晶区470。图4k为根据一些实施例的在 超晶格结构430中的每一者的顶部部分周围形成掺杂磊晶区470之后的图4j 的半导体结构400的横截面图。

178.参考图4k,掺杂磊晶区470包括半导体材料,诸如si、ge、sige、sic 或sigec。掺杂磊晶区470用作垂直fet的顶部源极/漏极结构。掺杂磊晶区 470因此含有具有与掺杂半导体区402a中的掺杂剂的导电类型相同的导电类 型的掺杂剂。举例而言,对于n型垂直fet,掺杂磊晶区470及掺杂半导体区 402a两者皆含有n型掺杂剂。而对于p型fet,基板402中的掺杂磊晶区470 及掺杂半导体区402a两者皆含有p型掺杂剂。在一些实施例中,掺杂磊晶区 470的掺杂剂浓度可自1

×

10

19

原子/cm3至1

×

10

22

原子/cm3,但可使用较小或较 大的的掺杂剂浓度。

179.在一些实施例中,掺杂磊晶区470是利用选择性磊晶生长工艺形成。在选 择性磊晶生长期间,提供掺杂磊晶区470的半导体材料仅自包括超晶格结构 430的顶部部分的实体曝露的最上表面及侧壁表面的半导体表面生长,而不自 介电表面(诸如介电间隔物层460的顶表面)生长。可在选择性磊晶生长工艺 期间通过原位掺杂提供掺杂剂,或在选择性磊晶生长工艺之后通过离子植入或 气相掺杂提供掺杂剂。

180.因此形成垂直fet。每一垂直fet包括自基板402向上延伸的超晶格结 构430、在超晶格结构430下方作为底部源极/漏极结构的掺杂半导体区402a、 接触作为顶部源极/漏极结构的超晶格结构430的顶部表面及顶部表面的侧壁 的掺杂磊晶区470,及包括横向接触超晶格结构430的通道区的栅极介电质 452p及栅电极454p的栅极结构。超晶格结构430包括在横向方向上堆叠且垂 直于基板402的第一半导体材料的纳米片(即,第一纳米片432a及第三纳米 片432b)及第二半导体材料的纳米片(第二纳米片434a)。与使用单一半导 体材料的纳米片作为垂直fet的通道相比,使用包含不同半导体材料的纳米 片的超晶格结构作为垂直fet中的通道有助于提高载流子迁移率,且由于超 晶格结构中的表面缺陷减少而减少漏电流。结果,装置效能得以提高。

181.本揭露的一个态样是关于一种半导体结构。半导体结构包括一基板及在基 板之上的一第一超晶格结构及一第二超晶格结构。第二超晶格结构安置在第一 超晶格结构之上。第一超晶格结构及第二超晶格结构中的每一者包括垂直堆叠 的交替的一第一半导体材料的第一纳米片及不同于第一半导体材料的一第二 半导体材料的第二纳米片。半导体进一步包括围绕第一超晶格结构及第二超晶 格结构中的每一者的一通道区的栅极堆叠及在栅极堆叠的相对侧上的源极/漏 极结构。源极/漏极结构接触第一超晶格结构及第二超晶格结构的侧壁。

182.在部分实施例中,其中栅极堆叠包含位于第二超晶格结构上方的一第一部 分以及填充第一超晶格结构与第二超晶格结构之间的一第一空间及第一超晶 格结构与基板之间的一第二空间的一第二部分。

183.在部分实施例中,其中栅极堆叠的第一部分包含接触第二超晶格结构的一 顶表面的一u形栅极介电质及由u形栅极介电质围绕的一栅电极。

184.在部分实施例中,进一步包含在栅极堆叠的第一部分的侧壁上的栅极间隔 物。

185.在部分实施例中,进一步包含在栅极堆叠的第二部分的侧壁上的内部间隔 物。

186.在部分实施例中,其中内部间隔物的侧壁与第一超晶格结构及第二超晶格 结构的侧壁垂直对准。

187.在部分实施例中,其中第一纳米片包含硅,且第二纳米片包含硅锗或锗。

188.在部分实施例中,其中第一纳米片及第二纳米片中的每一者的一厚度范围 为约1nm至约10nm。

189.在部分实施例中,进一步包含在源极/漏极结构上的一介电质层,介电质 层围绕栅极堆叠。

190.本揭露的另一态样是关于一种用于形成一半导体结构的方法。方法包括在 一基板上形成含有垂直堆叠的交替超晶格层及牺牲层的一鳍结构。超晶格层中 的每一者包括交替的一第一半导体材料的第一层及不同于第一半导体材料的 一第二半导体材料的第二层。方法进一步包括形成横跨鳍结构的一部分的一牺 牲栅极结构。牺牲栅极结构包括一牺牲栅极堆叠及位于牺牲栅极堆叠的侧壁上 的栅极间隔物。方法进一步包括:移除鳍结构的未由牺牲栅极结构覆盖的部分 以提供包含垂直堆叠的交替超晶格结构及牺牲结构的一鳍区段;在鳍区段的端 壁上形成源极/漏极结构;在源极/漏极结构上沉积一介电质层;移除牺牲栅极 堆叠以提供一栅极腔体;移除牺牲结构;以及形成围绕超晶格结构中的每一者 的一栅极堆叠。

191.在部分实施例中,其中移除牺牲结构的步骤包含以下步骤:执行一等相性 蚀刻,等相性蚀刻用以相对于超晶格结构选择性地移除牺牲结构,其中移除牺 牲结构在超晶格结构之间提供第一空间。

192.在部分实施例中,进一步包含以下步骤:蚀刻基板以在超晶格结构中的一 最底部超晶格结构下方形成一第二空间。

193.在部分实施例中,其中形成栅极堆叠的步骤包含以下步骤:在超晶格结构 的曝露表面及栅极腔体之上沉积一栅极介电质;以及在栅极介电质之上沉积一 栅电极,栅电极填充栅极腔体、第一空间及第二空间。

194.在部分实施例中,其中形成鳍结构的步骤包含以下步骤:在基板之上形成 一多层

堆叠,其中多层堆叠包括垂直层叠的交替超晶格层及牺牲层;以及通过 至少一个非等相性蚀刻来蚀刻垂直堆叠的交替超晶格层及牺牲层。

195.在部分实施例中,其中形成源极/漏极结构的步骤包含以下步骤:自鳍区 段的端壁磊晶生长一第三半导体材料。

196.在部分实施例中,进一步包含以下步骤:蚀刻牺牲结构的端部以形成凹部; 以及在凹部中形成内部间隔物。

197.本揭露的又一态样是关于一种半导体结构。半导体结构包括自一基板向上 延伸的一超晶格结构。超晶格结构包括垂直于基板对准的交替的一第一半导体 材料的第一纳米片及一第二半导体材料的第二纳米片。第一半导体材料不同于 第二半导体材料。半导体结构进一步包括横向接触超晶格结构的一通道区的一 栅极结构及围绕超晶格结构的一顶部部分的一掺杂磊晶区。

198.在部分实施例中,进一步包含位于栅极结构与掺杂磊晶区之间的一介电间 隔物层。

199.在部分实施例中,进一步包含围绕超晶格结构的一底部部分的一绝缘体层。

200.在部分实施例中,进一步包含在超晶格结构下方的基板中的一掺杂半导体 区。

201.前文概述了若干实施例的特征,使得熟悉此项技术者可更佳地理解本揭露 的各态样。熟悉此项技术者应理解,其可容易地将本揭露用作设计或修改其他 过程及结构的基础,以实现与本文介绍的实施例相同的目的及/或达成相同的 优点。熟悉此项技术者亦应认识到,此类等效组态不脱离本揭露的精神及范围, 且在不背离本揭露的精神及范围的情况下,可对其进行各种改变、替换及更改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1