三维存储器及其制作方法以及存储系统与流程

1.本公开实施例涉及半导体技术领域,尤其涉及一种三维存储器及其制作方法。

背景技术:

2.三维存储器可包括存储阵列以及外围电路(例如,驱动器和逻辑电路等),外围电路可对存储阵列进行控制,操作存储阵列进行读写或者擦除。

3.外围电路中包括有不同的电容,以实现外围电路的各种电性功能,进而对存储阵列进行控制操作。随着存储阵列集成度的提高,外围电路的集成度也需要不断提高以满足对高集成度存储阵列的控制,电容的集成度也需要得到提高。然而,电容往往需要占据外围电路中的一部分区域,从而阻碍了外围电路的缩小以及集成度的提高。因此,如何提高电容的集成度成为亟待解决的问题。

技术实现要素:

4.根据本公开实施例的第一方面,提供一种三维存储器的制作方法,包括:

5.提供基底,在所述基底上形成叠层结构;

6.形成贯穿所述叠层结构的沟道孔,填充所述沟道孔以形成存储单元柱;

7.形成贯穿所述叠层结构的电容孔,填充所述电容孔以形成电容,所述电容与所述叠层结构电隔离;其中,沿着所述电容的径向,所述电容包括:第一电极,围绕所述第一电极的第一介电层和第二电极,所述第一介电层位于所述第一电极和所述第二电极之间;

8.其中,所述存储单元柱与所述基底耦接,所述第二电极与所述基底耦接。

9.根据本公开实施例的第二方面,提供一种三维存储器,包括:

10.基底;

11.堆叠结构,位于所述基底上;

12.存储单元柱,贯穿所述堆叠结构,且与所述堆叠结构电隔离;

13.电容,贯穿所述堆叠结构,且与所述堆叠结构电隔离;沿着所述电容的径向,所述电容包括:第一电极,围绕所述第一电极的第一介电层和第二电极,所述第一介电层位于所述第一电极和所述第二电极之间;

14.所述存储单元柱与所述基底耦接,所述第二电极与所述基底耦接。

15.根据本公开实施例的第三方面,提供一种存储系统,包括:

16.存储器,包括上述实施例的三维存储器;

17.存储器控制器,耦合到所述存储器并且被配置为控制所述存储器。

18.本公开实施例,形成贯穿叠层结构的电容孔,填充电容孔以形成电容,电容的第二电极与存储单元柱都与基底耦接。相较于将电容形成于叠层结构以外区域以构成外围电路的制作方法,本公开中的电容与存储单元柱形成于叠层结构中,电容的尺寸以及形成方法不会限制外围电路中其他器件的集成度,提高电容集成度的同时也可保持甚至提高外围电路的集成度。并且,本公开实施例中的电容的第二电极与存储单元柱共同耦接基底,可省略

制作其他电极接触结构的工艺步骤,降低制作成本。

附图说明

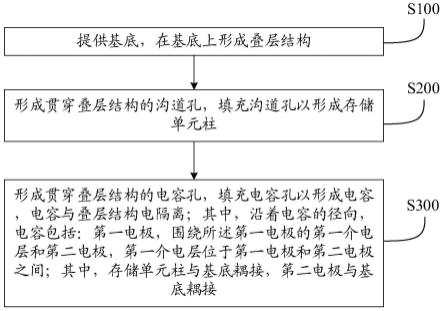

19.图1是根据本公开实施例示出的一种三维存储器的制作方法的流程示意图;

20.图2a至图2h是根据本公开实施例示出的一种三维存储器的制作方法的示意图;

21.图3是根据本公开实施例示出的一种具有台阶区的三维存储器的制作方法的示意图;

22.图4a和图4b是根据本公开实施例示出的一种电容与存储单元柱的排布示意图;

23.图5a和图5b是根据本公开实施例示出的一种电容的制作方法的示意图;

24.图6a和图6b是根据本公开实施例示出的另一种电容的制作方法的示意图;

25.图7是根据本公开实施例示出的具有两个堆叠的三维存储器的示意图;

26.图8是根据本公开实施例示出的另一种三维存储器的示意图;

27.图9是根据本公开实施例示出的一种包括有存储器的系统块图;

28.图10a是根据本公开实施例示出的一种包括有存储器的存储器卡的示意图;

29.图10b是根据本公开实施例示出的一种包括有存储器的固态驱动器(ssd)的示意图;

30.图11是根据本公开实施例示出的一种包括有外围电路的存储器的示意图;

31.图12是根据本公开实施例示出的一种包括有外围电路的存储器的块图。

具体实施方式

32.以下结合说明书附图及具体实施例对本公开的技术方案做进一步的详细阐述。

33.在本公开实施例中,术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。

34.在本公开实施例中,术语“a与b耦接”包含a与b直接接触的情形,或者a、b两者之间还间插有其它部件而a间接地与b耦接的情形。

35.在本公开实施例中,术语“层”是指包括具有厚度的区域的材料部分。层可以在下方或上方结构的整体之上延伸,或者可以具有小于下方或上方结构范围的范围。此外,层可以是厚度小于连续结构厚度的均质或非均质连续结构的区域。例如,层可位于连续结构的顶表面和底表面之间,或者层可在连续结构顶表面和底表面处的任何水平面对之间。层可以水平、垂直和/或沿倾斜表面延伸。并且,层可以包括多个子层。

36.可以理解的是,本公开中的“在

……

上”、“在

……

之上”和“在

……

上方”的含义应当以最宽方式被解读,以使得“在

……

上”不仅表示其“在”某物“上”且其间没有居间特征或层(即直接在某物上)的含义,而且还包括“在”某物“上”且其间有居间特征或层的含义。“a覆盖b”,也包括其间没有居间特征或层(即直接在某物上)的含义,而且还包括“在”某物“上”且其间有居间特征或层的含义。

37.需要说明的是,虽然本说明书按照实施方式加以描述,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施方式中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其它实施方式。

38.在三维存储器中,存储阵列和外围电路往往分别设置于基底的不同区域。例如,存储阵列与外围电路可水平并列设置,即外围电路可设置于存储阵列的一侧,外围电路与存储阵列在制作的过程中共用一个基底。或者,存储阵列与外围电路可垂直设置,即存储阵列与外围电路分别形成于不同的基底,之后通过键合工艺使得存储阵列与外围电路形成电信号互联,外围电路可位于存储阵列上部或者下部。

39.电容作为外围电路的一部分,往往会和外围电路的其他器件一起制作,所以电容往往会跟随外围电路也布置在存储阵列之外的区域。电容包括第一电极、介电层以及第二电极,介电层将第一电极和第二电极电隔离,第一电极和第二电极可分别施加不同的电压,介电层包括绝缘材料或者气隙。

40.相较于外围电路中cmos晶体管中栅极等部件的尺寸,电容的第一电极、介电层以及第二电极具有更大的尺寸,以获得更大的电极正对面积(第一电极与第二电极重叠的面积),由此来保持较高电容量以及较高的耐受电压,降低电容被高压击穿的风险。在一些外围电路中,往往会串联或者并联多个电容以配置不同功能的电路,所以电容会占用外围电路的一部分区域,会限制cmos晶体管等器件的集成度的提高。并且当电容的集成度增大时,电容占用外围电路的区域会进一步增多,进一步压缩外围电路其他器件的制作区域,阻碍外围电路集成度的提高。

41.随着三维存储器存储阵列集成度的不断提高,外围电路的集成度也在不断提高,电容的集成度也在不断提高。对此,本公开实施例提出的一种三维存储器的制作方法,在提高电容集成度的同时,保持甚至提高外围电路中其他器件的集成度。

42.图1是根据本公开实施例示出的一种三维存储器的制作方法的流程示意图,图2a至图2是根据本公开实施例示出的一种三维存储器的制作方法的示意图。结合图1、图2a至图2f所示,该制作方法包括以下步骤:

43.s100:参照图2a所示,提供基底210,在基底210上形成叠层结构220;

44.s200:参照图2a所示,形成贯穿叠层结构220的沟道孔23;参照图2b和图2c所示,填充沟道孔23以形成存储单元柱230;

45.s300:参照图2b所示,形成贯穿叠层结构220的电容孔24;参照图2d至图2f所示,填充电容孔24以形成电容240,电容240与叠层结构220电隔离;其中,沿着电容240的径向,电容240包括:第一电极241,围绕第一电极241的第一介电层242和第二电极243,第一介电层242位于第一电极241和第二电极243之间;其中,存储单元柱230与基底210耦接,第二电极243与基底210耦接。

46.示例性的,基底210的组成材料可包括:单质半导体材料(例如硅、锗)、

ⅲ‑ⅴ

族化合物半导体材料、

ⅱ‑ⅵ

族化合物半导体材料、有机半导体材料或者本领域已知的其它半导体材料。基底210也可经过掺杂,例如p型掺杂或者n型掺杂。

47.示例性的,形成叠层结构220、第二电极243、第一介电层242以及第一电极241的工艺可以包括本技术领域所知的任何工艺,例如低温化学气相沉积、低压化学气相沉积、快速热化学气相沉积、原子层沉积或者等离子体增强化学气相沉积等工艺。

48.需要强调的是,本实施例中的基底210为一种具有一定厚度膜层结构,可包括裸晶圆,也可包括外延层。例如,基底210为未执行镀膜、蚀刻等制程的裸晶圆(例如,裸硅晶圆)。或者,基底210为基于裸晶圆表面外延生长的外延层,外延层材料可与裸晶圆材料相同,也

可不同,而裸晶圆可在某个制作工序中被除去。

49.参照图2a所示,叠层结构220可包括互相层叠设置的栅极牺牲层221以及层间绝缘层222,栅极牺牲层221可在s300之后,被替换成栅极层223,栅极层223作为三维存储器的字线。栅极牺牲层221的组成材料包括:氮化硅、氮氧化硅、单晶硅、多晶硅或者其任意组合。层间绝缘层222的组成材料包括:氧化硅、氧化铝等绝缘材料或者其任意组合。

50.形成沟道孔23和电容孔24的工艺包括:干法蚀刻工艺、湿法蚀刻工艺或者其任意组合。沟道孔23的底部可仅仅与基底210的上表面接触,即在对叠层结构220进行蚀刻的过程中,蚀刻剂对于基底210不造成蚀刻。

51.在本实施例中,参照图2a所示,沟道孔23的底部可延伸进基底210中。参照图2b所示,填充沟道孔23以形成存储单元柱230。为了更加清楚明了的解释说明存储单元柱230的膜层结构,图2c示出了图2b中存储单圆柱顶部在xoy平面的俯视图。

52.参照图2c所示,沿着存储单元柱230的径向,存单储元柱230包括沟道层231,围绕沟道层231的功能层。功能层包括隧穿子层232、存储子层233以及阻挡子层234,隧穿子层232位于沟道层231和存储子层233之间,存储子层233位于隧穿子层232和阻挡子层234之间,沟道层231与基底210耦接。其中,沟道层231可以包括单晶硅、多晶硅或者其任意组合。隧穿子层232可以包括氧化硅、氮氧化硅或其任意组合。存储子层233可以包括氮化硅、氮氧化硅或其任意组合。阻挡子层234可以包括氧化硅、氮氧化硅、高介电材料或其任何组合。作为示例的,本实施例中,沟道层231选择多晶硅,隧穿子层232选择二氧化硅,存储子层233选择氮化硅,阻挡子层234选择二氧化硅和氧化铝(高介电材料),氧化铝层包围二氧化硅层。此处的高介电材料为介电常数高于二氧化硅的介电常数的材料。

53.图2b所示出的存储单元柱230仅为示例,本实施例还可包括更多的存储单元柱230,多个存储单元柱230成阵列排布,以构成存储阵列。

54.电容孔24的底部可仅仅与基底210的上表面接触,也可如图2b所示的延伸进基底210中。参照图2d所示,在形成第二电极243之前,以绝缘材料覆盖电容孔24的侧壁,绝缘材料显露电容孔24的底部,再填充包括绝缘材料的电容孔24形成如图2d所示的第二电极243、第一介电层242以及第一电极241,第二电极243的底部与基底210直接接触以形成耦接,第一介电层242电隔离第二电极243和第一电极241。绝缘材料包括:氧化硅,氮化硅,氮氧化硅,高介电材料或者其任意组合。绝缘材料电隔离电容240与叠层结构220,避免栅极牺牲层221被替换形成栅极层后与第二电极243接触而造成存储器失效。绝缘材料可以是多层的膜层以增加绝缘性能,例如图2d所示出的第二介电层244和第三介电层245,第二介电层244为二氧化硅,第三介电层245为高介电材料中的氧化铝。

55.示例性的,第一电极241和第二电极243的组成材料包括:钨、金、银、铜、铝、钛、镍、单晶硅或者多晶硅等导电材料。第一介电层242的组成材料包括:氧化硅,氮化硅,氮氧化硅,氧化铝或者其任意组合。

56.图2f示出了图2e中电容240上表面在xoy面上的俯视图。结合图2e和图2f所示,第二电极243、第一介电层242以及第一电极241基于电容孔24形成,第二电极243、第一介电层242以及第一电极241是环绕的连续结构。电容240为类似存储单元柱230的柱状结构,沿着z方向延伸。相较于电极为平板结构的平板电容240,本实施例中的电容240在占据相同基底210的面积时,第一电极241和第二电极243可以具有更大的面积,以获得更大的电极正对面

积(第一电极241与第二电极243重叠的面积),由此来保持较高电容量以及较高的耐受电压,降低电容240被高压击穿的风险。因此,在电容量相同的前提下,相较于平板电容240,本实施例的电容240可以占用更小的基板面积,有利于提高电容240的集成度。

57.在一些实施例中,可以在叠层结构220中形成虚拟沟道孔,填充虚拟沟道孔以形成支撑柱(也可称为,虚拟存储单元柱),支撑柱对存储器进行支撑。本公开实施例中的电容240也可对存储器提供支撑,可减少或者省略虚支撑柱的设置,提高存储单元柱230的集成度。

58.在一些实施例中,参照图2g所示,s300完成之后,该制作方法还包括形成贯穿叠层结构220的栅缝隙沟槽25,通过栅缝隙沟槽25蚀刻去除栅极牺牲层221以在相邻的层间绝缘层222之间形成空隙,以导电材料填充空隙形成栅极层223,使得叠层结构220形成堆叠结构220’。栅极层223的组成材料包括:钨、钛、镍、金、银或铜等导电材料。

59.在一些实施例中,参照图2h所示,以导电材料和绝缘材料填充栅缝隙沟槽25以形成栅缝隙结构251,栅缝隙结构251与堆叠结构220’电隔离,栅缝隙结构251与基底210耦接,为基底210供电。在另外一些实施例中,可仅用绝缘材料填充栅缝隙沟槽25,此时的栅缝隙结构251仅用于存储器的支撑。

60.在一些实施例中,参照图2h所示,基底210可作为共源极(或者,称为阵列公共源极acs)为存储单元柱230供电。可通过基底210为存储单元柱230提供一个电压,配合存储单元柱230的字线以及位线电压对存储单元柱230进行读写或者擦除的操作。示例性的,在读或者写的操作中,基底210提供低电压,例如,0v或者接地电压;在擦除的操作中,基底210提供高电压,例如20~25v,将存储单元柱230中存储子层233的电子抽出到沟道层231中,或者将沟道层231中的空穴注入存储子层233与电子中和,以此来实现擦除。

61.电容240中的第二电极243与基底210耦接,可与存储单元柱230共用共源极的电压,再对第一电极241施加其他电压,使第一电极241与第二电极243之间形成电压差,即可使电容240在电路中工作。在一些实施例中,将电容孔24与沟道孔23进行排列,将电容孔24设置在沟道孔23阵列的一端,从而使得形成的电容240也可位于存储单元柱230阵列的一端,形成贯穿基底210的隔离结构以将基底210划分为两部分,实现对第二电极243以及存储单元柱230阵列分别供电。隔离结构可包括:贯穿基底210的栅缝隙结构251、贯穿基底210的底部选择栅切线等。

62.本公开实施例,形成贯穿叠层结构220的电容孔24,填充电容孔24以形成电容240,电容240的第二电极243与存储单元柱230都与基底210耦接。相较于将电容240形成于叠层结构220之外区域以构成外围电路的制作方法,本公开中的电容240与存储单元柱230形成于叠层结构220中,电容240的尺寸以及形成方法不会限制外围电路中其他器件的集成度,提高电容240集成度的同时也可保持甚至提高外围电路的集成度。并且,本公开实施例中的电容240的第二电极243与存储单元柱230共同耦接基底210,可省略制作其他电极接触结构的工艺步骤,降低制作成本。

63.在一些实施例中,叠层结构220包括核心区和台阶区,台阶区位于核心区的一端;形成贯穿叠层结构220的电容孔24,包括:

64.在叠层结构220的核心区和/或台阶区,形成电容孔24。

65.存储单元柱230阵列设置于核心区,作为存储器的存储区域。台阶区位于核心区的

一端,用于形成耦接栅极层223的导电插塞,或者形成支撑柱对存储器提供支撑。台阶区中的一级台阶至少包括一层栅极牺牲层221以及与该栅极牺牲层221相邻的一层层间绝缘层222,栅极牺牲层221的端部位于台阶区。台阶区可以具有多个不同高度的台阶。

66.本实施例在图3中,填充电容孔24以形成电容240,将栅极牺牲层221替换成栅极层223以使叠层结构220形成堆叠结构220’,电容240可设置于堆叠结构220’的核心区211和/或台阶区212,可降低应力,减少或者省略支撑柱的设置,降低制作成本。

67.具体的,参照图3所示,电容240可仅设置于核心区211中,电容240与可与存储单元柱230相邻。电容240可仅设置于台阶区212中,不同的电容240可贯穿不同层数的台阶。电容240也可同时设置于核心区211以及台阶区212两个区域,或者两个区域的交界处。

68.继续参照图3所示,在堆叠结构220’的台阶区212形成沿z方向延伸的导电插塞261c,每个导电插塞261c与对应的栅极层223位于台阶区的端部耦接,为栅极层223提供字线电压。

69.电容240设置于核心区211和/或台阶区212,可降低应力,减少或者省略支撑柱的设置,降低制作成本。

70.在一些实施例中,多个存储单元柱230围绕至少一个电容240。

71.电容240可形成于核心区中,与存储单元柱230相邻。电容240的数量可少于存储单元柱230的数量,存储单元柱230成阵列排布,电容240被存储单元柱230包围。

72.例如图4a所示的,电容240成n字形排布。还例如图4b所示的,多个电容240包围至少一个存储单元柱230。图4a和图4b中,电容240和存储单元柱230可共同组成矩形阵列,如图4a中所示出的两个沿x方向排列的两个矩形阵列,相邻矩形阵列通过顶部选择栅切线252隔开,每个矩形阵列包括沿x方向并列排布的4个行结构,每个行结构包括沿y方向排布的多个存储单元柱230和多个电容240。

73.本实施例将电容240分布在存储单元柱230之间,减少形成电容240后的应力分布不均现象,提高存储器的制作良率。

74.在一些实施例中,参照图2b所示,电容孔24延伸进基底210中,参照图2d和图2e所示,填充电容孔24以形成电容240包括:

75.形成覆盖电容孔24侧壁和底部的第二电极243;

76.形成覆盖第二电极243的第一介电层242;

77.填充包括第二电极243和第一介电层242的电容孔24,形成第一电极241;其中,第一电极241包括柱状结构。

78.第二电极243的底部直接接触形成耦接,形成覆盖第二电极243的侧面以及底部的第一介电层242后,以导电材料填充电容孔24剩余的空间,形成柱状的第一电极241。其中,第二电极243和第一介电层242为围绕第一电极241的膜层结构。第一电极241除了用于承受电压对电容240供电外,还可用于对电容240以及对存储器提供支撑,提高存储器的制作良率,维持存储器的稳定性良好。柱状的第一电极241可提供更大面积的接触面,便于后期形成的导电插塞与第一电极241顶部耦接。

79.图5b示出了图5a电容240上表面在xoy平面的俯视图。在另外一些实施例中,不同于图2f所示出的,图5a和图5b中的第二电极243与第一电极241都为膜层结构。对电容孔24的侧壁和底部填充导电材料以形成第二电极243,以绝缘材料覆盖第二电极243以形成第一

介电层242,再以导电材料覆盖第一介电层242以形成第一电极241,最后以绝缘材料填充电容孔24剩余的空间以形成绝缘的芯部246。在图5a和图5b中,第一电极241、第一介电层242以及第二电极243围绕芯部246,芯部246用于对电容240的支撑。

80.在一些实施例中,在形成第二电极243前,制作方法还包括:

81.参照图6a所示,在电容孔24的底部形成导电块247,导电块247与基底210耦接;

82.参照图6b所示填充电容孔24以形成电容240包括:

83.填充包括导电块247的电容孔24,以形成电容240;其中,第二电极243覆盖电容孔24的侧壁和导电块247的上表面,第二电极243与导电块247耦接。

84.参照图6a所示,在电容孔24的底部形成导电块247,导电块247与基底210直接接触以形成耦接。导电块247的组成材料包括:单晶硅、多晶硅、钨、金、银、铜、铝、钛或镍等。例如,图6a中可采用外延生长工艺在电容孔24的底部沉积多晶硅,再对多晶硅进行掺杂以形成导电块247。

85.参照图6b所示,形成覆盖电容孔24侧壁以及导电块247上表面的第二电极243,导电块247的上表面为远离基底210的一侧表面。第二电极243通过导电块247与基底210耦接。

86.在一些实施例中,参照图6b所示,可在沟道孔23的底部形成导电块247,填充沟道孔23形成覆盖沟道孔23侧壁的功能层,形成覆盖功能层以及导电块247上表面的沟道层231,沟道层231通过导电块247与基底210耦接。耦接沟道层231的导电块247,以及耦接第二电极243的导电块247,可使用相同的工艺和材料形成,例如外延生长多晶硅工艺,利于工艺整合,利于降低制作成本。

87.在一些实施例中,参照图2e和图2f所示,电容240还包括第二介电层244和第三介电层245;在形成第二电极243前,制作方法还包括:

88.参照图2d所示,形成覆盖电容孔24侧壁的第三介电层245;形成覆盖第三介电层245的第二介电层244;其中,第三介电层245的介电常数大于二氧化硅的介电常数。

89.本实施例在第二电极243和叠层结构220之间形成第二介电层244和第三介电层245,第二介电层244和第三介电层245显露第二电极243的底面,第二电极243与基底210或者与基底210上的导电块247耦接。第二介电层244以及第三介电层245的组成材料包括:氧化硅、氮化硅、氮氧化硅或者高介电材料(高k材料)。通常将介电常数大于二氧化硅的介电常数的材料称为高介电材料,高介电材料包括:氧化铝、氧化钛、锆氧化、铪氧化或者氧化钌等。在达到相同绝缘性能的前提下,高介电材料所需的膜层厚度要比二氧化硅的膜层厚度要薄。

90.本实施例的第二介电层244可选用常用的二氧化硅,以降低制作成本,而第三介电层245选用高介电材料(例如,氧化铝)增加绝缘能力。在达到相同绝缘性能的要求下,本实施例相较于仅使用一层二氧化硅来电隔离叠层结构220和第二电极243,可以减少第二介电层244和第三介电层245的总厚度,有利于提高电容240的集成度。在另外一些实施例中,第三介电层245和第二介电层244也可全部为高介电材料,进一步提升绝缘性能。

91.在去除栅极牺牲层221的蚀刻工艺中,第三介电层245可作为蚀刻阻挡层,阻挡蚀刻剂对第二介电层244以及电容240其他结构的蚀刻损伤,提高电容240的制作良率。

92.在一些实施例中,电容孔24和沟道孔23的形成工艺相同,电容孔24的直径与沟道孔23的直径相同。

93.电容孔24与沟道孔23可同时形成也可不同时形成。形成电容孔24和沟道孔23的工艺相同,包括光刻、蚀刻等工艺参数相同,包括但不限于:相同分辨率的光刻机台,相同的蚀刻掩膜,相同的蚀刻剂配方,相同的蚀刻时间,相同的蚀刻功率。需要强调的是,这里的相同的工艺是指电容孔24与沟道孔23可套用相同的制作工艺制作,也包括根据电容孔24或者沟道孔23尺寸的变化,对工艺参数进行调整。例如,第n片晶圆的电容孔24或者沟道孔23直径比目标值大时,在第n+1片晶圆制作之前,可对制作参数进行调整,使得第n+1片晶圆的电容孔24与沟道孔23的直径符合工艺标准。

94.电容孔24的直径与沟道孔23的直径相同,利于电容孔24与沟道孔23套用相同的制作工艺,还利于电容孔24与沟道孔23执行相同的质量控制体系,包括但不限于:直径控制或者孔深度控制等。

95.在一些实施例中,在叠层结构220上形成第二个叠层结构220;

96.形成贯穿第二个叠层结构220的第二个存储单元柱230和第二个电容240;其中,两个叠层结构220中的相互层叠设置的电容240耦接,两个叠层结构220中相互层叠设置的存储单元柱230耦接。

97.在z方向上,两个相互层叠设置的两个电容240中的两个第二电极243进行耦接,两个电容240的第一电极241进行耦接,以实现上下电容240的耦接,增加电容240的电容量。两个相互层叠设置的两个存储单元柱230中的两个沟道层231耦接,增加存储单元柱230的存储容量。

98.在一些实施例中,形成贯穿两个叠层结构220的栅缝隙沟槽25,利用栅缝隙沟槽25替换两个叠层结构220的栅极牺牲层221,以形成如图7所示的相互层叠设置的两个堆叠结构220’。导电材料填充栅缝隙沟槽25形成栅缝隙结构251,用以对基底210的供电。或者,绝缘材料填充栅缝隙沟槽25形成栅缝隙结构251,用以对存储器的支撑。

99.在另外一些实施例中,也可先形成底部的堆叠结构220’,再层叠第二个叠层结构220,替换第二个叠层结构220的栅极牺牲层221为栅极,以形成第二个堆叠结构220’。

100.在一些实施例中,参照图3所示,该制作方法还包括:

101.在电容240远离基底210的一侧形成第一导电插塞261a,第一导电插塞261a与第一电极241耦接;

102.在第一导电插塞261a远离电容240的一侧形成第一互联层271,第一互联层271与第一导电插塞261a和存储单元柱230耦接。

103.参照图3所示,在电容240的顶部,形成与第一电极241耦接的第一导电插塞261a,以对第一电极241供电。在存储单元柱230的顶部,也可运用相同的工艺同时形成与沟道层231耦接的第一导电插塞261b,以降低制作成本。在一些示例中,与存储单元柱230耦接的第一导电插塞261b耦接到第一互联层271中的位线,电容240的第一电极241也可通过第一导电插塞261a耦接到位线,通过位线来给第一电极241提供电压。在另外一些示例中,第一互联层271可包括多个电信号交互的布线层或者器件。例如,第一互联层271除了包括位线,还设置有其他的导电线,用以为电容240的第一电极241单独供电,扩大电容240的使用场景。

104.在一些实施例中,参照图8所示,该制作方法还包括:

105.在基底210远离电容240的一侧形成第二导电插塞262;其中,第二导电插塞262贯穿基底210,且与第二电极243耦接;

106.在第二导电插塞262远离电容240的一侧形成第二互联层272,第二互联层272与第二导电插塞262耦接。

107.参照图8所示,对基底210远离电容240的一侧进行减薄,再形成贯穿基底210的第二导电插塞262,第二导电插塞262与电容240的第二电极243耦接。第二互联层272通过第二导电插塞262与电容240的第二电极243耦接,以实现对电容240的供电。

108.在另外一些实施例中,参照图所示,可采用第二导电插塞262的形成工艺形成第三导电插塞263,第三导电插塞263位于基底210远离电容240的一侧,贯穿基底210并且与栅缝隙结构251耦接,第二互联层272通过第三导电插塞263与栅缝隙结构251耦接。

109.第二互联层272可将存储器的电信号引出,与封装壳体的触点或者重布线层进行耦接,以实现存储器的封装。

110.在一些实施例中,参照图8所示,该制作方法还包括:

111.形成半导体结构;其中,半导体结构包括cmos器件290;

112.键合半导体结构、存储单元柱230以及电容240;其中,半导体结构位于电容240远离基底210的一端。

113.参照图8所示,半导体结构形成于电容240以及存储单元柱230的下方,半导体结构中包括cmos器件290以及第三互联层273,第三互联层273用于cmos器件290之间的电信号交互。

114.第一互联层271用于存储单元柱230、栅缝隙结构251、电容240或者台阶区的栅极层223上的导电插塞之间的电信号交互,在半导体结构以及第一互联层271之间设置焊盘264,键合半导体结构以及第一互联层271以实现电信号互联。半导体结构中的cmos器件290可配合电容240构成多种外围电路,以对存储单元柱230进行读写或者擦除操作。可以理解的是,焊盘264可形成于第一互联层271的键合表面和/或半导体结构的键合表面。焊盘264的组成材料包括:铜、铝、钛、金、银、铂、镍、钨或者锡等导电材料。

115.本公开实施例中的电容240与cmos器件290通过键合进行电信号交互,电容240与cmos器件290并不形成与同一个基底上,电容240的尺寸以及制作工艺并不会限制cmos器件290尺寸的缩小,提高电容240集成度的同时也可提高cmos器件290以及半导体结构中其他器件的集成度。

116.图2h示出了一种三维存储器的示意图。参照图2h所示,该三维存储器包括:基底210;

117.堆叠结构220’,位于基底210上;

118.存储单元柱230,贯穿堆叠结构220’;

119.电容240,贯穿堆叠结构220’,且与堆叠结构220’电隔离;沿着电容240的径向,电容240包括:第一电极241,围绕第一电极241的第一介电层242和第二电极243,第一介电层242位于第一电极241和第二电极243之间;

120.存储单元柱230与基底210耦接,第二电极243与基底210耦接。

121.参照图2h所示,堆叠结构220’包括相互层叠设置的栅极层223和层间绝缘层222,栅极层223作为三维存储器的字线。图中所示出的电容240和存储单元柱230仅为示例,本公开实施例对电容240和存储单元柱230的个数以及排布不作限制。可设置多个电容240构成电容240阵列,设置多个存储单元柱230构成存储阵列。

122.在一些实施例中,基底210可作为共源极为存储单元柱230供电。可通过基底210为存储单元柱230提供一个电压,配合存储单元柱230的字线以及位线电压对存储单元柱230进行读写或者擦除的操作。示例性的,在读或者写的操作中,基底210提供低电压,例如,0v或者接地电压;在擦除的操作中,基底210提供高电压,例如20~25v,将存储单元柱230中存储子层233的电子抽出到沟道层231中,或者将沟道层231中的空穴注入存储子层233与电子中和,以此来实现擦除。电容240中的第二电极243与基底210耦接,可与存储单元柱230共用共源极电压,对第一电极241施加其他电压,使第一电极241与第二电极243之间形成电压差,以在电路中发挥电容240的作用。

123.在一些实施例中,可将电容240设置在存储单元阵列的一端,设置贯穿基底210的隔离结构将基底210划分为两部分,实现对第二电极243以及存储单元柱230阵列分别供电。隔离结构可包括:贯穿基底210的栅缝隙结构251、贯穿基底210的底部选择栅切线等。

124.本公开实施例,设置贯穿堆叠结构220’的电容240,电容240的第二电极243与存储单元柱230都与基底210耦接。相较于将电容240设置于堆叠结构220’以外区域以构成外围电路,本公开中的电容240与存储单元柱230设置于堆叠结构220’中,电容240的尺寸不会限制外围电路中其他器件的集成度,提高电容240集成度的同时也可保持甚至提高外围电路的集成度。并且,本公开实施例中的电容240的第二电极243与存储单元柱230共同耦接基底210,可省略设置其他电极接触结构,降低制作成本。

125.在一些实施例中,堆叠结构220’包括核心区211和台阶区212,台阶区212位于核心区211的一端;电容240贯穿堆叠结构220’的核心区211;和/或,电容240贯穿堆叠结构220’的台阶区212。例如,一个核心区211可位于两个台阶区212之间。或者,一个台阶区212可位于两个核心区211之间。

126.参照图3所示,台阶区212可以具有多个不同高度的台阶,台阶区212中的一级台阶至少包括一层栅极层223以及与该栅极层223相邻的一层层间绝缘层222,栅极层223的端部位于台阶区212。电容240可仅设置于核心区211中,电容240与可与存储单元柱230相邻。电容240可仅设置于台阶区212中,不同的电容240可贯穿不同层数的台阶。电容240也可同时设置于核心区211以及台阶区212两个区域,或者两个区域的交界处。

127.继续参照图3所示,在堆叠结构220’的台阶区212形成沿z方向延伸的导电插塞,导电插塞与栅极层223位于台阶区的端部耦接,为栅极层223提供字线电压。

128.电容240设置于核心区211和/或台阶区212,可降低应力集中,电容240对堆叠结构220’提供支撑以减少或者省略支撑柱的设置,提高电容240集成度的同时也保持存储器的稳定性良好。

129.在一些实施例中,在堆叠结构220’的台阶区212设置沿z方向延伸的导电插塞,导电插塞与栅极层223位于台阶区212的端部耦接,为栅极层223提供字线电压。

130.在一些实施例中,多个存储单元柱230围绕至少一个电容240。

131.电容240可设置于核心区中,并与存储单元柱230相邻。电容240的数量可少于存储单元柱230的数量,存储单元柱230成阵列排布,电容240被存储单元柱230包围。

132.例如图4a所示的,电容240成n字形排布。还例如图4b所示的,多个电容240组成五边形来包围一个存储单元柱230。图4a和图4b中,电容240和存储单元柱230可共同组成矩形阵列,如图4a中所示出的两个沿x方向排列的两个矩形阵列,相邻阵列通过顶部选择栅切线

252隔开,每个矩形阵列包括沿x方向并列排布的4个行结构,每个行结构包括沿y方向排布的多个存储单元柱230和多个电容240。

133.本实施例将电容240分布在存储单元柱230之间,减少形成电容240后的应力分布不均现象,提高存储器的制作良率。

134.在一些实施例中,参照图2h所示,电容240延伸进基底210中,第一电极241包括柱状结构;第一介电层242围绕第二电极243的侧面和底部,第二电极243围绕第一介电层242的侧面的底部。

135.图2f示出了图2h中电容240的上表面在xoy表面的俯视图。结合图2h和图2f所示,第一电极241为贯穿堆叠结构220’的柱状结构,第一介电层242和第二电极243为膜结构,第一介电层242位于第一电极241和第二电极243之间。第一电极241除了用于承受电压对电容240供电外,还可用于对电容240以及对存储器提供支撑,提高存储器的制作良率,维持存储器的稳定性良好。柱状的第一电极241可提供更大面积的接触面,便于导电插塞与第一电极241顶部耦接,提高导电插塞与第一电极241的耦接性能。

136.在另外一些实施例中,参照图5b所示,电容240还包括绝缘的芯部246,第二电极243与第一电极241都为膜层结构,第一电极241、第一介电层242以及第二电极243围绕芯部246,芯部246用于对电容240的支撑。

137.在一些实施例中,参照图3和图7所示,三维存储器还包括导电块247,位于基底210与电容240之间;其中,导电块247与第二电极243耦接,且导电块247与基底210耦接。

138.导电块247耦接第二电极243和基底210,降低第二电极243和基底210之间的接触电阻。导电块247的组成材料包括:单晶硅、多晶硅、钨、金、银、铜、铝、钛或镍等。例如,本实施例的导电块247为掺杂的多晶硅。

139.在一些实施例中,在存储单元柱230和基底210之间也可设置导电块247,导电块247耦接沟道层231和基底210。

140.在一些实施例中,电容240还包括第二介电层244和第三介电层245,第二介电层244位于第三介电层245与第二电极243之间;第二介电层244围绕第二电极243的侧面,且第二介电层244暴露第二电极243的底部;第三介电层245围绕第二介电层244,且第三介电层245暴露第二电极243的底部;

141.其中,第三介电层245的介电常数大于二氧化硅的介电常数。

142.参照图2h和图2f所示,第三介电层245位于电容240的最外层,位于堆叠结构220’和第二介电层244之间。第二介电层244以及第三介电层245的组成材料包括:氧化硅、氮化硅、氮氧化硅或者高介电材料(高k材料)。通常将介电常数大于二氧化硅的介电常数的材料称为高介电材料,高介电材料包括:氧化铝、氧化钛、锆氧化、铪氧化或者氧化钌等。在达到相同绝缘性能的要求下,高介电材料所需的膜层厚度要比二氧化硅的膜层厚度要薄。

143.本实施例的第二介电层244可选用常用的二氧化硅,以降低制作成本,而第三介电层245选用高介电材料(例如,氧化铝)增加绝缘能力。在达到相同绝缘性能的要求下,本实施例相较于仅使用一层二氧化硅来电隔离叠层结构220和第二电极243,可以减少第二介电层244和第三介电层245的总厚度,有利于提高电容240的集成度。

144.在一些实施例中,电容240的直径与存储单元柱230的直径相同。

145.电容240的直径与存储单元柱230的直径相同,利于电容240与存储单元柱230套用

相同的制作工艺,还利于电容240与存储单元柱230执行相同的质量控制体系,包括但不限于:直径控制或者高度控制等。

146.在一些实施例,参照图7所示,该三维存储器还包括:

147.第二个堆叠结构220’,位于堆叠结构220’之上;

148.第二个存储单元柱230,贯穿第二个堆叠结构220’;

149.第二个电容240,贯穿第二个堆叠结构220’;

150.两个堆叠结构220’中的相互层叠设置的电容240耦接,两个堆叠结构220’中相互层叠设置的存储单元柱230耦接。

151.参照图7所示,两个相互层叠设置的两个电容240中的两个第二电极243进行耦接,两个电容240的第一电极241进行耦接,以实现上下电容240的耦接,增加电容240的电容量。两个相互层叠设置的两个存储单元柱230中的两个沟道层231耦接,增加存储单元柱230的存储容量。

152.在一些实施例中,参照图3所示,该三维存储器还包括:

153.第一导电插塞261a,位于电容240远离基底210的一侧,第一导电插塞261a与电容240耦接;

154.第一互联层271,位于第一导电插塞261远离电容240的一侧;

155.其中,第一互联层271与第一导电插塞261a和存储单元柱230耦接。

156.参照图3所示,在存储单元柱230远离基底210的一侧,设置第一导电插塞261a与存储单元柱230耦接。在一些示例中,与存储单元柱230耦接的第一导电插塞261b耦接到第一互联层271中的位线,电容240的第一电极241也可通过第一导电插塞261a耦接到位线中,通过位线来给第一电极241提供电压。在另外一些示例中,第一互联层271可包括多个电信号交互的布线层或者器件。例如,第一互联层271除了包括位线,还设置有其他的导电线,用以为电容240的第一电极241单独供电,扩大电容240的使用场景。

157.在一些实施例中,参照图8所示,该三维存储器还包括:

158.第二导电插塞262,位于基底210远离电容240的一侧;第二导电插塞262贯穿基底210,且与第二电极243耦接;

159.第二互联层272,位于第二导电插塞262远离电容240的一侧;第二互联层272与第二导电插塞262耦接。

160.第二互联层272通过第二导电插塞262与电容240的第二电极243耦接,以实现对电容240的供电。第二互联层272可将存储器的电信号引出,与封装壳体的触点或者重布线层进行耦接,以实现存储器的封装。

161.在一些实施例中,参照图8所示,三维存储器还包括第三导电插塞263,第三导电插塞263位于基底210与第二互联层272之间,第三导电插塞263贯穿基底210且与栅缝隙结构251耦接,第二互联层272通过第三导电插塞263为栅缝隙结构251供电。

162.在一些实施例中,参照图8所示,该三维存储器还包括:

163.半导体结构,包括cmos器件290;半导体结构位于电容240远离基底210的一端,半导体结构与电容240和存储单元柱230键合。

164.继续参照图8所示,半导体结构为于电容240以及存储单元柱230的下方,半导体结构中包括cmos器件290以及第三互联层273,第三互联层273用于cmos器件290之间的电信号

交互。第一互联层271用于存储单元柱230、栅缝隙结构251、电容240或者台阶区的栅极层223上的导电插塞之间的电信号交互,在半导体结构以及第一互联层271之间设置焊盘264,键合半导体结构以及第一互联层271以实现电信号互联。半导体结构中的cmos器件290可配合电容240构成多种外围电路,以对存储单元柱230进行读写或者擦除操作。焊盘264可设置于第一互联层271的键合表面,和/或半导体结构的键合表面。

165.本公开实施例中的电容240与cmos器件290通过键合进行电信号交互,电容240与cmos器件290并不设置在同一个基底上,电容240的尺寸以及排布方式并不会限制cmos器件290尺寸的缩小,提高电容240集成度的同时也可提高cmos器件290以及半导体结构中其他器件的集成度。

166.在一些实施例中,电容240被配置为电荷泵的电容器,为三维存储器提供电压。

167.电荷泵中会使用多个电容器,并将电容器进行串联或者并联,利用电容器的充电或者放电来实现对输入电压的升压、降压或者负压等电压转换功能。

168.本实施例中的电容240可被配置为电荷泵的电容器,实现电压的升压、降压或者负压的转换。示例性的,三维存储器的电源模块提供电压为1.5v,在对存储单元柱230进行写入(编程)操作时,需要7v至8v的字线电压来进行写入,可利用电荷泵将1.5v的输入电压经过升压后,输出较高的编程电压给到字线以完成写入操作。需要强调的是,示例的所有电压仅用于解释说明,本实施例的三维存储器内部的不同模块具有不同的操作电压,对此不作限制。

169.在一些实施例中,电容240被配置为解耦电容器,用以减小三维存储器内的噪声干扰。

170.三维存储器中不同模块,执行不同的操作时的操作电压也不同。本实施例的电容240可被配置为解耦电容器,用于降低不同电压的噪声干扰。电容240可被配置于各个模块的输入端或者输出端,也可被配置于模块内部。模块可包括但不限于:存储阵列,电压发生器,页缓存器,列解码器或者行解码器等。

171.图9是根据本公开实施例示出的一种包括存储系统的系统900块图。

172.参照图9所示,一种存储系统902,包括:

173.存储器904,包括上述实施例中图8所示的三维存储器;

174.存储器控制器906,耦合到存储器904并且被配置为控制存储器。

175.具体的,系统900可以是移动电话、台式计算机、膝上型计算机、平板计算机、车辆计算机、游戏控制台、打印机、定位设备、可穿戴电子设备、智能传感器、虚拟现实(vr)设备、增强现实(ar)设备或者其中具有储存器的任何其他合适的电子设备。

176.如图9中所示,系统900可以包括主机908和存储系统902,存储系统902具有一个或多个存储器904和存储器控制器906。主机908可以是电子设备的处理器(例如,中央处理单元(cpu))或者片上系统(soc)(例如,应用处理器(ap))。主机908可以被配置为将数据发送到存储器904或从存储器904接收数据。

177.存储器904可以包括本公开实施例中的三维存储器,例如,图7和图8示出的包括存储单元柱230和电容240的三维存储器。如下文详细说明的,存储器904(例如,nand闪存存储器(例如,三维(3d)nand闪存存储器))可以在擦除操作期间具有来自耦合到未选定字线的驱动晶体管(例如,串驱动器)的减小的漏电流,这允许驱动晶体管的进一步尺寸缩小。

178.在一些实施例中,存储器控制器906耦合到存储器904和主机908,并且被配置为控制存储器904。存储器控制器906可以管理存储在存储器904中的数据,并且与主机908通信。

179.在一些实施例中,存储器控制器906被设计为用于在低占空比环境中操作,如安全数字(sd)卡、紧凑型闪存(cf)卡、通用串行总线(usb)闪存驱动器、或用于在诸如个人计算器、数字相机、移动电话等的电子设备中使用的其他介质。

180.在一些实施例中,存储器控制器906被设计为用于在高占空比环境ssd或嵌入式多媒体卡(emmc)中操作,ssd或emmc用作诸如智能电话、平板计算机、膝上型计算机等的移动设备的数据储存器以及企业存储器阵列。存储器控制器906可以被配置为控制存储器904的操作,例如读取、擦除和编程操作。存储器控制器906还可以被配置为管理关于存储在或要存储在存储器904中的数据的各种功能,包括但不限于坏块管理、垃圾收集、逻辑到物理地址转换、损耗均衡等。

181.在一些实施例中,存储器控制器906还被配置为处理关于从存储器904读取的或者被写入到存储器904的数据的纠错码(ecc)。存储器控制器906还可以执行任何其他合适的功能,例如,格式化存储器904。存储器控制器906可以根据特定通信协议与外部设备(例如,主机908)通信。例如,存储器控制器906可以通过各种接口协议中的至少一种与外部设备通信,接口协议例如usb协议、mmc协议、外围部件互连(pci)协议、pci高速(pci-e)协议、高级技术附件(ata)协议、串行ata协议、并行ata协议、小型计算机小型接口(scsi)协议、增强型小型磁盘接口(esdi)协议、集成驱动电子设备(ide)协议、firewire协议等。

182.存储器控制器906和一个或多个存储器904可以集成到各种类型的存储设备中,例如,包括在相同封装(例如,通用闪存存储(ufs)封装或emmc封装)中。也就是说,存储系统902可以实施并且封装到不同类型的终端电子产品中。

183.参照图10a所示,在一些实施例中,存储器控制器906和单个存储器904可以集成到存储器卡1002中。存储器卡1002可以包括pc卡(pcmcia,个人计算机存储器卡国际协会)、cf卡、智能媒体(sm)卡、存储器棒、多媒体卡(mmc、rs-mmc、mmcmicro)、sd卡(sd、minisd、microsd、sdhc)、ufs等。存储器卡1002还可以包括将存储器卡1002与主机(例如,图5中的主机908)耦合的存储器卡连接器1004。

184.参照图10b所示,在一些实施例中,存储器控制器906和多个存储器904可以集成到ssd 1006中。ssd 1006还可以包括将ssd 1006与主机(例如,图5中的主机908)耦合的ssd连接器1008。

185.在一些实施例中,ssd 1006的存储容量和/或操作速度可大于存储器卡1002的存储容量和/或操作速度。

186.图11是根据本公开实施例示出的一种包括有外围电路的存储器1100的示意电路图。存储器1100可以是图9中的存储器904的示例。参照图11所示,存储器1100可以包括存储阵列1101和耦合到存储阵列1101的外围电路1102。存储阵列1101可以是nand闪存存储阵列,其中,存储单元1106以nand存储串1108的阵列的形式提供,每个nand存储串1108在基底(未示出)上方垂直地延伸。图11中示出的存储阵列1101可以是图7和图8中示出的存储阵列(包括多个存储单元柱230)的电路图。

187.在一些实施例中,每个nand存储串1108包括串联耦合并且垂直地堆叠的多个存储单元1106。每个存储单元1106可以保持连续模拟值,例如,电压或电荷,其取决于在存储单

元1106的区域内捕获的电子的数量。每个存储单元1106可以是包括浮栅晶体管的浮栅类型的存储单元,或者是包括电荷捕获晶体管的电荷捕获类型的存储单元。

188.图11中的存储串1108可包括图7和图8中的任意一个存储单元柱230。一个存储单元1106可包括,在x方向上,一个栅极层223对应的存储单元柱230的部分沟道层和部分功能层。栅极层223(即图11中的字线1118)的层数可确定存储单元1106的数量。

189.在一些实施例中,每个存储单元1106是具有两种可能的存储器状态并且因此可以存储一位数据的单级单元(slc)。例如,第一存储器状态“0”可以对应于第一电压范围,并且第二存储器状态“1”可以对应于第二电压范围。

190.在一些实施例中,每个存储单元1106是能够在多于四个的存储器状态中存储多于单个位的数据的多级单元(mlc)。例如,mlc可以每单元存储两位,每单元存储三位(又被称为三级单元(tlc)),或者每单元存储四位(又被称为四级单元(qlc))。每个mlc可以被编程为采取可能的标称存储值的范围。在一个示例中,如果每个mlc存储两位数据,则mlc可以被编程为通过将三个可能的标称存储值中的一个写入到该单元而从擦除状态采取三个可能的编程级中的一个。第四标称存储值可以用于擦除状态。

191.参照图11所示,每个nand存储串1108可以包括在其源极端处的源极选择栅极(ssg)1110和在其漏极端处的漏极选择栅极(dsg)1112。ssg 1110和dsg 1112可以被配置为在读取和编程操作期间激活选定的nand存储串1108(存储阵列的列)。

192.在一些实施例中,同一块1104中的nand存储串1108的源极通过同一源极线(sl)1114(例如,公共sl)耦合。同一块1104中的所有nand存储串1108可具有阵列公共源极(acs)。

193.在一些实施例中,每个nand存储串1108的dsg 1112耦合到相应的位线1116,可以经由输出总线(未示出)从位线1116读取或写入数据。

194.在一些实施例中,每个nand存储串1108被配置为通过经由一个或多个dsg线1113将选择电压(例如,高于具有dsg 1112的晶体管的阈值电压)或取消选择电压(例如,0v)施加到相应的dsg 1112和/或通过经由一个或多个ssg线1115将选择电压(例如,高于具有ssg 1110的晶体管的阈值电压)或取消选择电压(例如,0v)施加到相应的ssg 1110而被选择或被取消选择。

195.参照图11所示,nand存储串1108可以被组织为多个块1104,多个块1104的每一个可以具有公共源极线1114(例如,耦合到地)。

196.在一些实施例中,每个块1104可以是用于擦除操作的基本数据单位,即,同一块1104上的所有存储单元1106可同时被擦除。为了擦除选定块1104a中的存储单元1106,可以用擦除电压(vers)(例如,高正电压(例如,20v或更高))偏置耦合到选定块1104a以及与选定块1104a在同一面中的未选定块1104b的源极线1114。

197.可以理解的是,可以在半块级、在四分之一块级或者在具有任何合适数量的块或块的任何合适的分数的级执行擦除操作。相邻nand存储串1108的存储单元1106可以通过字线1118耦合,字线1118选择存储单元1106的哪一行受读取和编程操作的影响。

198.在一些实施例中,每个字线1118耦合到存储单元1106的页1120,页1120可以是用于编程操作的基本数据单位。以位为单位的一页1120的大小可以与一个块1104中由字线1118耦合的nand存储串1108的数量相关。每个字线1118可以包括在相应页1120中的每个存

储单元1106处的多个控制栅极(栅极电极)以及耦合控制栅极的栅极线。

199.继续参照图11所示,外围电路1102可以通过位线1116、字线1118、源极线1114、ssg线1115和dsg线1113耦合到存储阵列1101。外围电路1102可以包括任何合适的模拟、数字以及混合信号电路,以用于通过经由位线1116、字线1118、源极线1114、ssg线1115和dsg线1113将电压信号和/或电流信号施加到每个目标存储单元1106以及从每个目标存储单元1106感测电压信号和/或电流信号来促进存储阵列1101的操作。外围电路1102可以包括使用金属-氧化物-半导体(mos)技术形成的各种类型的外围电路。例如,外围电路1102可包括图8中所示出的键合耦接的电容240以及cmos器件290。

200.例如,图12示出了一些示例性外围电路,外围电路1102可包括页缓冲器/感测放大器1204、列解码器/位线驱动器1206、行解码器/字线驱动器1208、电压发生器1210、控制逻辑单元1212、寄存器1214、接口1216和数据总线1218。可以理解的是,在一些实施例中,还可以包括图12中未示出的附加外围电路。

201.结合图11和图12所示,页缓冲器/感测放大器1204可以被配置为根据来自控制逻辑单元1212的控制信号从存储阵列1101读取数据以及向存储阵列1101编程(写入)数据。

202.在一些实施例中,页缓冲器/感测放大器1204可以存储要被编程到存储阵列1101的一个页1120中的一页编程数据(写入数据)。在另外一些实施例中,页缓冲器/感测放大器1204可以执行编程验证操作,以确保数据已经被正确地编程到耦合到选定字线1118的存储单元1106中。在又一些实施例中,页缓冲器/感测放大器1204还可以感测来自位线1116的表示存储在存储单元1106中的数据位的低功率信号,并且在读取操作中将小电压摆幅放大到可识别的逻辑电平。列解码器/位线驱动器1206可以被配置为由控制逻辑单元1212控制,并且通过施加从电压发生器1210生成的位线电压来选择一个或多个nand存储串1108。

203.行解码器/字线驱动器1208可以被配置为由控制逻辑单元1212控制,并且选择/取消选择存储阵列1101的块1104并且选择/取消选择块1104的字线1118。行解码器/字线驱动器1208还可以被配置为使用从电压发生器1210生成的字线电压来驱动字线1118。

204.在一些实施例中,行解码器/字线驱动器1208还可以选择/取消选择并且驱动ssg线1115和dsg线1113。如下文详细描述的,行解码器/字线驱动器1208被配置为对耦合到(一个或多个)选定字线1118的存储单元1106执行擦除操作。电压发生器1210可以被配置为由控制逻辑单元1212控制,并且生成要被供应到存储阵列1101的字线电压(例如,读取电压、编程电压、通过电压、局部电压、验证电压等)、位线电压和源极线电压。

205.控制逻辑单元1212可以耦合到上文描述的每个外围电路,并且被配置为控制每个外围电路的操作。寄存器1214可以耦合到控制逻辑单元1212,并且包括状态寄存器、命令寄存器和地址寄存器,以用于存储用于控制每个外围电路的操作的状态信息、命令操作码(op码)和命令地址。接口1216可以耦合到控制逻辑单元1212,并且充当控制缓冲器,以缓冲从主机(未示出)接收的控制命令并且并将其中继到控制逻辑单元1212,以及缓冲从控制逻辑单元1212接收的状态信息并且将其中继到主机。接口1216还可以经由数据总线1218耦合到列解码器/位线驱动器1206,并且充当数据i/o接口和数据缓冲器,以缓冲数据并且将其中继到存储阵列1101或从存储阵列1101中继或缓冲数据。以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开

的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1