半导体结构及其形成方法与流程

本公开涉及半导体,涉及但不限于一种半导体结构及其形成方法。

背景技术:

1、半导体结构的制造技术中,通常利用光阻及掩膜层,结合光刻及刻蚀工艺形成所需图案,然而,受到光刻工艺局限性的影响,容易使得形成的所需图案产生偏差,从而影响半导体结构的制备良率。

2、以动态随机存储器(dynamic random access memory,dram)的制造为例,在动态随机存储器的电容管的形成工艺中,通常采用自对准四重成像技术(self-alignedquadruple patterning,saqp)进行图案的转移,由于图案的关键尺寸(criticaldimension,cd)不断缩小,图案密度越来越大,在刻蚀过程中由于刻蚀负载效应,使得侧墙图案的关键尺寸不能准确控制,且在侧墙图案形成过程中,由于刻蚀选择比的问题使得图案底部呈凹凸状,进而影响后续的图案转移,破坏最终形成电容管结构,例如,使得最后形成的电容孔尺寸均匀性差,且会出现刻蚀不足、刻蚀孔桥接以及孔错位等缺陷。

技术实现思路

1、有鉴于此,本公开实施例提供一种半导体结构及其形成方法。

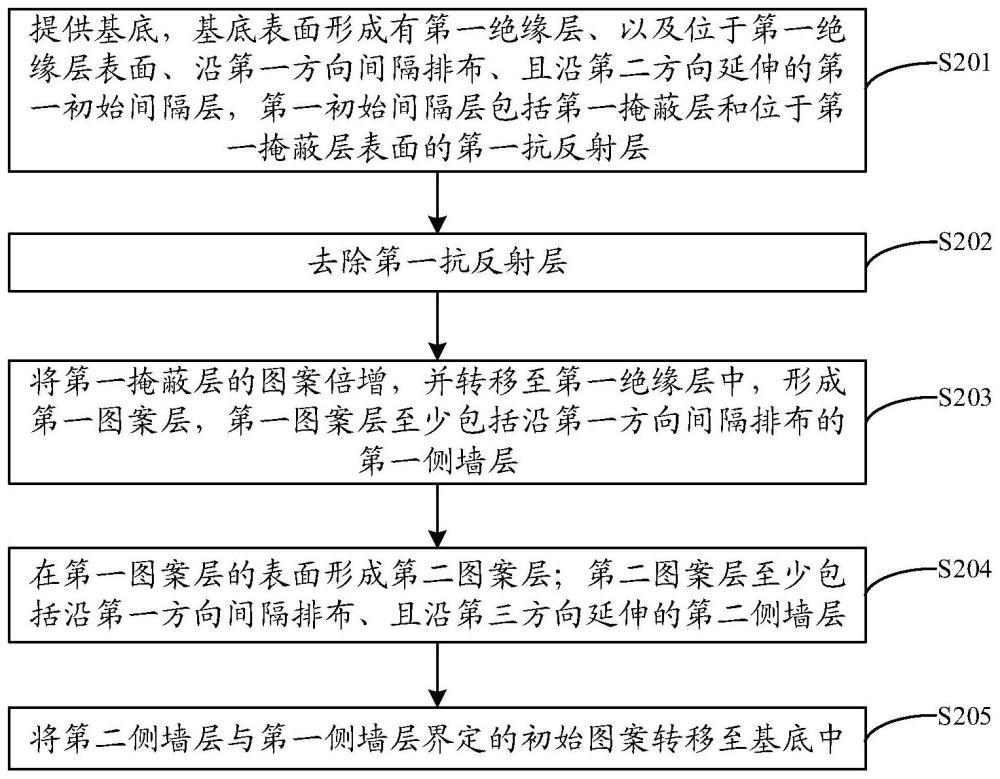

2、第一方面,本公开实施例提供一种半导体结构的形成方法,所述方法包括:

3、提供基底,所述基底表面形成有第一绝缘层、以及位于所述第一绝缘层表面、沿第一方向间隔排布、且沿第二方向延伸的第一初始间隔层,所述第一初始间隔层包括第一掩蔽层和位于所述第一掩蔽层表面的第一抗反射层;

4、去除所述第一抗反射层;

5、将所述第一掩蔽层的图案倍增,并转移至所述第一绝缘层中,形成第一图案层,所述第一图案层至少包括沿所述第一方向间隔排布的第一侧墙层;

6、在所述第一图案层的表面形成第二图案层;所述第二图案层至少包括沿所述第一方向间隔排布、且沿第三方向延伸的第二侧墙层;所述第一方向、所述第二方向与所述第三方向为所述基底所在平面内任意三个方向;

7、将所述第二侧墙层与所述第一侧墙层界定的初始图案转移至所述基底中。

8、在一些实施例中,所述第一抗反射层与所述基底之间的刻蚀选择比为所述第一绝缘层与所述基底之间的刻蚀选择比的3~10倍。

9、在一些实施例中,将所述第一掩蔽层的图案倍增,并转移至所述第一绝缘层中,包括:

10、在所述第一掩蔽层的表面和所述第一绝缘层的表面形成第二初始覆盖层;

11、去除位于所述第一掩蔽层顶表面和所述第一绝缘层表面的所述第二初始覆盖层,保留的位于所述第一掩蔽层侧壁的所述第二初始覆盖层,构成所述第一侧墙层。

12、在一些实施例中,所述第一图案层还包括第一牺牲层;在形成所述第一侧墙层之后,半导体结构的形成方法还包括:

13、在所述第一侧墙层之间的间隙中形成所述第一牺牲层;

14、其中,所述第一侧墙层与所述第一牺牲层的表面平齐。

15、在一些实施例中,所述第一初始间隔层通过以下步骤形成:

16、在所述第一绝缘层表面依次形成第一初始掩膜层和第二初始掩膜层;所述第一初始掩膜层包括所述第一掩蔽层和所述第一抗反射层;

17、刻蚀所述第二初始掩膜层,形成沿所述第一方向间隔排列的第二初始间隔层;

18、在所述第二初始间隔层的侧壁形成第一覆盖层;

19、通过所述第一覆盖层刻蚀所述第一初始掩膜层,形成沿所述第一方向交替排列的所述第一初始间隔层。

20、在一些实施例中,所述第二初始间隔层通过以下步骤形成:

21、在所述第二初始掩膜层的表面形成具有第一预设图案的第一光刻胶层;其中,所述第一预设图案包括沿所述第一方向依次排列、且沿所述第二方向延伸的多个第一子图案,所述第一子图案暴露出部分第二初始掩膜层;

22、去除所述第一子图案暴露出的所述第二初始掩膜层,形成所述第二初始间隔层。

23、在一些实施例中,所述第二图案层通过以下步骤形成:

24、在所述第一图案层表面形成第二绝缘层、以及位于所述第二绝缘层表面、沿所述第一方向间隔排列、且沿所述第三方向延伸的第三初始间隔层;所述第三初始间隔层包括第三掩蔽层和位于所述第三掩蔽层表面的第三抗反射层;

25、去除所述第三抗反射层;其中,所述第三抗反射层与所述基底之间的刻蚀选择比大于所述第二绝缘层与所述基底之间的刻蚀选择比;

26、将所述第三掩蔽层的图案倍增,并转移至所述第二绝缘层中,形成所述第二图案层。

27、在一些实施例中,所述第三抗反射层与所述基底之间的刻蚀选择比为所述第二绝缘层与所述基底之间的刻蚀选择比的3~10倍。

28、在一些实施例中,将所述第三掩蔽层的图案倍增,并转移至所述第二绝缘层中,包括:

29、在所述第三掩蔽层的表面和所述第二绝缘层的表面形成第四初始覆盖层;

30、去除位于所述第三掩蔽层顶表面和所述第一绝缘层表面的所述第四初始覆盖层,保留的位于所述第三掩蔽层侧壁的所述第四初始覆盖层,构成所述第二侧墙层。

31、在一些实施例中,所述第二图案层还包括第二牺牲层;在形成所述第二侧墙层之后,半导体结构的形成方法还包括:

32、在所述第二侧墙层之间的间隙中形成所述第二牺牲层;

33、其中,所述第二侧墙层与所述第二牺牲层的底表面平齐。

34、在一些实施例中,所述第三初始间隔层通过以下步骤形成:

35、在所述第二绝缘层表面依次形成第三初始掩膜层和第四初始掩膜层;所述第三初始掩膜层包括所述第三掩蔽层和所述第三抗反射层;

36、刻蚀所述第四初始掩膜层,形成沿所述第一方向间隔排列的第四初始间隔层;

37、在所述第四初始间隔层的侧壁形成第三覆盖层;

38、通过所述第三覆盖层刻蚀所述第三初始掩膜层,形成沿所述第一方向交替排列的所述第三初始间隔层。

39、在一些实施例中,所述第四初始间隔层通过以下步骤形成:

40、在所述第四初始掩膜层的表面形成具有第二预设图案的第二光刻胶层;其中,所述第二预设图案包括沿所述第一方向依次排列、且沿所述第三方向延伸的多个第二子图案,所述第二子图案暴露出部分第四初始掩膜层;

41、去除所述第二子图案暴露出的所述第四初始掩膜层,形成所述第四初始间隔层。

42、在一些实施例中,所述基底包括阵列区域和外围区域,在形成所述第二图案层之后,所述方法还包括:

43、在所述第二图案层表面具有第三预设图案的第三光刻胶层,其中,所述第三预设图案包括暴露出远离所述外围区域的部分所述阵列区域;

44、将所述初始图案转移至所述第三预设图案暴露出的所述阵列区域对应的基底中。

45、在一些实施例中,在形成所述第一图案层之后,且在形成所述第二图案层之前,半导体结构的形成方法还包括:

46、形成位于所述第一图案层表面的介质层。

47、在一些实施例中,所述基底包括第四掩膜层;将所述第二侧墙层与所述第一侧墙层界定的初始图案转移至所述基底中,包括:

48、以所述第一侧墙层和所述第二侧墙层为掩膜,将所述初始图案转移至所述第四掩膜层中,形成具有初始图案的第四掩膜层;所述初始图案包括多个第三子图案。

49、在一些实施例中,所述基底还包括衬底,所述第四掩膜层位于所述衬底表面;在形成具有所述初始图案的第四掩膜层之后,所述方法还包括:

50、去除所述第三子图案暴露的部分所述衬底,以将所述初始图案转移至所述衬底中。

51、在一些实施例中,所述基底还包括叠层结构,所述第四掩膜层位于所述叠层结构表面;在形成具有所述初始图案的第四掩膜层之后,所述方法还包括:

52、去除所述第三子图案暴露的部分所述叠层结构,以将所述初始图案转移至所述叠层结构中。

53、在一些实施例中,所述初始图案包括电容孔图案。

54、第二方面,本公开实施例提供一种半导体结构,所述半导体结构通过上述权利要求所述的半导体结构的形成方法形成,所述半导体结构包括:

55、基底;所述基底包括初始图案;所述初始图案通过第一图案层中的第一侧墙层和第二图案层中的第二侧墙层界定;

56、其中,所述第一图案层位于所述基底的表面,所述第一侧墙层沿所述第一方向间隔排布、且沿第二方向延伸;所述第二图案层位于所述第一图案层的表面,所述第二侧墙层沿所述第一方向间隔排布、且沿第三方向延伸;所述第一方向、所述第二方向与所述第三方向为所述基底所在平面内任意三个方向。

57、本公开实施例提供的半导体结构及其形成方法,在基底表面形成有第一绝缘层、以及位于第一绝缘层表面、沿第一方向间隔排布、且沿第二方向延伸的第一初始间隔层,第一初始间隔层包括第一掩蔽层和位于第一掩蔽层表面的第一抗反射层,在形成第一图案层的过程中,由于第一抗反射层与基底之间的刻蚀选择比大于第一绝缘层与基底之间的刻蚀选择比,因此,在去除第一抗反射层的过程中不会损伤第一绝缘层,使得第一掩蔽层底部的图案不会出现凹凸结构,减小了第一掩蔽层向下转移过程中的刻蚀负载效应,如此,可以使得第一侧墙层的关键尺寸容易控制,不会影响后续的图案转移,进而也不会破坏最终形成半导体结构。

- 还没有人留言评论。精彩留言会获得点赞!