半导体封装测试装置的制作方法

本发明涉及半导体封装测试装置,更详细地,涉及用于检查由下部封装和上部封装上下层叠而成的封装体叠层型(pop)半导体封装是否正常工作的半导体封装测试装置。

背景技术:

1、通常,半导体封装由微细的电子电路以高密度集成而成,在制造工序中,将进行判断各个电子电路是否正常的相关测试工序。测试工序是指通过测试半导体封装是否正常工作来筛选出优质品及残次品的工序。

2、在半导体封装的测试过程中,将用到使半导体封装的端子与用于施加测试信号的测试器电连接的测试装置。测试装置根据作为测试对象的半导体封装的种类具有多种结构。

3、最近,随着可最大限度地减小部件尺寸且快速实现信号传输的封装体叠层型(pop)半导体封装的使用增加,对用于测试这种半导体封装的测试装置的需求也逐渐增加。

4、封装体叠层方式是指将具备不同功能的封装依次层叠在一个封装上(层叠型)。

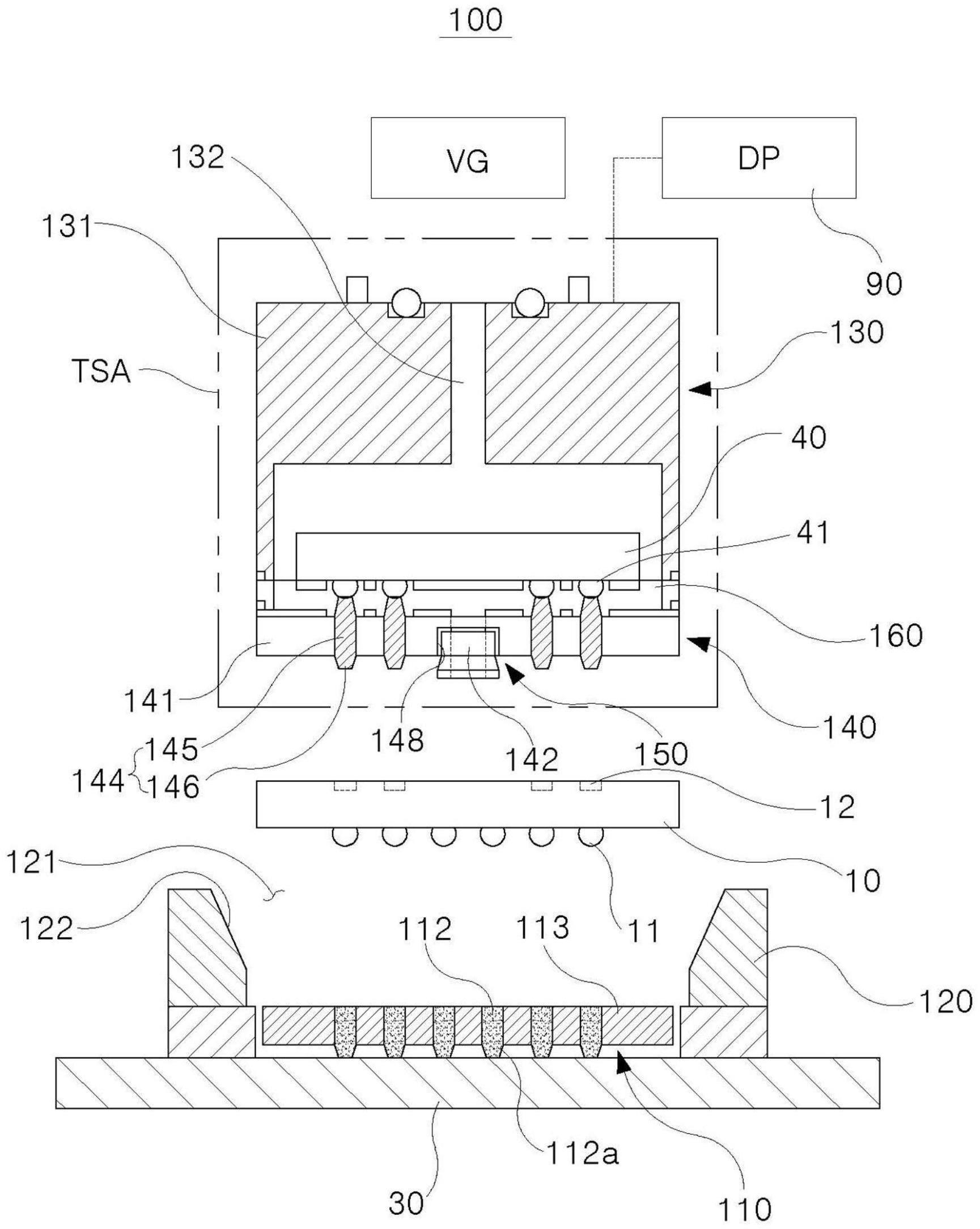

5、由于封装体叠层方式可最大限度地减少连接配线的长度,因此,可最大限度地减少二维排列时所发生的信号延迟、阻抗失配等的损失,而且,空间上使用垂直方向,因此,可最大限度地增加单位面积的安装面积来实现大容量、超小型部件。

6、图1为示出用于测试封装体叠层型半导体封装的现有测试装置的图,图2为示出现有测试装置的工作的图。

7、如图1及图2所示,现有的测试装置1包括:推动器50,可从驱动部(dp)90接收动力来上下移动,在内部形成有真空空间(真空区域);上部封装40,安装在推动器50内;第二检查用电路板20,安装有上部封装40;上部插口70,与第二检查用电路板20的下部相结合;真空拾取器71,配置在上部插口70的下部,以可真空吸附下部封装10;以及下部插口60,安装在第一检查用电路板(测试器)30(在本说明书中,将检查用电路板表示为测试器)。

8、上部插口组件tsa包括:推动器50;上部封装40,安装在推动器50内;第二检查用电路板20,安装有上部封装40;上部插口70,与第二检查用电路板20的下部相联接;以及真空拾取器71,配置在上部插口70的下部。

9、上部封装40在下部设置有端子41,由作为优质品预先筛选的封装构成,由可用于检查下部封装10是否正常工作的golden device构成,下部封装10可以为设置有下部端子11和上部端子(未图示)的受检设备。

10、上部插口70和下部插口60分别包括第二导电部73及第一导电部61,多个导电粒子沿着厚度方向排列形成在弹性绝缘物质内。

11、下部插口60安装在第一检查用电路板(测试器)30上,在下部插口60的上部面设置有下部封装10,其下部封装10的上部面与上部插口70相联接,使得由测试器30施加的检查电流经过下部封装10并通过第二检查用电路板20施加到上部封装40来执行电测试。在图1及图2中,附图标记11表示端子,附图标记80表示引导外壳。

12、在现有的测试装置1中,需要使从真空发生装置vg产生的真空压力传递到真空拾取器71来吸附下部封装10并使其向下部插口60施加压力,因此,推动器50的内部空间应维持真空状态,在真空发生装置vg与真空拾取器71之间应形成有真空管线vl。

13、然而,在直接连接上述封装40与上部插口70的情况下,为了在上部封装的端子41与上部插口的第二导电部73之间形成电通路,上部封装的端子41压缩上部插口的第二导电部73并结合。因此,在上部封装40与上部插口70之间并未充分形成真空管线vl。

14、因此,在现有的测试装置1中,为了在上部封装40与上部插口70之间形成真空管线而在上部封装40与上部插口70之间配置第二检查用电路板20。

15、随着在第二检查用电路板20的端子(未图示)焊接上部封装40的端子41来在第二检查用电路板20上安装上部封装40,因此,在上部封装40的下表面与第二检查用电路板20之间形成上部封装端子41的高度程度的空间,通过上述空间形成使得从真空发生装置vg产生的真空压力传递到真空拾取器71的真空管线。

16、图2示出了从真空发生装置vg产生的真空压力经过上部封装40与第二检查用电路板20之间的空间传递到真空拾取器71的真空管线vl。

17、随着从真空发生装置vg产生的真空压力通过形成在上部插口70中心和第二检查用电路板20中心的孔21流入之后,进入到上部封装40与第二检查用电路板20之间的空间,之后,经过推动器50的内壁与上部封装40之间的空间进入到位于推动器50外部的真空发生装置vg侧。

18、但是,现有的测试装置1存在如下问题,即,为了确保真空管线vl而需要必备安装上部封装40的第二检查用电路板20,由于受到存在于第二检查用电路板20的端子(未图示)与上部封装40的端子41之间的水分等的影响而无法正常进行焊接,从而引起焊接不良的问题,即使进行焊接,也会因无法均匀地焊接而发生的上部封装40的端子41之间的厚度偏差问题,在上部封装40的端子41发生裂纹(crack)等的问题。

19、并且,需要制造第二检查用电路板20的工序及在上部封装40层叠第二检查用电路板20的工序,从而制造将消耗大量时间,因设置第二检查用电路板20而导致整体负荷的增加,从而引发焊球端子的裂纹等的不良。由于这种不良,随着需要对封装的焊球端子进行额外检查,将发生因整体工序的增加而导致的成本上升的问题。

20、并且,随着设置第二检查用电路板20,上部封装40与下部封装10之间的信号传输路径(signal path)变长,从而发生信号延迟和信号失真的问题,因此,将发生无法对高速工作的半导体封装进行精密检查的问题。

21、现有技术文献

22、专利文献

23、专利文献0001:韩国公开专利公报第2015-0106848号(公开日:2015年09月22日)

24、专利文献0002:韩国公开专利公报第10-1555965号(授权日:2015年09月25日)

技术实现思路

1、本发明用于解决如上所述的问题而发明,本发明的目的在于,提供如下的半导体封装测试装置,即,在封装体叠层方式的半导体测试装置中,即使去除第二检查用电路板,也能够以确保真空管线的方式改变装置结构,由此,可通过缩短信号传输路径的长度来对高速工作的半导体封装进行精密检查,并且,可有效执行电特性检查来大幅缩减检查成本及检查时间。

2、为了实现上述目的,本发明的半导体封装测试装置可包括:下部插口,安装在用于提供测试信号的测试器,与下部封装的下部端子相联接,使得上述下部封装与上述测试器实现电连接;推动器,可从驱动部接收动力来上下移动;上部插口,安装在上述推动器并具有导电部,上述导电部设置在上部封装的下部并与上部封装的下部端子实现电连接;真空拾取器,安装在上述上部插口的中心,以能够真空吸附上述下部封装;以及非弹性绝缘片,设置在上述上部插口与上述上部封装之间,在与上述上部封装的端子和上述导电部相对应的位置形成有贯通孔,在与上述上部插口相对应的下表面形成有真空空间部。

3、并且,上述非弹性绝缘片的真空空间部可呈长凹槽形状。

4、并且,可在上述真空空间部形成有用于补偿上述凹槽的高度的多个防变形柱体。

5、并且,上述非弹性绝缘片可通过在聚酰亚胺(pi)、fr4、工程塑胶或金属形成绝缘镀层来制成。

6、并且,供给到上述推动器的真空压力可经过上述真空空间部施加到上述真空拾取器。

7、并且,上述上部插口能够以通过粘结剂真空密封的方式附着在上述推动器。

8、并且,在上述上部插口的导电部中,多个导电粒子可沿着厚度方向排列形成在弹性绝缘物质内。

9、并且,上述上部封装或上述下部封装的下部端子可以为焊球型或焊盘型中的一种。

10、而且,本发明的半导体封装测试装置包括:下部插口,安装在用于提供测试信号的测试器,与下部封装的下部端子相联接,使得上述下部封装与上述测试器实现电连接;推动器,可从驱动部接收动力来上下移动;以及上部插口,安装在上述推动器并具有导电部,上述导电部设置在作为优质封装的上部封装的下部并与上部封装的下部端子实现电连接,上述上部封装的下部端子采用焊球型,可在与上述导电部直接接触的上述上部封装的下部端子的上部形成有抗氧化金属镀层。

11、并且,可在上述上部封装的下部端子的表面与上述抗氧化金属镀层之间形成有镀镍层。

12、并且,上述抗氧化金属可以为金、钯、铑、钴或其中两种以上金属的合金。

13、如上所述,本发明具有如下效果,即,当测试半导体封装时,由测试器施加的测试信号将施加到下部插口、下部封装、上部插口及上部封装,在本发明中,可通过去除配置在现有上部插口组件的第二检查用电路板并在上部插口与上述封装之间设置具有真空空间部的非弹性绝缘片来确保上部插口组件内的真空管线,以使从真空发生装置产生的真空压力顺畅地施加到真空拾取器。

14、并且,本发明具有如下的效果,即,即使不使用第二检查用电路板,也可同时确认下部封装是否处于正常状态及在与上部封装相结合的状态下是否正常工作,因此,可大幅缩短上部封装与下部封装之间的信号传输路径(signal path)长度来防止在高速信号传输过程中发生的信号延迟和失真,而且,可对高速工作的半导体封装进行精密测试,因此,可通过有效执行电特性检查来大幅减少测试成本及检查时间。

15、并且,本发明具有如下的效果,即,采用上部插口组件的结构要素采用通过粘结剂结合的结构来使得上部封装的分离及结合变得简单,并且,对粘结部分进行真空密封(sealing)处理来防止发生真空压力损失,由此,通过粘结剂缓和下部封装与上部插口组件接触时所产生的冲击。

16、并且,采用真空压力向用于吸附推动器和下部封装的真空拾取器之间泄漏的风险小,并使真空压力从真空发生装置稳定传递到真空拾取器的结构,由此,当拾取下部封装时,可降低拾取错误。

17、并且,本发明具有如下的效果,即,在由优质封装组成的上部封装的下部端子形成有抗氧化金属镀层,因此,即使在反复使用的情况下,也可防止与导电部之间的接触电阻增加,从而提高检查下部封装的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!