包含组合逻辑单元的集成电路的制作方法

1.本公开大体上涉及集成电路,且更具体来说,涉及包含组合逻辑单元的集成电路,以及操作及形成所述集成电路的方法。

背景技术:

2.逻辑单元包含经配置以执行逻辑功能的晶体管,例如(但不限于)反相器、nand门及nor门。标准逻辑单元的晶体管以输出驱动电流容量执行逻辑功能。数字库中的标准逻辑单元在标准高度及不同宽度内执行单个逻辑功能。

3.还存在以较低功率电平执行逻辑功能的逻辑单元(也称为“低驱动逻辑单元”)。低驱动标准逻辑单元的晶体管以较低输出驱动电流容量执行逻辑功能。数字库中的低驱动标准逻辑单元也在标准高度及不同宽度内执行单个功能。低驱动标准逻辑单元可提供(但不限于)标准逻辑单元的输出驱动电流容量的四分之一或一半。

4.归因于功率电平的降低,低驱动标准逻辑单元的晶体管具有比在更高功率电平下的标准逻辑单元的对应晶体管更小的特征大小(例如,更小的晶体管宽度)。由于针对标准逻辑单元的标准(固定)高度,与具有更高输出驱动电流容量的对应标准逻辑单元相比,低驱动标准逻辑单元通常具有额外未使用空间。

5.换句话说,低驱动标准逻辑单元经特定设计以消耗较低功率。然而,由于具有由前端布局规则及节距确定的相同单元宽度,大多数低驱动标准逻辑单元具有与在更高功率电平下的标准逻辑单元相同或类似的面积。因此,通常低驱动标准逻辑单元仅具有功率增益,而没有面积增益。因此,低驱动标准逻辑单元经常经历对半导体裸片(也称为“裸片”)面积的低效利用。

6.因此,需要的是一种集成电路及形成所述集成电路的补充方法,所述集成电路包含用于执行逻辑功能的逻辑单元,所述逻辑单元在与其相关联的标准(固定)高度的约束内高效地利用裸片面积。

技术实现要素:

7.这些及其它问题通常通过包含集成电路及形成所述集成电路的方法的本公开的有利实例来解决或规避,并且通过所述有利实例来大体实现技术优势。在一个实例中,所述集成电路包含成行布置在半导体衬底上方的多个逻辑单元,其包含标准逻辑单元及至少一个组合逻辑单元。每一标准逻辑单元包含标准高度、是单位宽度的整数倍的宽度、沿一侧的第一电力轨、沿第二相对侧的第二电力轨,及至少一个晶体管及互连件,其经配置以实施逻辑功能,所述逻辑功能在操作时产生所述标准逻辑单元的单个逻辑输出。所述组合逻辑单元包含所述标准高度、所述单位宽度的整数倍的宽度、沿一侧的所述第一电力轨、沿第二相对侧的所述第二电力轨,及至少两个晶体管及互连件,其经配置以实施第一逻辑功能及第二逻辑功能。所述第一逻辑功能及所述第二逻辑功能分别产生第一逻辑输出及第二逻辑输出。所述互连件经配置以将所述第一逻辑输出及所述第二逻辑输出引导到所述组合逻辑单

元之外的相应目的地。

8.前述内容相当宽泛地概述本公开的特征及技术优势,以便可更好地理解下面对本公开的详细描述。下文将描述本公开的额外特征及优势,其形成本公开的权利要求书的标的物。应了解,所公开的具体实例可很容易地用作修改或设计用于实行本公开的相同目的的其它结构或过程的基础。还应认识到,此类等效构造不脱离所附权利要求书中阐述的本公开的精神及范围。

附图说明

9.为更完整地理解本公开,现参考以下结合附图的描述,其中:

10.图1说明集成电路的实例的平面图;

11.图2及3说明集成电路的实例的框图;

12.图4及5说明集成电路的实例的平面图;及

13.图6说明形成集成电路的方法的实例的流程图。

14.除非另有指示,否则不同图式中的对应数字及符号通常指代对应部分。图式经绘制以清楚地说明优选实例的相关方面,并且不一定按比例绘制。

具体实施方式

15.下面详细论述实例的制作及使用。然而,应了解,本公开提供可在各种各样的特定上下文中体现的适用概念。所论述的特定实例仅说明制作及使用本公开的特定方法,并且不限制本公开的范围。

16.本公开将关于特定上下文中的实例来描述,所述特定上下文即集成电路,以及操作及形成所述集成电路的方法。然而,本公开的原理也可应用于可能受益于组合逻辑单元的所有类型的电路,所述组合逻辑单元在针对标准逻辑单元的标准(固定)高度的约束内实施多个逻辑功能。如上文提及,低驱动标准逻辑单元经常经历对半导体裸片(也称为“裸片”)面积的低效利用。

17.本文描述的各种实例包含位于逻辑单元的相对侧的第一及第二电力轨。一个电力轨(例如,第一电力轨)可提供第一电压电势,例如vdd,而第二电力轨可提供第二电压电势,例如vss或接地。贯穿此描述及图式,第一电力轨展示在对应逻辑单元的顶部处,而第二电力轨则展示在对应逻辑单元的底部处。此约定仅为便于论述,并且相关领域的技术人员将了解,可反转电力轨的排序。此外,如本文使用,术语“栅极长度”是指栅极电极在流动通过晶体管沟道的电流方向上的范围,而“栅极宽度”是指栅极电极在垂直于栅极长度的方向上的范围。晶体管的开关速度部分由栅极长度确定,且晶体管的驱动电流能力部分由栅极宽度确定。

18.首先参考图1,说明为集成电路100的实例的平面图。集成电路100包含低驱动标准逻辑单元110及在更高功率电平下的标准逻辑单元150。低驱动标准逻辑单元110表示标准逻辑单元150的输出驱动电流容量的0.5x(或50%)。低驱动标准逻辑单元110包含沿一侧117的第一电力轨115及沿第二相对侧122的第二电力轨120。低驱动标准逻辑单元110包含第一晶体管源极-漏极区125及第二晶体管源极-漏极区域127。低驱动标准逻辑单元110包含向低驱动标准逻辑单元110提供逻辑输入的栅极区130(具有栅极宽度gw1)及逻辑输出

135。低驱动标准逻辑单元110包含指定为“h”的标准高度。

19.栅极区130被说明为横跨并包含第一晶体管源极-漏极区125上方的栅极及第二晶体管源极-漏极区127上方的栅极的单个结构。类似地,栅极宽度gw1也被说明为栅极区130的单个总体尺寸,其包含在第一晶体管源极-漏极区125上方的栅极的栅极宽度,及在第二晶体管源极-漏极区127上方的栅极的栅极宽度。

20.标准逻辑单元150包含沿一侧117的第一电力轨115及沿第二相对侧122的第二电力轨120。标准逻辑单元150包含第一晶体管源极-漏极区155及第二晶体管源极-漏极区157。标准逻辑单元150包含向标准逻辑单元150提供逻辑输入的栅极区160(具有栅极宽度gw2)及逻辑输出165。标准逻辑单元150包含指定为“h”的标准高度。

21.栅极区160被说明为横跨并包含第一晶体管源极-漏极区155上方的栅极及第二晶体管源极-漏极区157上方的栅极的单个结构。栅极宽度gw2也被说明为栅极区160的单个总体尺寸,其包含在第一晶体管源极-漏极区155上方的栅极的栅极宽度,及在第二晶体管源极-漏极区157上方的栅极的栅极宽度。

22.由于较小的晶体管特征大小及标准高度,低驱动标准逻辑单元110具有未使用的半导体裸片面积140。例如,低驱动标准逻辑单元110的第一晶体管源极-漏极区125及第二晶体管源极-漏极区127比标准逻辑单元150的第一晶体管源极-漏极区155及第二晶体管源极-漏极区157更小(面积更小)。

23.现在转到图2,说明为集成电路200的实例的框图。集成电路200包含多个逻辑单元,其包含成行布置在半导体衬底205上方的标准逻辑单元(例如,第一标准逻辑单元210及第二标准逻辑单元240)及至少一个组合逻辑单元(如,组合逻辑单元250)。第一标准逻辑单元210使用第一裸片面积212,并包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第一标准逻辑单元210的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。还应注意,裸片面积通常是相应单元的高度乘以宽度。第一标准逻辑单元210还包含沿一侧220的第一电力轨215及沿第二相对侧230的第二电力轨225。第一标准逻辑单元210还包含至少一个晶体管235及互连件,其经配置以实施逻辑功能(例如,双输入nand门),所述逻辑功能在操作时从到第一标准逻辑单元210的第一输入input 1及第二输入input 2产生第一标准逻辑单元210的单个逻辑输出output 1。

24.第二标准逻辑单元240使用第二裸片面积242,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第二标准逻辑单元240的宽度是单位宽度的两倍(或两个整数单位度,例如,约1.04微米)。第二标准逻辑单元240还包含沿一侧220的第一电力轨215及沿第二相对侧230的第二电力轨225。第二标准逻辑单元240还包含至少一个晶体管245及互连件,其经配置以实施逻辑功能(例如,反相器),所述逻辑功能在操作时从到第二标准逻辑单元240的输入(在此实例中,针对集成电路200的第三输入input 3)产生第二标准逻辑单元240的单个逻辑输出output 2。

25.组合逻辑单元250使用第三裸片面积252,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,组合逻辑单元250的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米),并且第三裸片面积252约为第一裸片面积212及第二裸片面积242的总和的60%或少于所述总和。组合逻辑单元250还包含沿一侧220的第一电力轨215及沿第二相对侧230的第二电力轨225。组合逻辑单元250还包含至少两个晶

体管(例如,第一(nand)晶体管255及第二(反相器)晶体管260)以及的互连件,其经配置以实施第一逻辑功能(例如,双输入nand门)及第二逻辑功能(例如,反相器)。在此实例中,第一逻辑功能是不同于第二逻辑功能的逻辑功能。第一逻辑功能从到组合逻辑单元250的第一输入(在此实例中,针对集成电路200的第四输入input 4)及到组合逻辑单元250的第二输入(在此例中,针对集成电路200第五输入input 5)产生组合逻辑单元250的第一逻辑输出output 3。第二逻辑功能从到组合逻辑单元250的第一输入(再次,针对集成电路200的第四输入input 4)产生组合逻辑单元250的第二逻辑输出output 4。因此,第一逻辑输出output 3及第二逻辑输出output 4是到组合逻辑单元250的相同逻辑输入(例如,针对集成电路200的第四输入input 4)的相应第一及第二函数。互连件经配置以将第一逻辑输出output 3及第二逻辑输出output 4引导到组合逻辑单元250外部的相应目的地。

26.第一(nand)晶体管255经配置以用第一输出驱动电流容量产生第一逻辑输出output 3,且第二(反相器)晶体管260经配置以用不同于第一输出驱动电流容量的第二输出驱动电流容量产生第二逻辑输出output 4。组合逻辑单元250的至少两个晶体管255、260(或其中的一者)的输出驱动电流容量可分别与多个标准逻辑单元中的第一标准逻辑单元210及第二标准逻辑单元240的至少一个晶体管235、245相同或比其更低。多个标准逻辑单元中的每一标准逻辑单元210、240的至少一个晶体管235、245分别具有第一及第二栅极宽度,并且经配置以实施对应第一及第二逻辑功能的组合逻辑单元250的至少两个晶体管255、260分别具有第三及第四栅极宽度。第三及第四栅极宽度中的至少一者不同于第一及第二栅极宽度中的至少一者。第一及第二栅极宽度可大体上相等,并且第三及第四栅极宽度中的至少一者不同于第一及第二栅极宽度。虽然栅极宽度通常可相同或不同,但组合逻辑单元250以及第一标准逻辑单元210及第二标准逻辑单元240的单元高度相同,同时容纳多个逻辑功能。

27.现在转到图3,说明为集成电路300的实例的框图。集成电路300包含多个逻辑单元,其包含成行布置在半导体衬底305上方的标准逻辑单元(例如,第一标准逻辑单元310及第二标准逻辑单元340)及至少一个组合逻辑单元(如,组合逻辑单元350)。第一标准逻辑单元310使用第一裸片面积312,并包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第一标准逻辑单元310的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。还应注意,裸片面积通常是相应单元的高度乘以宽度。第一标准逻辑单元310还包含沿一侧320的第一电力轨315及沿第二相对侧330的第二电力轨325。第一标准逻辑单元310还包含至少一个晶体管335及互连件,其经配置以实施逻辑功能(例如,双输入nand门),所述逻辑功能在操作时从到第一标准逻辑单元310的第一输入input 1及第二输入input 2产生第一标准逻辑单元310的单个逻辑输出output 1。

28.第二标准逻辑单元340使用第二裸片面积342,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第二标准逻辑单元340的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。第二标准逻辑单元340还包含沿一侧320的第一电力轨315及沿第二相对侧330的第二电力轨325。第二标准逻辑单元340还包含至少一个晶体管345及互连件,其经配置以实施逻辑功能(例如,双输入nor门),所述逻辑功能在操作时从到第二标准逻辑单元340的第一输入(在此实例中,针对集成电路300的第三输入input 3)及到第二标准逻辑单元340的第二输入(在此实例中,针对集成电路300的

第四输入input 4)产生第二标准逻辑单元340的单个逻辑输出output 2。

29.组合逻辑单元350使用第三裸片面积352,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,组合逻辑单元350的宽度是单位宽度的四倍(或四个整数单位宽,例如,约2.08微米),并且第三裸片面积352约为第一裸片面积312及第二裸片面积342的总和的70%或少于所述总和。组合逻辑单元350还包含沿一侧320的第一电力轨315及沿第二相对侧330的第二电力轨325。组合逻辑单元350还包含至少两个晶体管(例如,第一(nand)晶体管355及第二(nor)晶体管360)以及互连件,其经配置以实施第一逻辑功能(例如,双输入nand门)及第二逻辑功能(例如,双输入nor门)。在此实例中,第一逻辑功能是不同于第二逻辑功能的逻辑功能。第一逻辑功能从到组合逻辑单元350的第一输入(在此实例中,针对集成电路300的第五输入input 5)及到组合逻辑单元350的第二输入(在此例中,针对集成电路300第六输入input 6)产生组合逻辑单元350的第一逻辑输出output 3。第二逻辑功能从到组合逻辑单元350的第一输入(再次,针对集成电路300的第五输入input 5)及到组合逻辑单元350的第二输入(再次,针对集成电路300第六输入input 6)产生组合逻辑单元350的第二逻辑输出output 4。因此,第一逻辑输出output 3及第二逻辑输出output 4是到组合逻辑单元350的相同逻辑输入(例如,针对集成电路300的第五输入input 5及第六输入input 6)的相应第一及第二函数。应理解,第一及第二函数中的任一者可采用不同逻辑输入(例如,到组合逻辑单元350的第三输入,及在此实例中,针对集成电路300的第七输入input 7),而不是共享输入。互连件经配置以将第一逻辑输出output 3及第二逻辑输出output 4引导到组合逻辑单元350外部的相应目的地。

30.第一(nand)晶体管355经配置以用第一输出驱动电流容量产生第一逻辑输出output 3,且第二(nor)晶体管360经配置以用不同于第一输出驱动电流容量的第二输出驱动电流容量产生第二逻辑输出output 4。组合逻辑单元350的至少两个晶体管355、360的输出驱动电流容量可分别与多个标准逻辑单元中的第一标准逻辑单元310及第二标准逻辑单元340的至少一个晶体管335、345相同或比其更低。多个标准逻辑单元中的每一标准逻辑单元310、340的至少一个晶体管335、345分别具有第一及第二栅极宽度,并且经配置以实施对应第一及第二逻辑功能的组合逻辑单元350的至少两个晶体管355、360分别具有第三及第四栅极宽度。第三及第四栅极宽度中的至少一者不同于第一及第二栅极宽度中的至少一者。第一及第二栅极宽度可大体上相等,并且第三及第四栅极宽度中的至少一者不同于第一及第二栅极宽度。虽然栅极宽度通常可相同或不同,但组合逻辑单元350以及第一标准逻辑单元310及第二标准逻辑单元340的单元高度相同,同时容纳多个逻辑功能。

31.现在转到图4,说明为集成电路400的实例的平面图。集成电路400包含多个逻辑单元,其包含成行布置在半导体衬底405上方的标准逻辑单元(例如,第一标准逻辑单元410及第二标准逻辑单元440)及至少一个组合逻辑单元(如,组合逻辑单元450)。第一标准逻辑单元410使用第一裸片面积412,并包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第一标准逻辑单元410的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。还应注意,裸片面积通常是相应单元的高度乘以宽度。第一标准逻辑单元410还包含沿一侧420的第一电力轨415及沿第二相对侧430的第二电力轨425。第一标准逻辑单元410还包含至少一个晶体管(例如,通常指定为tr1的nand晶体管)及互连件,其经配置以实施逻辑功能(例如,双输入nand门),所述逻辑功能在操作时从到第一标准

逻辑单元410的第一输入input 1及第二输入input 2产生第一标准逻辑单元410的单个逻辑输出output 1。

32.nand晶体管tr1包含第一标准逻辑单元410的第一及第二晶体管。第一晶体管包含栅极区g1(具有栅极宽度gw1)、第一晶体管源极-漏极区sd1及经配置以实施逻辑功能的互连件(其中一些被指定为432)。第二晶体管包含栅极区g2(具有栅极宽度gw1)、第二晶体管源极-漏极区sd2及经配置以实施逻辑功能的互连件(其中一些被指定为432)。如所说明,第一标准逻辑单元410包含未使用的半导体裸片面积435,其表示半导体裸片面积的低效利用。

33.虽然栅极区g1被说明为横跨第一晶体管源极-漏极区sd1及第二晶体管源极-漏极区sd2的单个结构,但栅极区g1包含在第一晶体管源极-漏极区sd1上方的栅极。类似地,栅极宽度gw1也被说明为栅极区g1的单个总体尺寸,其包含在第一晶体管源极-漏极区sd1上方的栅极的栅极宽度。

34.虽然栅极区g2被说明为横跨第一晶体管源极-漏极区sd1及第二晶体管源极-漏极区sd2的单个结构,但栅极区g2包含在第二晶体管源极-漏极区sd2上方的栅极。类似地,栅极宽度gw1也被说明为栅极区g2的单个总体尺寸,其包含在第二晶体管源极-漏极区sd2上方的栅极的栅极宽度。

35.第二标准逻辑单元440使用第二裸片面积442,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第二标准逻辑单元440的宽度是单位宽度的两倍(或两个整数单位度,例如,约1.04微米)。第二标准逻辑单元440还包含沿一侧420的第一电力轨415及沿第二相对侧430的第二电力轨425。第二标准逻辑单元440还包含至少一个晶体管(例如,通常指定为tr2的反相器晶体管)及互连件,其经配置以实施逻辑功能(例如,反相器),所述逻辑功能在操作时从到第二标准逻辑单元440的输入(在此实例中,针对集成电路400的第三输入input 3)产生第二标准逻辑单元440的单个逻辑输出output 2。

36.反相器晶体管tr2包含第二标准逻辑单元440的第一及第二晶体管。第一晶体管(在此实例中,针对集成电路400的第三晶体管)包含栅极区g3(具有栅极宽度gw2)、第一晶体管源极-漏极区(在此实例中,针对集成电路400的第一晶体管源极-漏极区sd3)及经配置以实施逻辑功能的互连件(其中一些被指定为445)。第二晶体管(在此实例中,针对集成电路400的第四晶体管)包含栅极区g3(具有栅极宽度gw2)、第二晶体管源极-漏极区(在此实例中,针对集成电路400的第四晶体管源极-漏极区sd4)及经配置以实施逻辑功能的互连件(其中一些被指定为445)。如所说明,标准逻辑单元440包含未使用的半导体裸片面积447,其表示半导体裸片面积的低效利用。

37.栅极区g3被说明为横跨并包含在第三晶体管源极-漏极区sd3上方的栅极及在第四晶体管源极-漏极区sd4上方的栅极的单个结构。栅极宽度gw2也被说明为栅极区g3的单个总体尺寸,其包含在第三晶体管源极-漏极区sd3上方的栅极的栅极宽度,及在第四晶体管源极-漏极区sd4上方的栅极的栅极宽度。

38.组合逻辑单元450使用第三裸片面积452,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,组合逻辑单元450的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米),并且第三裸片面积452约为第一裸片面积412

及第二裸片面积442的总和的60%或小于所述总和。组合逻辑单元450还包含沿一侧420的第一电力轨415及沿第二相对侧430的第二电力轨425。组合逻辑单元450还包含至少两个晶体管(例如,一般指定为tr3的第一(nand)晶体管及一般指定为tr4的第二(反相器)晶体管)及互连件,其经配置以实施第一逻辑功能(例如,双输入nand门)及第二逻辑功能(例如,反相器)。在此实例中,第一逻辑功能是不同于第二逻辑功能的逻辑功能。第一逻辑功能从到组合逻辑单元450的第一输入(在此实例中,针对集成电路400的第四输入input 4)及到组合逻辑单元450的第二输入(在此例中,针对集成电路400第五输入input 5)产生组合逻辑单元450的第一逻辑输出output 3。第二逻辑功能从到组合逻辑单元450的第一输入(再次,针对集成电路400的第四输入input 4)产生组合逻辑单元450的第二逻辑输出output 4。因此,第一逻辑输出output 3及第二逻辑输出output 4是到组合逻辑单元450的相同逻辑输入(例如,针对集成电路400的第四输入input 4)的相应第一及第二函数。互连件经配置以将第一逻辑输出output 3及第二逻辑输出output 4引导到组合逻辑单元450外部的相应目的地。

39.第一(nand)晶体管tr3包含组合逻辑单元450的第一及第二晶体管。组合逻辑单元450的第一晶体管(在此实例中,针对集成电路400的第五晶体管)包含栅极区g4(具有栅极宽度gw3)、第一晶体管源极-漏极区(在此实例中,针对集成电路400的第五晶体管源极-漏极区sd5)及经配置以实施逻辑功能的互连件(其中一些指定为455)。第二晶体管(在此实例中,针对集成电路400的第六晶体管)包含栅极区g5(具有栅极宽度gw4)、第二晶体管源极-漏极区(在此实例中,针对集成电路400的第六晶体管源极-漏极区sd6)及经配置以实施逻辑功能的互连件(其中一些被指定为455)。

40.第二(反相器)晶体管tr4包含组合逻辑单元450的第三及第四晶体管。组合逻辑单元450的第三晶体管(在此实例中,针对集成电路400的第七晶体管)包含栅极区g4(具有栅极宽度gw3)、第三晶体管源极-漏极区(在此实例中,针对集成电路400的第七晶体管源极-漏极区sd7),及经配置以实施逻辑功能的互连件(其中一些指定为455)。第四晶体管(在此实例中,针对集成电路400的第八晶体管)包含栅极区g4(具有栅极宽度gw3)、第四晶体管源极-漏极区(在此实例中,针对集成电路400的第八晶体管源极-漏极区sd8),及经配置以实施逻辑功能的互连件(其中一些被指定为455)。

41.虽然栅极区g4被说明为横跨第五晶体管源极-漏极区sd5、第六晶体管源极-漏极区sd6、第七晶体管源极-漏极地区sd7及第八晶体管源极-漏极地方sd8的单个结构,但栅极区g4包含在第五晶体管源极-漏极地区sd5上方的栅极、在第七晶体管源极-漏极区sd7上方的栅极及在第八晶体管源极-漏极区sd8上方的栅极。类似地,栅极宽度gw3也被说明为栅极区g4的单个总体尺寸,其包含在第五晶体管源极-漏极区sd5上方的栅极的栅极宽度、针对在第七晶体管源极-漏极区sd7上方的栅极的栅极宽度及在第八晶体管源极-漏极层区sd8上方的栅极的栅极宽度。

42.虽然栅极区g5被说明为横跨第五晶体管源极-漏极区sd5及第六晶体管源极-漏极区sd6的单个结构,但栅极区g5包含在第六晶体管源极-漏极区sd6上方的栅极。类似地,栅极宽度gw4也被说明为栅极区g5的单个总体尺寸,其包含在第六晶体管源极-漏极区sd6上方的栅极的栅极宽度。

43.第一(nand)晶体管tr3(在此实例中,针对集成电路400的第五及第六晶体管)经配

置以用第一输出驱动电流容量产生第一逻辑输出output 3,并且第二(反相器)晶体管tr4(在此实例中,针对集成电路400的第七及第八晶体管)经配置以用不同于第一输出驱动电流容量的第二输出驱动电流容量产生第二逻辑输出output 4。组合逻辑单元450的晶体管(在此实例中,针对集成电路400的第五、第六、第七及第八晶体管,或其中的一者)的输出驱动电流容量可与多个标准逻辑单元中的第一标准逻辑单元410及第二标准逻辑单元440的晶体管(在此实例中,针对集成电路400的第一、第二、第三及第四晶体管)相同或比其更低。多个标准逻辑单元中的每一标准逻辑单元410、440的晶体管具有第一及第二栅极宽度(在此实例中,针对集成电路400的第一及第二晶体管的栅极宽度gw1,以及针对集成电路400的第三及第四晶体管的栅极宽度gw2)。经配置以实施对应第一及第二逻辑功能的组合逻辑单元450的晶体管具有第三及第四栅极宽度(在此情况下,针对集成电路400的第五、第七及第八晶体管的栅极宽度gw3,以及针对集成电路400的第六晶体管的栅极宽度gw4)。第三栅极宽度gw3及第四栅极宽度gw4中的至少一者不同于第一栅极宽度gw1及第二栅极宽度gw2中的至少一者。第一栅极宽度gw1及第二栅极宽度gw2可大体上相等,并且第三栅极宽度gw3及第四栅极宽度gw4中的至少一者不同于第一栅极宽度gw1及第二栅极宽度gw2。虽然栅极宽度通常可相同或不同,但组合逻辑单元450以及第一标准逻辑单元410及第二标准逻辑单元440的单元高度相同,同时容纳多个逻辑功能。

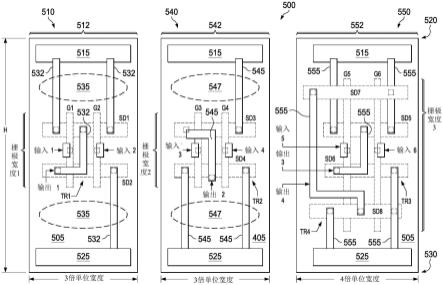

44.现在转到图5,说明为集成电路500的实例的平面图。集成电路500包含多个逻辑单元,其包含成行布置在半导体衬底505上方的标准逻辑单元(例如,第一标准逻辑单元510及第二标准逻辑单元540)及至少一个组合逻辑单元(如,组合逻辑单元550)。第一标准逻辑单元510使用第一裸片面积512,并包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第一标准逻辑单元510的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。还应注意,裸片面积通常是相应单元的高度乘以宽度。第一标准逻辑单元510还包含沿一侧520的第一电力轨515及沿第二相对侧530的第二电力轨525。第一标准逻辑单元510还包含至少一个晶体管(例如,通常指定为tr1的nand晶体管)及互连件,其经配置以实施逻辑功能(例如,双输入nand门),所述逻辑功能在操作时从到第一标准逻辑单元510的第一输入input 1及第二输入input 2产生第一标准逻辑单元510的单个逻辑输出output 1。

45.nand晶体管tr1包含第一标准逻辑单元510的第一及第二晶体管。第一晶体管包含栅极区g1(具有栅极宽度gw1)、第一晶体管源极-漏极区sd1及经配置以实施逻辑功能的互连件(其中一些被指定为532)。第二晶体管包含栅极区g2(具有栅极宽度gw1)、第二晶体管源极-漏极区sd2及经配置以实施逻辑功能的互连件(其中一些被指定为532)。如所说明,第一标准逻辑单元510包含未使用的半导体裸片面积535,其表示半导体裸片面积的低效利用。

46.虽然栅极区g1被说明为横跨第一晶体管源极-漏极区sd1及第二晶体管源极-漏极区sd2的单个结构,但栅极区g1包含在第一晶体管源极-漏极区sd1上方的栅极。类似地,栅极宽度gw1也被说明为栅极区g1的单个总体尺寸,其包含在第一晶体管源极-漏极区sd1上方的栅极的栅极宽度。

47.虽然栅极区g2被说明为横跨第一晶体管源极-漏极区sd1及第二晶体管源极-漏极区sd2的单个结构,但栅极区g2包含在第二晶体管源极-漏极区sd2上方的栅极。类似地,栅

极宽度gw1也被说明为栅极区g2的单个总体尺寸,其包含在第二晶体管源极-漏极区sd2上方的栅极的栅极宽度。

48.第二标准逻辑单元540使用第二裸片面积542,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,第二标准逻辑单元540的宽度是单位宽度的三倍(或三个整数单位宽,例如,约1.56微米)。第二标准逻辑单元540还包含沿一侧520的第一电力轨515及沿第二相对侧530的第二电力轨525。第二标准逻辑单元540还包含至少一个晶体管(例如,通常指定为tr2的nor晶体管)及互连件,其经配置以实施逻辑功能(例如,双输入nor门),所述逻辑功能在操作时从到第二标准逻辑单元540的第一输入(在此实例中,针对集成电路500的第三输入input 3)及到第二标准逻辑单元540的第二输入(在此实例中,针对集成电路500的第四输入input 4)产生第二标准逻辑单元540的单个逻辑输出output 2。

49.nor晶体管tr2包含第二标准逻辑单元540的第一及第二晶体管。第一晶体管(在此实例中,针对集成电路500的第三晶体管)包含栅极区g3(具有栅极宽度gw2)、第一晶体管源极-漏极区(在此实例中,针对集成电路500的第一晶体管源极-漏极区sd3)及经配置以实施逻辑功能的互连件(其中一些被指定为545)。第二晶体管(在此实例中,针对集成电路500的第四晶体管)包含栅极区g4(具有栅极宽度gw2)、第二晶体管源极-漏极区(在此实例中,针对集成电路500的第四晶体管源极-漏极区sd4)及经配置以实施逻辑功能的互连件(其中一些被指定为545)。如所说明,标准逻辑单元540包含未使用的半导体裸片面积547,其表示半导体裸片面积的低效利用。

50.虽然栅极区g3被说明为横跨第三晶体管源极-漏极区sd3及第四晶体管源极-漏极区sd4的单个结构,但栅极区g3包含在第三晶体管源极-漏极区sd3上方的栅极。类似地,栅极宽度gw2也被说明为栅极区g3的单个总体尺寸,其包含在第三晶体管源极-漏极区sd3上方的栅极的栅极宽度。

51.虽然栅极区g4被说明为横跨第三晶体管源极-漏极区sd3及第四晶体管源极-漏极区sd4的单个结构,但栅极区g4包含在第四晶体管源极-漏极区sd4上方的栅极。类似地,栅极宽度gw2也被说明为栅极区g4的单个总体尺寸,其包含在第四晶体管源极-漏极区sd4上方的栅极的栅极宽度。

52.组合逻辑单元550使用第三裸片面积552,并且包含标准高度(指定为“h”)及是单位宽度(指定为“uw”)的整数倍的宽度。在此实例中,组合逻辑单元550的宽度是单位宽度的四倍(或四个整数单位宽,例如,约2.08微米),并且第三裸片面积552约为第一裸片面积512及第二裸片面积542的总和的70%或小于所述总和。组合逻辑单元550还包含沿一侧520的第一电力轨515及沿第二相对侧530的第二电力轨525。组合逻辑单元550还包含至少两个晶体管(例如,一般指定为tr3的第一(nand)晶体管及一般指定为tr4的第二(nor)晶体管)及互连件,其经配置以实施第一逻辑功能(例如,双输入nand门)及第二逻辑功能(例如,双输入nor门)。在此实例中,第一逻辑功能是不同于第二逻辑功能的逻辑功能。第一逻辑功能从到组合逻辑单元550的第一输入(在此实例中,针对集成电路500的第五输入input 5)及到组合逻辑单元550的第二输入(在此例中,针对集成电路500第六输入input 5)产生组合逻辑单元550的第一逻辑输出output 3。第二逻辑功能从到组合逻辑单元550的第一输入(再次,针对集成电路500的第五输入input 5)及到组合逻辑单元550的第二输入(再次,针对集

成电路500第六输入input 6)产生组合逻辑单元550的第二逻辑输出output 4。因此,第一逻辑输出output 3及第二逻辑输出output 4是到组合逻辑单元550的相同逻辑输入(例如,针对集成电路500的第五输入input 5及第六输入input 6)的相应第一及第二函数。互连件经配置以将第一逻辑输出output 3及第二逻辑输出output 4引导到组合逻辑单元550外部的相应目的地。

53.第一(nand)晶体管tr3包含组合逻辑单元550的第一及第二晶体管。组合逻辑单元550的第一晶体管(在此实例中,针对集成电路500的第五晶体管)包含栅极区g5(具有栅极宽度gw3)、第一晶体管源极-漏极区(在此实例中,针对集成电路500的第五晶体管源极-漏极区sd5),及经配置以实施逻辑功能的互连件(其中一些指定为555)。第二晶体管(在此实例中,针对集成电路500的第六晶体管)包含栅极区g6(具有栅极宽度gw3)、第二晶体管源极-漏极区(在此实例中,针对集成电路500的第六晶体管源极-漏极区sd6)及经配置以实施逻辑功能的互连件(其中一些被指定为555)。

54.第二(nor)晶体管tr4包含组合逻辑单元550的第三及第四晶体管。组合逻辑单元550的第三晶体管(在此实例中,针对集成电路500的第七晶体管)包含栅极区g5(具有栅极宽度gw3)、第三晶体管源极-漏极区(在此实例中,针对集成电路500的第七晶体管源极-漏极区sd7),及经配置以实施逻辑功能的互连件(其中一些指定为555)。第四晶体管(在此实例中,针对集成电路500的第八晶体管)包含栅极区g6(具有栅极宽度gw3)、第四晶体管源极-漏极区(在此实例中,针对集成电路500的第八晶体管源极-漏极区sd8),及经配置以实施逻辑功能的互连件(其中一些被指定为555)。

55.虽然栅极区g5被说明为横跨第五晶体管源极-漏极区sd5、第六晶体管源极-漏极区sd6、第七晶体管源极-漏极地区sd7及第八晶体管源极-漏极地方sd8的单个结构,但栅极区g5包含在第五晶体管源极-漏极地区sd5上方的栅极及在第七晶体管源极-漏极区sd7上方的栅极。类似地,栅极宽度gw3也被说明为栅极区g5的单个总体尺寸,其包含在第五晶体管源极-漏极区sd5上方的栅极的栅极宽度及在第七晶体管源极-漏极区sd7上方的栅极的栅极宽度。

56.虽然栅极区g6被说明为横跨第五晶体管源极-漏极区sd5、第六晶体管源极-漏极区sd6、第七晶体管源极-漏极地区sd7及第八晶体管源极-漏极地方sd8的单个结构,但栅极区g6包含在第六晶体管源极-漏极地区sd6上方的栅极及在第八晶体管源极-漏极区sd8上方的栅极。类似地,栅极宽度gw3也被说明为栅极区g6的单个总体尺寸,其包含在第六晶体管源极-漏极区sd6上方的栅极的栅极宽度及在第八晶体管源极-漏极区sd8上方的栅极的栅极宽度。

57.第一(nand)晶体管tr3(在此实例中,针对集成电路500的第五及第六晶体管)经配置用第一输出驱动电流容量产生第一逻辑输出output 3,并且第二(nor)晶体管tr4(在此实例中,针对集成电路500的第七及第八晶体管)经配置以用不同于第一输出驱动电流容量的第二输出驱动电流容量产生第二逻辑输出output 4。组合逻辑单元550的晶体管(在此实例中,针对集成电路500的第五、第六、第七及第八晶体管,或其中的一者)的输出驱动电流容量可与多个标准逻辑单元中的第一标准逻辑单元510及第二标准逻辑单元540的晶体管(在此实例中,针对集成电路500的第一、第二、第三及第四晶体管)相同或比其更低。

58.多个标准逻辑单元中的每一标准逻辑单元510、540的晶体管具有第一及第二栅极

宽度(在此实例中,针对集成电路500的第一及第二晶体管的栅极宽度gw1,以及针对集成电路500的第三及第四晶体管的栅极宽度gw2)。经配置以实施对应第一及第二逻辑功能的组合逻辑单元550的晶体管具有第三栅极宽度gw3。第三栅极宽度gw3不同于第一栅极宽度gw1及第二栅极宽度gw2中的至少一者。第一栅极宽度gw1及第二栅极宽度gw2可大体上相等,并且第三栅极宽度gw3不同于第一栅极宽度gw1及第二栅极宽度gw2。虽然栅极宽度通常可相同或不同,但组合逻辑单元550以及第一标准逻辑单元510及第二标准逻辑单元540的单元高度相同,同时容纳多个逻辑功能。

59.现在转到图6,说明的是形成集成电路的方法600的实例的流程图。出于实例支持的目的,此处介绍的特征将返回参考上文关于先前图式描述的类似特征(通过参考数字)。另外,虽然下面的方法600描述在单独步骤中形成多个逻辑单元,但应理解,多个逻辑单元可同时形成。形成集成电路(参见例如图2,200;图3,300;图4,400;图5,500)的方法600在开始步骤605处开始。在步骤610处,方法600在半导体衬底(参见例如图2,205;图3,305;图4,405;图5,505)上方成行形成第一标准逻辑单元(参见例如图2,210;图3,310;图4,410;图5,510)。为形成第一标准逻辑单元,方法600在步骤615处沿一侧(参见例如图2,220;图3,320;图4,420;图5,520)形成第一电力轨(参见例如图2,215;图3,315;图4,415;图5,515)。为形成第一标准逻辑单元,方法600在步骤620处沿第二相对侧(参见例如图2,230;图3,330;图4,430;图5,530)形成第二电力轨(参见例如图2,225;图3,325;图4,425;图5,525)。为形成第一标准逻辑单元,方法600在步骤625处形成经配置以实施逻辑功能的至少一个晶体管(参见例如图2,235;图3,335;图4及5,tr1)及互连件(参见例如图4,432;图5,532),所述逻辑功能在操作时产生第一标准逻辑单元(参见例如图2,210;图3,310;图4,410;图5,510)的单个逻辑输出(参见例如图2到5,output 1)。第一标准逻辑单元(参见例如图2,210;图3,310;图4,410;图5,510)具有标准高度(参见例如图2到5,h)及是单位宽度(参见例如图2到5,uw)的整数倍的宽度。

60.在步骤630处,方法600在半导体衬底(参见例如图2,205;图3,305;图4,405;图5,505)上方成行形成第二标准逻辑单元(参见例如图2,240;图3,340;图4,440;图5,540)。为形成第二标准逻辑单元,方法600在步骤635处沿一侧(参见例如图2,220;图3,320;图4,420;图5,520)形成第一电力轨(参见例如图2,215;图3,315;图4,415;图5,515)。为形成第二标准逻辑单元,方法600在步骤640处沿第二相对侧(参见例如图2,230;图3,330;图4,430;图5,530)形成第二电力轨(参见例如图2,225;图3,325;图4,425;图5,525)。为形成第二标准逻辑单元,方法600在步骤645处形成经配置以实施逻辑功能的至少一个晶体管(参见例如图2,245;图3,345;图4及5,tr2)及互连件(参见例如图4,445;图5,545),所述逻辑功能在操作时产生第二标准逻辑单元(参见例如图2,240;图3、340;图4,440;图5,540)的单个逻辑输出(参见例如图2到5,output 2)。第二标准逻辑单元(参见例如图2,240;图3、340;图4,440;图5,540)具有标准高度(参见例如图2到5,h)及是单位宽度(参见例如图2到5,uw)的整数倍的宽度。

61.在步骤650处,方法600在半导体衬底(参见例如图2,205;图3,305;图4,405;图5,505)上方成行形成组合逻辑单元(参见例如图2,250;图3、350;图4,450;图5,550)。为形成组合逻辑单元,方法600在步骤655处沿一侧(参见例如图2,220;图3、320;图4,420;图5,520)形成第一电力轨(参见例如图2,215;图3,315;图4,415;图5,515)。为形成组合逻辑单

元,方法600在步骤660处沿第二相对侧(参见例如图2,230;图3,330;图4,430;图5,530)形成第二电力轨(参见例如图2,225;图3、325;图4,425;图5,525)。

62.为形成组合逻辑单元,方法600在步骤665处形成至少两个晶体管(例如,图2,255、260;图3,355、360;图4及5,tr3、tr4)及互连件(参见例如图4,455;图5,555),其经配置以实施第一逻辑功能及第二逻辑功能。第一逻辑功能可为不同于第二逻辑功能的逻辑功能。第一逻辑功能及第二逻辑功能分别产生第一逻辑输出(参见例如图2到5,output 3)及第二逻辑输出(参见例如图2到5,output 4)。互连件(参见例如图4,455;图5,555)经配置以将第一逻辑输出(参见例如图2到5,output 3)及第二逻辑输出(参见例如图2到5,output 4)引导到组合逻辑单元(参加例如图2,250;图3,350;图4,450;图5,550)之外的相应目的地。组合逻辑单元(参见例如图2,250;图3,350;图4,450;图5,550)具有标准高度(参见例如图2到5,h)及是单位宽度(参见例如图2到5,uw)的整数倍的宽度。形成至少两个晶体管的步骤665可包含形成第一及第二晶体管(参见例如图2,255、260;图3,355、360;图4及5,tr3、tr4)。第一晶体管(参见例如图2,255;图3,355;图4及5,tr3)经配置以用第一输出驱动电流容量产生第一逻辑输出(参见例如图2到5,输出output 3),且第二晶体管(参见例如图2,260;图3,360;图4及5,tr4)经配置以用不同于第一输出驱动电流容量的第二输出驱动电流容量产生第二逻辑输出(参见例如图式,output 4)。

63.下文论述介绍形成相应标准逻辑单元及组合逻辑单元的各种变化。第一逻辑输出(参见例如图2到5,output 3)及第二逻辑输出(参见例如图2到5,output 4)可为到组合逻辑单元(参见例如图2,250;图3,350;图4,450;图5,550)的相同逻辑输入(参见例如图2,input 4;图3,input 5、input 6;图4,input 4;图5,input 5、input6)的相应第一及第二函数。第一标准逻辑单元(参见例如图2,210;图4,410)及第二标准逻辑单元(参见例如图2,240;图4,440)具有两个或三个整数单位宽的宽度,且组合逻辑单元(参见例如图2,250;图4,450)具有三个整数单位宽的宽度。第一标准逻辑单元(参见例如图3,310;图5,510)及第二标准逻辑单元(参见例如图3,340;图5,540)具有三个整数单位宽的宽度,且组合逻辑单元(参见例如图3,350;图5,550)具有四个整数单位宽的宽度。

64.第一逻辑功能可为经配置以接收第一逻辑输入(参见例如图2及4,input 4)及第二不同逻辑输入(参见例如图2及4,input 5)的双输入门,且第二逻辑功能可为经配置以接收第一逻辑输入(参见例如图2及4,input 4)的反相器。第一标准逻辑单元(参见例如图2,210;图4,410)经配置以实施第一双输入门,并且具有三个整数单位宽的宽度,第二标准逻辑单元(参见例如图2,240;图4,440)经配置以实施第一反相器,并且具有两个整数单位宽的宽度,且组合逻辑单元(参见例如图2,250;图4,450)经配置以实施第二双输入门及第二反相器,并且具有三个整数单位宽的宽度。第一标准逻辑单元(参见例如图2,210;图4,410)使用第一裸片面积(参见例如图2,212;图4,412),并且经配置以实施第一nand门,第二标准逻辑单元(参见例如图2,240;图4,440)使用第二裸片面积(参见例如图2,242;图4,442)并且经配置以实施第一反相器,组合逻辑单元(参见例如图2,250;图4,450)使用第三裸片面积(参见例如图2,252;图4,452)并且经配置以实施第二nand门及第二反相器。第三裸片面积(参见例如图2,252;图4,452)是第一及第二裸片面积的总和的60%或小于所述总和(参见例如图2,212、242;图4,412、442)。

65.第一逻辑功能是经配置以接收第一逻辑输入(参见例如图3及5,input 5)及不同

第二逻辑输入(参见例如图3及5,input 6)的第一双输入门,且第二逻辑功能是经配置以接收第一逻辑输入(参见例如图3及5,input 5)及第二逻辑输入(参见例如图3及5,input 6)的第二双输入门。第一逻辑功能是经配置以接收第一逻辑输入(参见例如图3,input 5)及不同第二逻辑输入(参见例如图3,input 6)的第一双输入门,且第二逻辑功能是第二双输入门,其经配置以接收第一逻辑输入(参见例如图3,input 5)及与第一逻辑输入(参见例如图3,input 5)及第二逻辑输入(参见例如图3,input 6)不同的第三逻辑输入(参见例如,图3,input 7)。

66.第一标准逻辑单元(参见例如图3,310;图5,510)经配置以实施第一nand门,并且具有三个整数单位宽的宽度,第二标准逻辑单元(参见例如图3,340;图5,540)经配置以实施第一nor门,并且具有三个整数单位宽的宽度,且组合逻辑单元(参见例如图3,350;图5,550)经配置以实施第二nand门及第二nor门,并且具有四个整数单位宽的宽度。第一标准逻辑单元(参见例如图3,310;图5,510)使用第一裸片面积(参见例如图3,312;图5,512),并且经配置以实施第一nand门,第二标准逻辑单元(参见例如图3,340;图5,540)使用第二裸片面积(参见例如图3,342;图5,542)并且经配置以实施第一nor门,且组合逻辑单元(参见例如图3,350;图5,550)使用第三裸片面积(参见例如图3,352;图5,552)并且经配置以实施第二nand门及第二nor门。第三裸片面积(参见例如图3,352;图5,552)是第一及第二裸片面积(参见例如图3,312、342;图5,512、542)的总和的70%或小于所述总和。

67.第一标准逻辑单元(参见例如图4,410;图5,510)的至少一个晶体管(参见例如图4及5,tr1)具有第一栅极宽度(参见例如图4及5,gw1),第二标准逻辑单元(参见例如图4,440;图5,540)的至少一个晶体管(参见例如图4及5,tr2)具有第二栅极宽度(参见例如图4及5、gw2),经配置以实施对应第一及第二逻辑功能的组合逻辑单元(参见例如图4,450;图5,550)的至少两个晶体管(参见例如图4及5,tr3、tr4)具有至少第三栅极宽度(参见例如图4,gw3、gw4;图5,gw3),并且至少第三栅极宽度(参见例如图4,gw3、gw4;图5,gw3)不同于第一及第二栅极宽度(参见例如图4及5,gw1、gw2)中的至少一者。第一及第二栅极宽度(参见例如图4及5,gw1,gw2)大体上相等,并且至少第三栅极宽度(参见例如图4及5,gw3、gw4;图5,gw 3)不同于第一及第二栅极宽度(参见例如图4及5,gw1、gw2)。

68.在表1中总结组合nand门及反相器组合逻辑单元。

[0069][0070]

表1

[0071]

表2总结组合nand门及nor门组合逻辑单元。

[0072][0073][0074]

表2

[0075]

因此,已介绍一种具有标准逻辑单元及组合逻辑单元的集成电路,以及操作及形成所述集成电路的相关方法。应理解,先前描述的集成电路的实例及相关方法仅用于说明性目的来提交,并且能够利用未使用的半导体裸片面积将多个逻辑功能合并入组合逻辑单元中的其它实例完全在本公开的广泛范围内。

[0076]

虽然已经详细描述本公开,但可在不脱离本公开最广泛形式的精神及范围的情况下进行各种改变、替换及变更。

[0077]

此外,本技术案的范围不希望限于说明书中描述的过程、机器、制造、物质组成、手段、方法及步骤的特定实例。根据本公开,可利用目前存在或稍后将要开发的执行与本文描述的对应实例大体上相同的功能或实现与本文描述的对应实例大体上相同的结果的过程、机器、制造、物质组成、手段、方法或步骤。因此,所附权利要求书希望在其范围内包含此类过程、机器、制造、物质组成、手段、方法或步骤。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1