引线框架、半导体装置、检查方法及引线框架的制造方法与流程

1.本发明涉及引线框架、半导体装置、检查方法及引线框架的制造方法。

背景技术:

2.近年来,已知有一种半导体装置,其将例如ic(integrated circuit,集成电路)芯片等半导体芯片搭载于金属制的引线框架。即,例如将半导体芯片搭载在设于引线框架中央的面状芯片垫上,该半导体芯片例如通过引线键合(wire bonding)与设于芯片垫周围的多个引脚连接。并且,有时对搭载于引线框架的半导体芯片使用例如环氧树脂等树脂进行封装,从而形成半导体装置。

3.搭载于芯片垫上的半导体芯片有时例如通过胶带粘接在芯片垫上。即,在面状的芯片垫上粘贴有具有粘性的胶带,并由胶带粘接半导体芯片,从而将半导体芯片搭载于芯片垫。通过使用例如绝缘性的胶带来将半导体芯片搭载于芯片垫上,能够使半导体芯片与芯片垫电气绝缘。

4.专利文献1:日本特开平8-222585号公报

5.专利文献2:日本特开昭63-249341号公报

6.专利文献3:日本特开平1-147836号公报

技术实现要素:

7.在使用胶带来将半导体芯片搭载于芯片垫的情况下,半导体芯片的位置取决于胶带所粘贴的位置。因此,将胶带粘贴在芯片垫的适当的位置上非常重要,优选为在制造引线框架后,对胶带是否粘贴在芯片垫的适当的位置上进行检查。

8.作为检查胶带位置的方法,存在使用透射光的方法以及使用反射光的方法。即,对粘贴有胶带的引线框架照射光,并在由透射光或反射光生成的图像中检测胶带的位置,由此,能够判断胶带的位置是否适当。

9.然而,对于粘贴在芯片垫上的胶带,存在难以使用透射光或反射光来检测位置是否适当的问题。具体而言,由于芯片垫是光无法穿过的面状的部分,因此在使用透射光来进行检查时,无法检测到粘贴于芯片垫上的胶带。因此,使用透射光的方法难以用于检查粘贴于芯片垫上的胶带的位置是否适当。

10.另外,在使用反射光进行的检查中,与周围的金属部分相比,在胶带位置上的光的反射被抑制,因此能够检测到胶带的位置。然而,由于芯片垫表面的细微的损伤或色调的不均匀等也会使光的反射被抑制,因此根据芯片垫表面的状态而有时无法辨别金属部分与胶带,从而难以准确地检测出胶带的位置。其结果,存在无法确认到胶带所粘贴的位置是否适当,使得搭载于芯片垫上的半导体芯片的位置精准度下降的情况。

11.所公开的技术是鉴于上述问题而提出的,其目的在于提供一种能够防止半导体芯片的位置精准度下降的引线框架、半导体装置、检查方法及引线框架的制造方法。

12.本发明公开的引线框架在一个形态中包括:具有半导体芯片的搭载面的芯片垫、

以及设于所述芯片垫的搭载面的薄膜状部件,所述芯片垫具有贯穿孔,所述贯穿孔形成于包含所述薄膜状部件的外周的区域。

13.根据本发明公开的引线框架、半导体装置、检查方法及引线框架的制造方法的一个形态,能够取得防止半导体芯片的位置精准度下降的效果。

附图说明

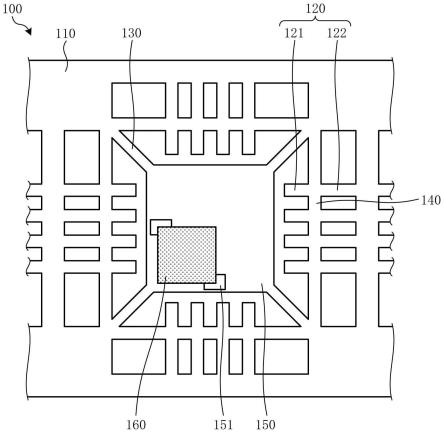

14.图1是表示一实施方式涉及的引线框架的结构的俯视图。

15.图2是用于说明贯穿孔的位置的图。

16.图3(a)至图3(d)是表示贯穿孔的位置的具体示例的图。

17.图4(a)至图4(d)是表示胶带的结构的具体示例的图。

18.图5是表示引线框架的制造方法的流程图。

19.图6是表示引线框架成形工序的具体示例的图。

20.图7是表示电镀加工工序的具体示例的图。

21.图8是表示胶带粘贴工序的具体示例的图。

22.图9是表示引线框架的检查方法的流程图。

23.图10(a)、图10(b)是表示二值图像的具体示例的图。

24.图11是表示半导体装置的制造方法的流程图。

25.图12是表示半导体芯片搭载工序的具体示例的图。

26.图13(a)至图13(c)是用于说明粘接半导体芯片的图。

27.图14是表示引线键合工序的具体示例的图。

28.图15是表示树脂封装工序的具体示例的图。

29.图16是表示分割工序的具体示例的图。

30.符号说明

31.110 框体

32.120 引脚

33.121 内引脚

34.122 外引脚

35.125 镀层

36.130 支承杆

37.140 连筋

38.150 芯片垫

39.151 贯穿孔

40.160 胶带

41.210、215 半导体芯片

42.230 模塑树脂

具体实施方式

43.下面,参照附图对本发明公开的引线框架、半导体装置、检查方法及引线框架的制造方法的一实施方式进行详细说明。此外,本发明不限于该实施方式。

44.图1是表示一实施方式涉及的引线框架100的结构的俯视图。由于引线框架100是作为由多个引线框架100连结而成的集合体来制造的,在图1中,对集合体中的一个引线框架100进行图示。

45.引线框架100具有:框体110、引脚120、支承杆130、连筋(dam bar)140及芯片垫150。引线框架100例如由厚度为0.1~0.25mm左右的铜或铜合金等金属板形成。

46.框体110对一个引线框架100的外周进行划定,并对引脚120、支承杆130及芯片垫150进行支承。在制造引线框架100时,引线框架100作为通过框体110连结多个引线框架100的集合体被制造。并且,在引线框架100搭载了半导体芯片并被树脂封装后,将引脚120间的连筋140切断,并将包括引脚120、支承杆130及芯片垫150的部分从框体110切开,则能够得到被分割成单片的半导体装置。

47.在引线框架100搭载有半导体芯片的情况下,引脚120形成将该半导体芯片与外部部件电气连接的端子。即,在引线框架100搭载有半导体芯片的情况下,半导体芯片例如通过引线键合与引脚120连接。在引线框架100中,形成有包围芯片垫150的多个引脚120,相邻的引脚120通过连筋140连接。

48.此外,引脚120包括内引脚121和外引脚122。内引脚121形成于比连筋140靠近芯片垫150处,与搭载于芯片垫150的半导体芯片电气连接。外引脚122形成于比连筋140远离芯片垫150处,成为与外部部件电气连接的端子。在搭载于芯片垫150的半导体芯片被树脂封装时,内引脚121与半导体芯片一起被树脂封装,而外引脚122从树脂中露出。

49.支承杆130将框体110与芯片垫150连接,用于支承芯片垫150。在搭载于芯片垫150的半导体芯片被树脂封装时,支承杆130与半导体芯片一起被树脂封装。并且,在经过树脂封装后,支承杆130被从框体110切开。

50.连筋140连接平行排列的多个引脚120,并将这些多个引脚120连接于框体110。通过在搭载于芯片垫150的半导体芯片被树脂封装后切断连筋140,使得连筋140连接的引脚120被各自分离。

51.芯片垫150是形成于引线框架100中央的面状的区域,例如通过四个支承杆130与框体110连结。芯片垫150具有例如一个边为2~20mm左右的正方形或长方形的面,半导体芯片被搭载于该面上。具体而言,在芯片垫150上粘贴有胶带160,半导体芯片粘接于胶带160的位置。并且,在包含胶带160的外周一部分的区域中,形成有将芯片垫150贯穿的贯穿孔151,所述胶带160被粘贴于芯片垫150的适当的位置。即,若胶带160被粘贴于芯片垫150的适当的位置上,则该胶带160的外周一部分位于贯穿孔151内。在图1所示的示例中,胶带160的对角的顶点均位于贯穿孔151内。

52.在此,参照图2对贯穿孔151的位置进行说明。图2示意性地表示芯片垫150的形状,图2的下图是放大表示贯穿孔151的周围的图。

53.如图2所示,芯片垫150例如在两处形成有贯穿孔151。各贯穿孔151形成为包含,在胶带160被粘贴在适当的位置的情况下顶点160a可能存在的范围,该顶点160a作为表示胶带160的位置的基准点。即,贯穿孔151形成为作为基准点的顶点160a可能存在的预设范围以上的大小。

54.具体而言,如图2的下图所示,贯穿孔151的前端位于:在胶带160被粘贴于适当的位置的范围内的最前方的情况下的顶点160a的位置的前方,贯穿孔151的后端位于:在胶带

160被粘贴于适当的位置的范围内的最后方的情况下的顶点160a的位置的后方。同样地,贯穿孔151的左端位于:在胶带160被粘贴于适当的位置的范围内的最左方的情况下的顶点160a的位置的左方,贯穿孔151的右端位于:在胶带160被粘贴于适当的位置的范围内的最右方的情况下的顶点160a的位置的右方。如此,贯穿孔151形成为与胶带160的粘贴位置可容许的误差范围对应的大小,例如具有一个边为0.4~2mm左右的正方形形状或长方形形状。

55.如此,贯穿孔151在胶带160被粘贴于适当的位置时的胶带160的基准点可能存在的区域,贯穿芯片垫150。由此,当胶带160被粘贴于适当的位置时,作为胶带160的基准点的顶点160a位于贯穿孔151内。因此,在对芯片垫150照射光时,能够由穿过贯穿孔151的透射光生成能够检测出胶带160的基准点的坐标的图像,从而能够检查胶带160是否被粘贴在适当的位置上。

56.此外,图1、图2表示了将胶带160的对角的顶点作为基准点的情况下的贯穿孔151的位置,但贯穿孔151的位置不限于此。具体而言,例如如图3(a)所示,在将胶带160的对角的顶点作为基准点的情况下,贯穿孔151也可以与芯片垫150的外周相接。即,在图3(a)所示的示例中,贯穿孔151形成为切开芯片垫150的外周的形状。

57.此外,在胶带160被粘贴于整个芯片垫150的情况下,例如如图3(b)所示,可以将胶带160的外周四个边作为基准线,在芯片垫150的外周四个边上形成贯穿孔151。即,在图3(b)所示的示例中,贯穿孔151形成为切开芯片垫150的外周四个边的形状,当胶带160被粘贴于适当的位置时,胶带160的四个边位于贯穿孔151内。

58.此外,例如如图3(c)所示,也可以将胶带160的外周四个边作为基准线,而在芯片垫150上形成四处贯穿孔151。这种情况下,当胶带160被粘贴于适当的位置时,胶带160的四个边也位于贯穿孔151内。

59.进一步地,例如如图3(d)所示,也可以将胶带160的一个顶点作为基准点,而在芯片垫150上形成一处贯穿孔151。这种情况下,当胶带160被粘贴于适当的位置时,作为胶带160的基准点的顶点位于贯穿孔151内。

60.此外,形成贯穿孔151的位置是根据在芯片垫150上粘贴的胶带160的位置来决定的,为了将半导体芯片通过胶带160可靠地接合于芯片垫150上,优选使贯穿孔151形成于俯视视角下与半导体芯片不重叠的位置。通过配合贯穿孔151的形成位置对胶带160的大小进行调整,则可以以覆盖半导体芯片的搭载范围且基准点位于贯穿孔151内的方式粘贴胶带160。此外,贯穿孔151形成为,具有大于等于胶带160的基准点(线)可能存在的预设范围的大小的各种形状即可。因此,例如除正方形及长方形等矩形以外,贯穿孔151的形状也可以是各种多边形、圆形或椭圆形等。

61.胶带160是能够被粘贴在芯片垫150的表面的薄膜状部件。胶带160具有在俯视视角下,例如一个边为1~20mm左右的正方形形状或长方形形状,并且胶带160被粘贴在芯片垫150的搭载半导体芯片的位置。若胶带160被粘贴于预定搭载半导体芯片的适当的位置,则胶带160的预设的顶点或边等基准点或基准线位于贯穿孔151内。胶带160的结构的具体示例如图4(a)~图4(d)所示。图4(b)~图4(d)表示图4(a)的i-i线截面。

62.如图4(b)所示,胶带160例如可以由一层粘接层161形成。即,胶带160可以是由粘接材料构成的粘接层161被粘贴在芯片垫150上的胶带。粘接层161例如可以使用环氧树脂

等绝缘树脂来形成。粘接层161的厚度例如可以为10~100μm左右。由于这种胶带160是由一层粘接层161形成的,因此胶带160的两个面具有粘性,其一个面可以被粘贴在芯片垫150上,同时另一个面可以与半导体芯片粘接。

63.此外,如图4(c)所示,胶带160例如可以为在基材层162的一个面上层叠粘接层161的双层结构。即,胶带160可以是将层叠在基材层162上的粘接层161粘贴在芯片垫150上的胶带。基材层162例如可以使用聚酰亚胺树脂等绝缘树脂来形成。粘接层161的厚度例如可以为10~50μm左右,基材层162的厚度例如可以为50~100μm左右。因此,胶带160的厚度例如为60~150μm左右。在这种胶带160中,由于基材层162的一个面上层叠有粘接层161,因此胶带160的粘接层161侧的面被粘贴在芯片垫150上。在该胶带160上搭载半导体芯片时,通过在基材层162的表面形成粘接层来粘接半导体芯片。

64.此外,如图4(d)所示,胶带160例如还可以为在基材层162的两个面上层叠粘接层161、163的三层结构。即,胶带160还可以是层叠于基材层162的粘接层161被粘贴于芯片垫150、并且粘接层163露出于表面的胶带。粘接层163与粘接层161一样地,例如可以使用环氧树脂等绝缘树脂来形成。粘接层161、163的厚度例如均可以为10~50μm左右,基材层162的厚度例如可以为50~100μm左右。因此,胶带160的厚度例如为70~200μm左右。在这种胶带160中,由于在胶带160的两个面形成有粘接层161、163,使得粘接层161能够被粘贴于芯片垫150,且粘接层163能够与半导体芯片粘接。

65.像这样,由于可以在芯片垫150上粘贴各种结构的胶带160,通过适当地选择具有所需厚度的胶带160,则能够调整芯片垫150与粘接在胶带160上的半导体芯片之间的距离。

66.接下来,参照图5所示的流程图来对如上所述构成的引线框架100的制造方法进行说明。

67.首先,通过对例如厚度为0.1~0.25mm左右的铜或铜合金等金属板进行冲压加工或蚀刻等处理,来成形引线框架100(步骤s101)。此外,在成形引线框架100的同时,在芯片垫150上形成贯穿孔151(步骤s102)。具体而言,例如如图6所示,通过冲压加工或蚀刻处理将金属板的不要的部分去除,由此,在被框体110包围的区域内,形成引脚120、支承杆130、连筋140及芯片垫150。并且,在芯片垫150中形成贯穿孔151。

68.然后,对构成引脚120的内引脚121施加电镀加工(步骤s103)。即,例如如图7所示,在内引脚121的连接金属丝的位置形成镀层125。镀层125例如通过镀银形成。此外,在图7、图8以外的附图中,省略镀层125的图示。

69.在形成镀层125后,将胶带160粘贴在芯片垫150上(步骤s104)。具体而言,胶带160通过将胶带160的粘接层161粘接于芯片垫150的搭载半导体芯片的位置来完成粘贴。此时,如图8所示,只要胶带160被粘贴在适当的位置,则胶带160的预设的顶点或边等基准点或基准线位于贯穿孔151内。

70.通过以上的工序,则完成了能够将半导体芯片搭载于粘贴在芯片垫150的胶带160上的引线框架100的制作。由于芯片垫150中的半导体芯片的位置取决于胶带160的位置,因此胶带160需要被粘贴在适当的位置上。由于通过上述工序制造的引线框架100的芯片垫150上形成有贯穿孔151,因此能够高效地检查胶带160是否被粘贴在适当的位置上。

71.图9是表示引线框架100的检查方法的流程图。引线框架100的检查例如通过具备光源、光传感器及图像处理装置的检查装置来执行。

72.在芯片垫150上粘贴有胶带160的引线框架100制作完成后,从光源向引线框架100照射穿过贯穿孔151的透射光(步骤s201)。即,光传感器隔着引线框架100被配置在光源的相反侧,来自光源的光被框体110、引脚120、支承杆130、连筋140及芯片垫150遮挡,而仅从包含芯片垫150的贯穿孔151在内的空隙部分穿过。然后,通过光传感器能够检测到穿过引线框架100的空隙部分的透射光。在光传感器检测到透射光后,生成表示遮挡了光的区域和穿过了光的区域的二值图像(步骤s202)。

73.然后,在二值图像中确定与芯片垫150的贯穿孔151对应的区域,并在该区域内检测胶带160的基准点或基准线的坐标。具体而言,在二值图像的对应贯穿孔151的区域中确定被胶带160遮挡了光的区域,从而检测到与该胶带160对应的区域的预设顶点或预设边等的坐标。像这样,只要胶带160的基准点或基准线位于贯穿孔151内,则能够在二值图像中检测到胶带160的基准点或基准线的坐标。然后,对检测到的基准点或基准线的坐标是否包含于与胶带160的适当粘贴位置对应的预设范围内进行判断(步骤s203)。即,对基准点或基准线是否位于以可容许的误差粘贴胶带160时的范围内进行判断。

74.作为该判断的结果,当胶带160的基准点或基准线在预设范围内时(步骤s203:是),判定胶带160被粘贴于适当的位置(步骤s204)。另一方面,当胶带160的基准点或基准线不在预设范围内时(步骤s203:否),判定胶带160未被粘贴于适当的位置(步骤s205)。

75.具体而言,例如如图10(a)所示,在二值图像中,贯穿孔151区域内的一部分是与遮挡了光的胶带160对应的区域,在作为胶带160的基准点的顶点160a的坐标包含于预设范围内的情况下,判定胶带160的位置适当。另一方面,即使作为胶带160的基准点的顶点160a包含于贯穿孔151的区域内,在顶点160a的坐标不包含于预设范围内的情况下,判定胶带160的位置不正常。此外,例如如图10(b)所示,在二值图像中,贯穿孔151的全部区域为被光穿过的区域时,作为胶带160的基准点的顶点160a不包含于贯穿孔151的区域内,因此判定胶带160的位置不正常。进一步地,在二值图像中贯穿孔151的全部区域为遮挡了光的区域的情况下,由于作为胶带160的基准点的顶点160a不包含于贯穿孔151的区域内,因此也判定胶带160的位置不正常。

76.像这样,通过使贯穿孔151形成于,包含被粘贴在芯片垫150中的适当位置的胶带160的外周一部分的区域,则能够使用透射光来检测胶带160的基准点或基准线的坐标,从而能够检查胶带160是否被粘贴于适当的位置。

77.接下来,参照图11所示的流程图对使用引线框架100构成的半导体装置的制造方法进行说明。用于制造半导体装置的引线框架100为,通过上述的检查,被判定为胶带160已粘贴于芯片垫150的适当的位置的引线框架。

78.将半导体芯片搭载于引线框架100的芯片垫150上(步骤s301)。具体而言,例如如图12所示,将半导体芯片210粘接于胶带160的位置上。此外,在芯片垫150上,除了通过胶带160粘接的半导体芯片210,例如还可以搭载通过焊料或芯片粘贴膏等接合的半导体芯片215。

79.通过胶带160粘接的半导体芯片210的大小为在俯视视角下收纳在胶带160的范围内的大小,半导体芯片210的整个面与胶带160粘接。此时,例如如图13(a)所示,在胶带160是由一层的粘接层161形成的情况下,半导体芯片210直接被粘接在粘接层161上。此外,例如如图13(b)所示,在胶带160为粘接层161及基材层162的双层结构的情况下,基材层162的

表面形成有粘接层211,而半导体芯片210被粘接在粘接层211上。并且,例如如图13(c)所示,在胶带160为粘接层161、基材层162及粘接层163的三层结构的情况下,半导体芯片210被粘接在粘接层163上。

80.在将半导体芯片210搭载在芯片垫150上后,通过引线键合将引脚120与半导体芯片210电气连接(步骤s302)。此外,在芯片垫150上搭载有多个半导体芯片210、215的情况下,各个半导体芯片210、215之间可以通过引线键合连接。具体而言,例如如图14所示,内引脚121的镀层125与半导体芯片210的端子通过金属丝220连接。此外,相邻的半导体芯片210、215的端子之间也通过金属丝220来连接。

81.然后,例如使用环氧树脂等模塑树脂将半导体芯片210、215封装(步骤s303)。具体而言,搭载有半导体芯片210、215的芯片垫150、内引脚121及支承杆130例如被图15中虚线所示的范围内的模塑树脂230封装。

82.在将半导体芯片210、215树脂封装后,将引脚120及支承杆130从框体110切开,并且将连接相邻的引脚120之间的连筋140切断。由此,得到分割成单片的半导体装置,制成使用了引线框架100的半导体装置(步骤s304)。该半导体装置例如如图16所示,具有外引脚122向模塑树脂230的外侧突出的形状。这些外引脚122成为与外部连接的端子。

83.如上所述,根据本实施方式,在引线框架的芯片垫上粘贴有用于粘接半导体芯片的胶带,并在包含被粘贴在适当的位置时的胶带的外周一部分的区域,形成有贯穿芯片垫的贯穿孔。因此,通过使用透射光的检查,能够对胶带的外周的位置是否适当进行判断,从而能够检查胶带是否被粘贴在芯片垫的适当的位置上。其结果,能够使引线框架中的胶带的位置适当,从而防止通过胶带粘接的半导体芯片的位置精准度的下降。

84.此外,在上述的一实施方式中,例举了用于外引脚122向模塑树脂230的外侧突出的qfp(quad flat package:方形扁平封装)的引线框架100的示例进行说明,但本发明不限于此。与上述一实施方式一样具有贯穿孔的芯片垫也能够适用于,例如qfn(quad flat non-leaded package:方形扁平无引脚封装)等的各种半导体装置的引线框架。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1